雷達(dá)數(shù)字化收發(fā)系統(tǒng)芯片設(shè)計與實現(xiàn)?

(中國電子科技集團(tuán)公司第三十八研究所,安徽合肥230088)

0 引言

數(shù)字陣列雷達(dá)是一種接收波束和發(fā)射波束都采用數(shù)字波束形成技術(shù)實現(xiàn)的有源相控陣?yán)走_(dá),由于數(shù)字陣列雷達(dá)具有瞬時動態(tài)大、波束掃描靈活、抗干擾能力強(qiáng)等特點,因此數(shù)字陣列雷達(dá)正成為未來有源相控陣?yán)走_(dá)發(fā)展的重要方向之一[1-3]。數(shù)字陣列雷達(dá)的核心模塊是數(shù)字T/R組件,數(shù)字T/R組件是集數(shù)字波形產(chǎn)生、模擬變頻放大、大功率放大、低噪聲接收、模數(shù)轉(zhuǎn)換和數(shù)字解調(diào)等功能于一體的多功能模塊,實現(xiàn)雷達(dá)信號的接收和發(fā)射功能。數(shù)字T/R組件是組成數(shù)字陣列雷達(dá)的基本單元,通過將成千上萬個數(shù)字T/R組件進(jìn)行集成設(shè)計構(gòu)成數(shù)字陣列雷達(dá)的有源天線陣面,因而數(shù)字T/R組件的性能指標(biāo)、成本、體積和重量將決定數(shù)字陣列雷達(dá)的使用價值和生存周期[4-5]。

隨著數(shù)字陣列雷達(dá)技術(shù)推廣應(yīng)用到機(jī)載、艦載、球載和星載等平臺上。高集成、輕量化及低功耗的數(shù)字T/R組件設(shè)計是未來的發(fā)展趨勢,本文提出一種基于微系統(tǒng)封裝(SIP)技術(shù)的數(shù)字T/R組件設(shè)計和實現(xiàn)方法,即將微波收發(fā)芯片、變頻芯片和模數(shù)混合收發(fā)芯片一起集成在一個IC封裝內(nèi),形成一個微波數(shù)字混合的收發(fā)系統(tǒng)芯片,實現(xiàn)數(shù)字陣列雷達(dá)單元級數(shù)字接收和數(shù)字發(fā)射功能。采用該技術(shù)將極大地降低數(shù)字T/R組件的體積、重量和功耗,由于實現(xiàn)了芯片化,因此也可以提高批產(chǎn)一致性和可靠性。它能以極小的體積、功耗和成本來支撐大規(guī)模的應(yīng)用,同時降低有效載荷體積重量,直接提高其生存能力。

1 系統(tǒng)組成

系統(tǒng)芯片由驅(qū)動功放MMIC、限幅器MMIC、射頻收發(fā)MMIC、中頻收發(fā)MMIC和模數(shù)混合芯片等組成,其組成框圖如圖1所示。

圖1 系統(tǒng)芯片組成框圖

在圖1所示的系統(tǒng)芯片組成框圖中,為了提高系統(tǒng)芯片的通用性,在方案設(shè)計時考慮將鏈路中的濾波器外置,同時為進(jìn)一步提高系統(tǒng)芯片集成度,這里創(chuàng)新性地采用有源變頻方式實現(xiàn)收發(fā)鏈路的兩次上下變頻。射頻收發(fā) MMIC(包含低噪放、收發(fā)開關(guān)和一中上下變頻)是基于Ga As工藝,對雷達(dá)回波信號進(jìn)行低噪放和一中下變頻,對二中激勵信號進(jìn)行一中上變頻;中頻收發(fā)MMIC(包含收發(fā)開關(guān)和二中上下變頻)是基于Si工藝,主要完成二中上下變頻功能;模數(shù)混合芯片(包含ADC、DAC、數(shù)字下變頻、數(shù)字波形產(chǎn)生、控制接口、RAM和ROM)是基于CMOS工藝,對中頻輸入信號進(jìn)行數(shù)字接收,輸出數(shù)字基帶I/Q信號,同時根據(jù)信號帶寬和中頻要求,數(shù)字直接產(chǎn)生相應(yīng)的LFM信號。

2 技術(shù)指標(biāo)

系統(tǒng)芯片采用集成化、一體化設(shè)計方式,在單封裝芯片中實現(xiàn)雷達(dá)收發(fā)系統(tǒng)功能,其主要性能指標(biāo)為:

工作頻率:S波段;

工作帶寬:300 MHz;

瞬時帶寬:5 MHz;

噪聲系數(shù):≤2.5 dB;

動態(tài)范圍:≥60 d B;

輸出功率:≥20 d Bm;

帶內(nèi)起伏:≤±1 dB;

輸出數(shù)據(jù)率:≥20 Mbit/s。

3 電路設(shè)計

3.1 寬帶低噪聲放大器設(shè)計

系統(tǒng)芯片工作頻段為S波段,相對帶寬約為30%,系統(tǒng)對低噪聲放大器噪聲系數(shù)要求低,增益起伏要求小,在設(shè)計中從以下幾方面進(jìn)行了考慮:

(1)匹配電路設(shè)計

作為低噪聲電路,輸入電路的匹配效果直接影響整個電路的噪聲性能。為了電路噪聲性能及輸入駐波指標(biāo)的均衡考慮,必須仔細(xì)選擇輸入匹配點。為了增加第一級FET的穩(wěn)定性及取得噪聲與駐波指標(biāo),在源級增加了一個電感量較小的串聯(lián)負(fù)反饋,使FET的穩(wěn)定性有了很大提高,簡化了匹配電路的復(fù)雜性。選擇寬帶內(nèi)的一個工作點來設(shè)計匹配電路,在匹配電路拓?fù)涞拇_定中還需充分考慮到電路的寬帶特性,力爭使整個網(wǎng)絡(luò)的Q值不超過1。第二級FET的作用主要是放大、寬帶匹配及輸出能力考慮,為了提高寬帶特性,該級反饋采用的是電阻并聯(lián)負(fù)反饋電路,可以提高第二級FET穩(wěn)定性至完全穩(wěn)定狀態(tài)。該級FET輸入輸出采用共扼匹配,保證了輸出駐波的良好特性。

(2)仿真設(shè)計

根據(jù)電路的拓?fù)浣Y(jié)構(gòu)將UMS的有源、無源模型放入原理圖中,仿真優(yōu)化后達(dá)到的結(jié)果如圖2所示。可以看出噪聲系數(shù)指標(biāo)略差,這是由于電感在該頻段的Q值略低,造成了物理損耗過大,在實際的應(yīng)用中可以將FET的工作電流降低,達(dá)到降低噪聲系數(shù)的目的,這里可以近似得到電流降低后的仿真噪聲結(jié)果。寬帶放大器設(shè)計中難以達(dá)到的指標(biāo)為寬帶增益起伏,選擇的設(shè)計目標(biāo)為帶內(nèi)起伏1 dB,根據(jù)經(jīng)驗將工作頻率偏移6%~7%,帶寬也略放寬。從分析仿真的結(jié)果可以看出,很難達(dá)到帶寬與輸入/輸出駐波的完全滿足,只能在寬帶的帶內(nèi)起伏與駐波之間找到一個均衡點,使其基本能夠滿足系統(tǒng)對該部分電路的要求。采用的關(guān)鍵技術(shù)主要是用串聯(lián)及并聯(lián)負(fù)反饋技術(shù)來擴(kuò)展頻帶,第一級采用串聯(lián)負(fù)反饋技術(shù),第二級采用串聯(lián)+并聯(lián)負(fù)反饋技術(shù),從仿真的結(jié)果看完全達(dá)到了設(shè)計要求。

圖2 電感模型比較

(3)模型庫的修正

在UMS的元件模型中,并不是所有的模型都能夠滿足電路的需求,為滿足電路拓?fù)?用ADS的MOMENT設(shè)計工具自制了一個電感,將MOMENT的仿真結(jié)果作為黑匣子放入電路中,得到了完整電路的仿真結(jié)果。同時將MOMENT的仿真結(jié)果與ADS的模型結(jié)果相比較,可以看出在該頻段ADS的模型是比較準(zhǔn)確的。

(4)版圖設(shè)計

MMIC設(shè)計中一個重要的環(huán)節(jié)是版圖設(shè)計,不僅要保證Layout的圖形能夠達(dá)到原理圖的仿真結(jié)果,而且要有效利用Ga As材料的有效面積。完全利用UMS現(xiàn)有的模型Layout不可能有效利用面積,所以對于對電路性能影響不大的旁路電容可以依據(jù)Designer Ruler畫出。芯片版圖設(shè)計時,要嚴(yán)格按照FOUDRY廠家工藝規(guī)范和要求設(shè)計。寬帶低噪聲放大器電原理圖和版圖如圖3所示。

圖3 寬帶低噪聲放大器電原理圖和版圖

3.2 寬帶有源混頻器設(shè)計

系統(tǒng)芯片接收采用的是超外差工作方式,前端的混頻器工作頻帶與低噪聲放大器相同,也面臨著寬帶與高技術(shù)指標(biāo)的問題。設(shè)計中采用在本振端增加有源FET來提高整個頻帶內(nèi)RF端口與LO端口的隔離度,這樣帶來的缺陷就是增加了芯片的面積及功耗;同時在RF端與LO端增加諧振回路,提高整個頻帶內(nèi)的駐波技術(shù)指標(biāo)。

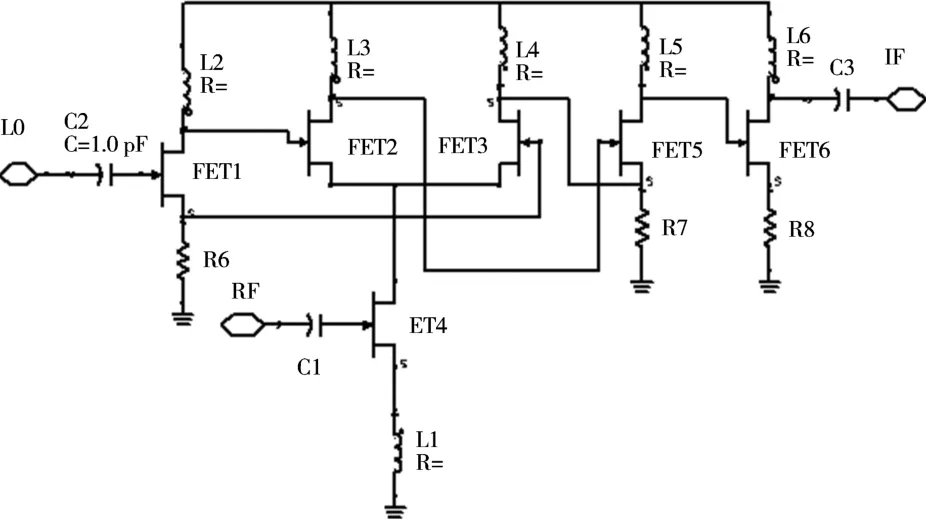

在有源混頻放大器電路設(shè)計中,變頻部分選用了Gilbert雙平衡結(jié)構(gòu),混頻電路原理圖如圖4所示。

圖4 混頻器的結(jié)構(gòu)

本振信號Vo(t)=Vocosωo(t)首先加到FET1的柵極,并加在差分對FET2和FET3的柵極。射頻信號VS(t)=VScosωS(t)加在恒流FET4的柵極,使總電流隨ωS周期性的變化。因此,差分對管可以看成一個參數(shù)(跨導(dǎo))變化的線性電路。經(jīng)過非線性變換,差分對管的輸出分別加在FET5的柵極和源級,信號在FET5的漏級反向疊加,濾除其他頻率分量,輸出差頻(中頻)信號。因此,差分對管混頻器在管子完全相同、輸入信號完全對稱的情況下,輸出端主要是差頻ωO-ωS項,不包括射頻頻率ωS及其諧波,不包括本振頻率ωO的偶次諧波,也不包括本振的偶次方與射頻的相乘項所引起的組合頻率。所以,差分對混頻器大大減少了組合頻率干擾,提高了隔離度。在芯片版圖設(shè)計時,充分考慮微波的傳輸特性,分布參數(shù)影響和實際使用的情況。主要措施為:在不同線寬的微帶線連接時,加入漸進(jìn)線模型,以減小信號反射;通過合理安排器件的位置,以減小分布參數(shù)影響,提高設(shè)計效率;在設(shè)計中加入鍵合金絲和焊盤的模型,更準(zhǔn)確地仿真實際情況。圖5為寬帶混頻器芯片實物圖,其主要指標(biāo)為:增益大于15 d B,噪聲系數(shù)小于10 dB,本振與中頻隔離度大于30 dB。

圖5 寬帶有源混頻器芯片實物圖

3.3 模數(shù)混合芯片設(shè)計

在系統(tǒng)芯片中,模數(shù)混合芯片主要完成兩個功能:對中頻回波信號進(jìn)行模數(shù)轉(zhuǎn)換、I/Q數(shù)字變換和頻譜搬移,輸出基帶I/Q信號;根據(jù)載頻、帶寬和時寬要求產(chǎn)生相應(yīng)數(shù)字LFM或NLFM信號后進(jìn)行數(shù)模轉(zhuǎn)換,輸出中頻激勵信號,其功能框圖如圖6所示。

根據(jù)Foundry工藝分類,模數(shù)混合芯片由5個功能模塊電路組成:模數(shù)轉(zhuǎn)換(A/D)、數(shù)模轉(zhuǎn)換(D/A)、數(shù)字下變頻(DDC)、數(shù)字波形產(chǎn)生(DDS)和控制接口,整個模數(shù)混合芯片采用0.18μm CMOS工藝進(jìn)行設(shè)計。

圖6 模數(shù)混合芯片功能框圖

模數(shù)混合SOC芯片中的模擬電路部分包括數(shù)字下變頻器(DDC)前端的AD轉(zhuǎn)換器,以及直接數(shù)字頻率合成器(DDS)輸出后端的DA轉(zhuǎn)換器兩部分,這兩部分采用現(xiàn)有的IP核。

數(shù)字下變頻器DDC的主要目的是實現(xiàn)中頻信號到正交基帶信號的變換。數(shù)字下變頻器的實現(xiàn)結(jié)構(gòu)采用傳統(tǒng)的、類似現(xiàn)有ASIC芯片普遍采用的結(jié)構(gòu):NCO+數(shù)字混頻+CIC濾波器/HB濾波器+FIR濾波器結(jié)構(gòu)。

直接數(shù)字合成器DDS是從相位的概念出發(fā)直接合成所需波形的一種新的頻率合成技術(shù),它在相對帶寬、頻率轉(zhuǎn)換時間、相位連續(xù)性、正交輸出、高的頻率分辨率以及集成化方面都遠(yuǎn)遠(yuǎn)超過傳統(tǒng)的頻率合成技術(shù)。

控制接口單元負(fù)責(zé)DDC和DDS模塊的參數(shù)配置。由于DDC和DDS分屬于兩個獨(dú)立的時鐘域,因此使用了兩片1 024×16 bit的雙口SDRAM,用地址線的第一位作為片選信號。該控制接口具有參數(shù)回讀功能,可將SDRAM中的參數(shù)讀出到輸入輸出復(fù)用的數(shù)據(jù)線上。

版圖設(shè)計:高頻數(shù)字部分與模擬部分分開布局、高頻數(shù)字部分屏蔽、模擬與數(shù)字部分電源和地分開布線設(shè)計,同時進(jìn)行閉鎖設(shè)計和抗電應(yīng)力可靠性設(shè)計。芯片封裝形式為LQFP128,其總體版圖及pin腳如圖7所示,裸芯片尺寸4 mm×3 mm。

3.4 一體化封裝殼體設(shè)計

系統(tǒng)芯片采用多層板結(jié)構(gòu),將芯片和器件裝到多層基板上并用金絲進(jìn)行互連,在陶瓷板底部做CBGA焊球,并在陶瓷板上作金屬外框一體化封裝。雷達(dá)收發(fā)系統(tǒng)芯片如圖8所示。

圖7 模數(shù)混合芯片版圖和引腳定義

圖8 系統(tǒng)芯片一體化封裝殼體實物

為了避免封裝殼體產(chǎn)生腔體效應(yīng)引起電路自激,保證微波電路穩(wěn)定工作,利用電磁場分析軟件HFSS對管殼進(jìn)行了模擬和分析,使得金屬盒體的自諧振頻率與工作頻率距離甚遠(yuǎn),仿真結(jié)果如圖9所示。

圖9 一體化封裝管殼自諧振頻率

系統(tǒng)芯片采用一體化封裝設(shè)計,I/O的引出端采用CBGA焊球,CBGA具有共面性好、阻抗匹配好、互連密度高及氣密性好等優(yōu)點[6-7],其組成如圖10所示,包括LTCC基板(系統(tǒng)芯片襯底)、CBGA球形引出端、封裝外殼腔壁和金屬蓋板等。

LTCC基板制造時,將電學(xué)I/O端就近通過金屬化孔從基板底面以標(biāo)準(zhǔn)節(jié)距呈矩陣排列的外引線金屬化焊盤引出,在基板的頂面網(wǎng)印制作出金屬封裝腔壁的金屬化焊區(qū)。通過釬焊(Brazing)工藝,用合金材料在基板底面的中I/O端子焊盤內(nèi)焊接上或制作出焊球凸點,形成標(biāo)準(zhǔn)CBGA端子,在基板頂面的焊區(qū)中焊接上柯伐封裝腔體側(cè)壁。

系統(tǒng)芯片的封裝使用頻率為S波段,封裝管殼的電設(shè)計(如阻抗設(shè)計等)是決定系統(tǒng)性能的關(guān)鍵。

圖10 一體化封裝管殼結(jié)構(gòu)示意圖

從焊球到芯片焊點的整個信號通道中,CBGA焊球垂直過渡結(jié)構(gòu)的傳輸損耗將直接決定雷達(dá)收發(fā)系統(tǒng)芯片封裝的微波性能。對于襯底傳輸損耗控制技術(shù)主要指微波傳輸線理論模型設(shè)計、仿真和優(yōu)化技術(shù)。

系統(tǒng)芯片的封裝管殼引腳建模重點考慮封裝襯底的微波互連傳輸結(jié)構(gòu)建模。CBGA封裝襯底微波互連傳輸結(jié)構(gòu)模型為“微帶線→傳輸通孔→BGA焊球→微帶線”所構(gòu)成的三維垂直互連傳輸模型。由于互連結(jié)構(gòu)復(fù)雜,會用到較多通孔,這是建模的一項重要工作,尤其受工藝標(biāo)準(zhǔn)限制時,在高頻段往往因為通孔不合適和焊球尺寸不合適而造成整個系統(tǒng)芯片性能的惡化。因此需要建立通孔模型來保證各裸芯片的微波互連。

焊球、過孔及其環(huán)狀焊盤的大小根據(jù)需要進(jìn)行設(shè)計,通過仿真優(yōu)化,使得通孔的大小及進(jìn)行表面匹配阻抗后其在相當(dāng)寬的頻率范圍內(nèi)傳輸損耗及回波損耗最小。利用Ansoft公司的高頻電磁場仿真軟件HFSS對LTCC上的“微帶—VIA”垂直過渡進(jìn)行建模并改進(jìn)。在表層微帶過渡點附近作射頻接地并加入同軸補(bǔ)償,模型和仿真結(jié)果如圖11和圖12所示。

通過對“微帶—BGA焊球—VIA—微帶”垂直過渡的建模仿真和優(yōu)化,可以得到垂直過渡結(jié)構(gòu)的各項尺寸,從而在所需頻段之內(nèi),采用BGA封裝可以獲得較好的微波信號傳輸特性和駐波特性。

圖11 BGA封裝引腳過渡模型

圖12 引腳過渡傳輸特性與駐波特性仿真圖

4 測試結(jié)果

雷達(dá)數(shù)字化收發(fā)系統(tǒng)芯片通過方案論證后,完成設(shè)計投產(chǎn),調(diào)試后裝配到某S波段數(shù)字陣列模塊中,隨數(shù)字陣列模塊一起完成聯(lián)試和環(huán)境實驗,并通過專家組的測試驗收。經(jīng)測試,雷達(dá)數(shù)字化收發(fā)系統(tǒng)芯片達(dá)到設(shè)計要求,部分測試結(jié)果如圖13所示。

圖13 系統(tǒng)芯片部分測試結(jié)果圖

5 結(jié)束語

本文提出了一種雷達(dá)數(shù)字化收發(fā)系統(tǒng)芯片設(shè)計和實現(xiàn)方法,即在單基板和單封裝中,將具有自主知識產(chǎn)權(quán)的微波、數(shù)字芯片混合集成設(shè)計,形成了一種小型化、集成化、一致性好的雷達(dá)專用收發(fā)系統(tǒng)芯片。測試結(jié)果滿足設(shè)計要求。該系統(tǒng)芯片應(yīng)用在某數(shù)字陣列雷達(dá)試驗系統(tǒng)中,極大地簡化了雷達(dá)系統(tǒng)的工程設(shè)計復(fù)雜度,達(dá)到了滿意效果。

[1]張明友.數(shù)字陣列雷達(dá)和軟件化雷達(dá)[M].北京:電子工業(yè)出版社,2008:361-363.

[2]馬曉峰,秦思,盛衛(wèi)星,等.X波段數(shù)字陣列雷達(dá)的數(shù)字收發(fā)模塊研制[J].南京理工大學(xué)學(xué)報,2013,37(4):457-462.

[3]CHAPPELL W,FULTON C.Digital Array Radar Panel Development[C]∥IEEE International Symposium on Phased Array Systems and Technology,Waltham,MA:IEEE,2010:50-60.

[4]方立軍,李佩,馬駿,等.基于微波光電技術(shù)的未來數(shù)字陣列構(gòu)想[J].雷達(dá)科學(xué)與技術(shù),2013,11(6):583-586.

FANG Lijun,LI Pei,MA Jun,et al.An Idea for Future Digital Array Radar Based on Microwave Optoelectronics[J].Radar Science and Technology,2013,11(6):583-586.(in Chinese)

[5]吳曼青,王炎,靳學(xué)明.收發(fā)全數(shù)字波束形成相控陣?yán)走_(dá)關(guān)鍵技術(shù)研究[J].系統(tǒng)工程與電子技術(shù),2001,23(4):45-47,60.

[6]孫軼,何睿,班玉寶,等.陶瓷焊球陣列封裝可靠性研究與試驗分析[J].航空科學(xué)技術(shù),2014,25(8):87-90.

[7]郭影.CBGA器件組裝工藝和焊接方法[J].印制電路信息,2015(5):51-54.