基于FPGA和gamma校正的視頻監控系統設計與實現

劉冰,徐文濤

(南京航空航天大學理學院,江蘇南京211100)

?

基于FPGA和gamma校正的視頻監控系統設計與實現

劉冰,徐文濤

(南京航空航天大學理學院,江蘇南京211100)

摘要:本文針對視頻監控系統實時處理速度瓶頸和視頻監控圖像失真等問題,提出一種基于FPGA和gamma校正的視頻監控系統解決方案,充分利用FPGA并行數據處理的優勢,很好地滿足了視頻監控系統實時性和高清晰度的要求;并采用查找表(LUT)的方法實現快速gamma校正,解決了由顯示器亮度非線性輸出所導致的視頻失真問題。實驗結果顯示視頻監控系統運行穩定,圖像清晰度高,且經gamma校正后,暗場灰階的顯示明顯改善,細節分明,很好地解決了失真的問題。

關鍵詞:視頻監控;FPGA;gamma校正;圖像失真;查找表

隨著視頻處理技術的不斷發展,視頻監控系統在生活中得到了廣泛的應用,同時用戶對視頻監控技術的實時性、穩定性和清晰度也提出了更高的要求。以往基于CPU/DSP的視頻監控系統,以程序順序執行的方式對視頻進行采集和處理,限制了視頻監控系統的處理速度,不能滿足實時性和高清晰度的要求。近些年基于FPGA的數字系統設計得到了迅速的發展,FPGA并行處理能力強[1-2],設計靈活,集成度高,在視頻處理方面有巨大的優勢,可以滿足現今對視頻監控的要求[3]。

在監控系統中,由于顯示器輸出亮度與輸入電壓不成正比,如果不對數字視頻信號進行處理,則會導致圖像的失真,影響視頻監控質量。對顯示器的非線性修正,常常被稱為gamma校正[4-6]。

本文基于FPGA設計并實現了一種視頻監控系統,在FPGA中,集成了視頻數據的采集、解碼、顏色空間轉換等功能模塊,并用FPGA實現了gamma校正,能夠通過Verj1og程序對gamma值進行修改,適配不同gamma參數的顯示器,該校正方法可以簡化電路結構,不需要單獨的RAM單元,能夠解決圖像失真的問題。實驗結果表明,該系統可以滿足視頻監控系統對清晰度和實時性的要求。

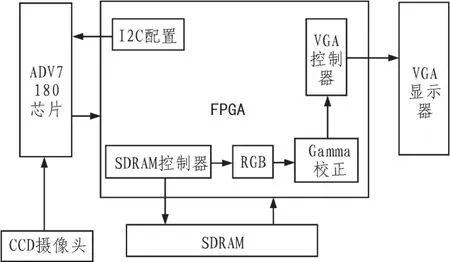

1 視頻監控系統總體框架

本系統通過CCD攝像頭捕捉到PAL格式的模擬視頻信號,然后通過ADV7180芯片將其轉換為YUV4:2:2數字視頻數據。在FPGA中完成對視頻信號的處理,通過解碼、插值、解交織等過程,將YUV4:2:2轉換成YUV4:4:4,,再將其轉換成RGB格式。再此過程中需要對數據進行緩存,緩存模塊使用SDRAM。在視頻信號通過gamma校正模塊校正后,由VGA顯示器進行顯示。系統構成如圖1所示。

2 ADV7180視頻解碼

視頻解碼芯片ADV7180是一種能將NTSC、PAL等標準模擬視頻信號轉換為符合ITU-R BT.656標準的數字視頻數據的綜合視頻解碼器。在本系統中,FPGA通過I2C總線對

圖1 視頻監控系統系統構成圖

ADV7180的寄存器進行配置,配置完成后,芯片對通過CCD攝像頭輸入的模擬視頻進行視頻解碼,輸出符合ITU-R BT. 656標準的YCrCb4:2:2視頻數據。

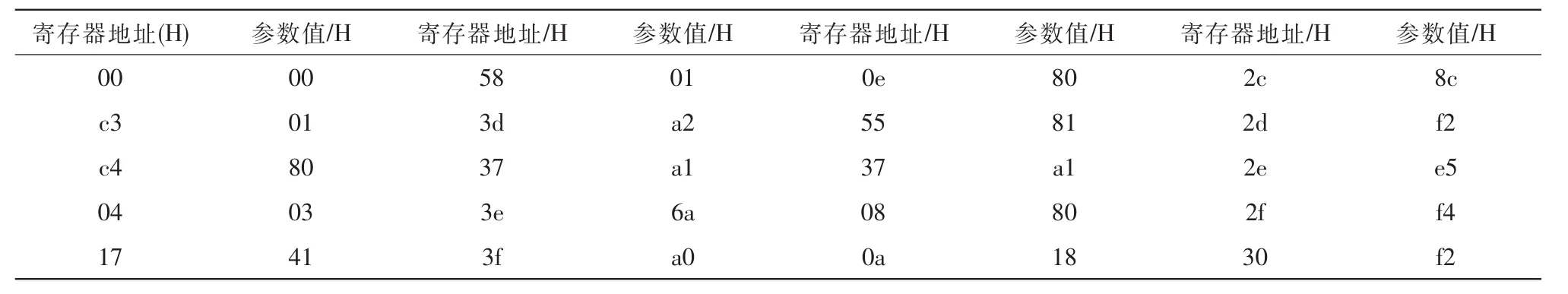

完成對ADV7180的初始化要通過對ADV7180的寄存器進行配置。在FPGA中設計一個I2C總線配置模塊,將要配置的寄存器數據存儲在I2C的查找表中,通過調用該模塊,完成對ADV7180的配置。寄存器的地址和配置參數值如表1所示。

3 基于FPGA的視頻數據處理

視頻采集芯片ADV7180輸出的視頻信息為串行的YCrCb4:2:2格式數據,但是這一格式的數據并不能在VGA顯示器上顯示,要進一步對此視頻數據進行處理,最終轉換為RGB格式才能滿足VGA顯示的要求。本文在FPGA上設計并實現了數據轉換模塊,該模塊具有ITU-R BT.656解碼、隔行掃描轉逐行掃描、顏色空間變化3個功能。

表1 寄存器地址和參數值

3.1ITU-R BT.656解碼

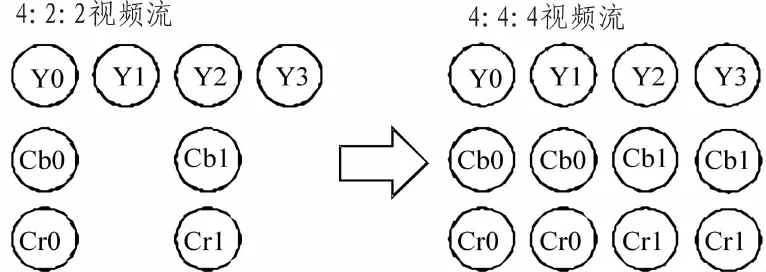

ITU-R BT.656解碼工作將串行的YCrCb4:2:2視頻數據轉換為并行數據,并對YCrCb4:2:2視頻數據進行插值,使其轉換為YCrCb4:4:4格式。

圖2 YCrCb4:2:2視頻流轉換為YCrCb4:4:4示意圖

如圖2所示,YCrCb4:2:2格式即水平方向上每兩個點采樣色差信號Cr、Cb,每一個點采樣亮度信號Y,數據順序為Cb0 Y0 Cr0 Y1 Cb1 Y2 Cr1 Y3……。當有效視頻起始標志到來后,FPGA中的解碼模塊對視頻數據進行讀入,并將Cb、Cr各復用一次,數據格式轉變為Cb0 Y0 Cr0 Cb0 Y1 Cr0 Cb1 Y2 Cr1 Cb1 Y3 Cr1……,即可完成從數據格式YCrCb4:2:2到格式YCrCb4:4:4的轉換。

3.2隔行掃描轉逐行掃描

PAL制式對視頻的掃描方式是隔行掃描的,但是VGA對視頻的掃描方式是逐行掃描的。將YCrCb4:2:2為YCrCb4:4:4視頻數據轉換之后,還需要將隔行掃描數據轉換為逐行掃描數據。本系統通過3個FIFO便可完成隔行掃描轉逐行掃描的操作,,無需設計專門的功能電路,優化了系統結構,節約了系統資源。

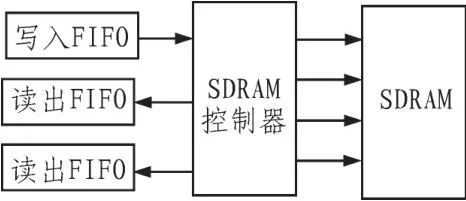

SDRAM控制模塊如圖3所示,其中包含了3個FIFO和 SDRAM控制器。

圖3 隔行掃描轉逐行掃描示意圖

YCrCb4:4:4視頻數據寫入SDRAM時是隔行寫入的,其占用的地址空間為0-640*585,其中每一行的前24個數據為起始標志,然后依順序方式依次寫入奇數場和偶數場數據。從SDRAM中640x24地址到640x294地址取奇數場的270行數據,從640x315地址到640x585地址取偶數場的270行數據,當從SDRAM讀出視頻數據時,由兩個讀出FIFO交替讀出奇數場和偶數場的數據,這樣的讀取的方法最終實現了隔行掃描轉換為逐行掃描的目的。

3.3顏色空間變化(YCrCb->RGB)

ITU-R BT.656解碼后的視頻格式為YCrCb4:4:4,并且每個像素的Y、CB、Cr都是獨立的,顏色空間變換就是從YCrCb顏色空間變換到RGB顏色空間,得到像素的RGB值。

YCbCr到RBG空間的變換公式為:

R=1.164(Y-16)+1.59(Cr-128)

G=1.164(Y-16)-0.391(Cb-128)-0.813(Cr-128)

B=1.164(Y-16)+2.018(Cb-128)

用Verj1og編程時,因為以上公式涉及到小數,若直接運用,編譯過程中會在ISE綜合時報錯。因此使用FPGA處理浮點運算時,一般采取放大的方法,先將公式放大512倍得:

R-jnt=512*R=596Y+817Cr-114131

G-jnt=512*G=596Y-200Cb-416Cr+69370

B-jnt=512*B=596Y+1033Cb-141787

計算出R-jnt、G-jnt和B-jnt等之后,均除以512(右移9位),即得到RGB的值。

4 gamma校正

4.1gamma校正原理

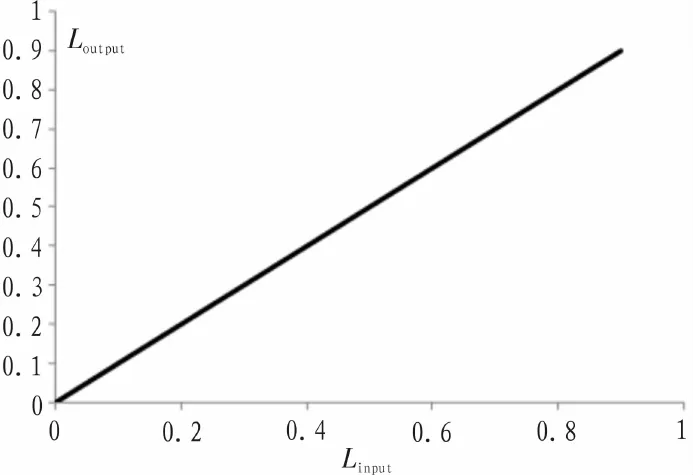

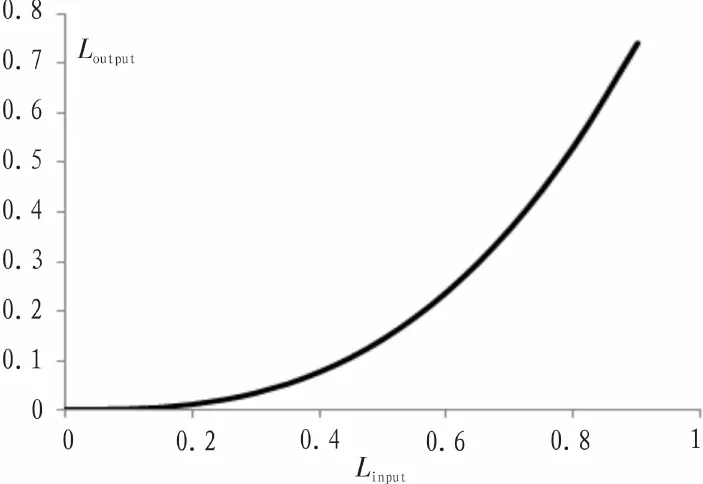

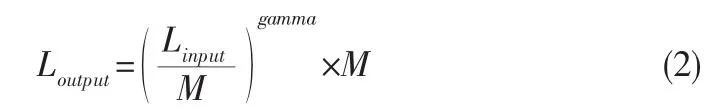

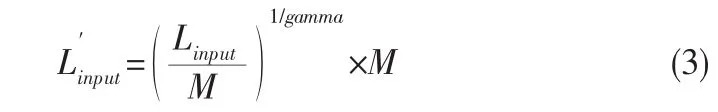

對于理想的顯示系統,顯示信號的電壓與顯示器亮度應為線性關系,如圖4所示。但是由于顯示器紅藍綠3色的光電特性不同,導致顯示系統的響應曲線是非線性的,輸入信號與輸出信號關系如圖5所示,輸入與輸出之間呈現以gamma為參數的指數關系。當Gamma值=1的時候,曲線為正比例函數,這個時候輸出值等于輸入值,為理想系統。當Gamma值>1時,圖像變暗;而當Gamma值<1時,圖像變亮。一般VGA顯示器的gamma值為2.8,導致輸出亮度變暗。通過反效果補償的方法解決顯示器非線性失真問題。理想狀態下要達到的效果為:其中Loutput為顯示器最終輸出的值,Linput為輸入顯示器的值。顯示器的亮度相應曲線為:

圖4 理想顯示系統輸入輸出關系

圖5 實際顯示系統輸入輸出關系

其中M為總的色階數。

采用反效果補償法,在數據輸出顯示器之前,先對數據做補償處理,設補償后數據為L′input,則有:將L′input輸入顯示器后,最終得到:

最終達到和式(1)相同的結果,從而實現gamma值的補償,這就是gamma校正的原理。

4.2gamma校正FPGA實現

如果對每個像素點都執行上述的指數運算,那樣運算量十分龐大。我們采取查找表(LUT)的方法實現gamma值的快速校正。

顏色空間變換之后,得到RGB信號均為8位256色,在給定gamma值的情況下,對0-255進行(3)式的計算,得到的值就可以制作為查找表,對于不同的像素值只需通過對表的查找就可以完成校正,這樣的方法極大的提高了運算效率。具體的操作為打開quarters II軟件,新建一個.mjf文件,將得到的(3)式的結果導入到.mjf中。隨后創建一個RAM,并將前面的mjf文件導入到RAM中。

quarters II自帶工具即可創建RAM模塊,這樣省去了復雜的編程過程,實現了快速方便的gamma校正。

5 VGA

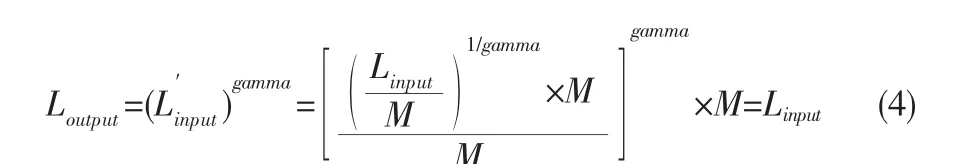

經過FPGA處理過的數字視頻數據通過VGA接口控制模塊在VGA顯示器中進行顯示。本系統使用的VGA顯示器的分辨率為800*600,刷新頻率為60 MHz。VGA時序中,行同步信號包括消隱信號區和有效視頻信號區[7-8]。其中有效視頻信號區為要顯示的視頻信號,共800個時鐘周期,當行同步信號到達有效視頻信號區時,每個時鐘周期應攜帶RGB信息。消隱信號區包括同步脈沖、顯示后沿和顯示前沿,時鐘周期數分別128、88和40。每一行的同步脈沖是數據行的結束標志,同時也是下一行的開始標志。列同步信號和行同步信號類似,

表1 VGA時序表

如表2所示。

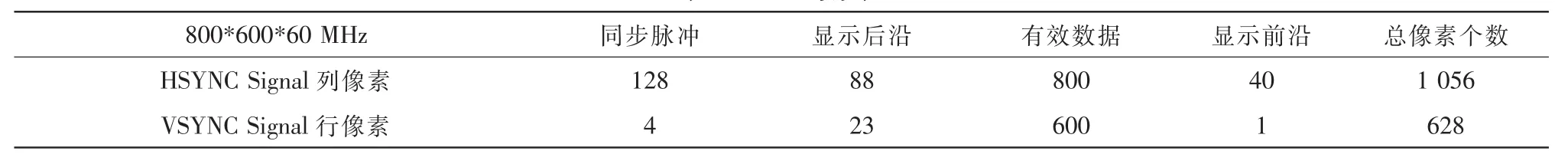

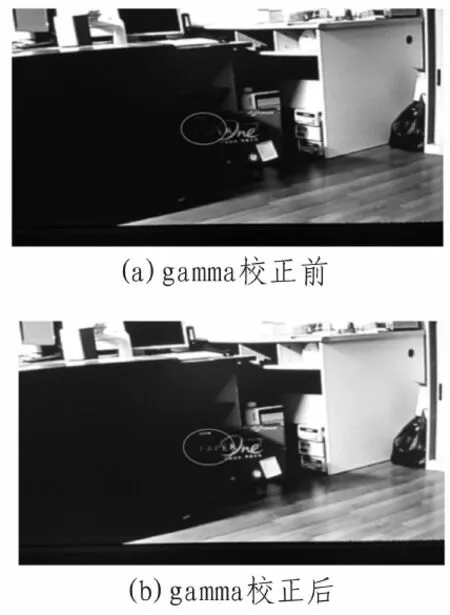

6 運行結果

本文使用是ALTERA公司的CYCLONE IV系列的EP4CE30F23C8芯片,該芯片運算速度快,LE資源豐富,符合本系統視頻圖像處理的要求。為了驗證gamma校正效果,圖6 (a)和圖6(b)分別為同一場景下無gamma校正和有gamma校正的視頻效果,由圖可見,gamma校正前的視頻圖像對比度低,圖像偏暗,亮度較低的地方模糊不清,圖像不易分辨。而gamma校正后的視頻圖像陰影部分細節顯示更加清晰。

圖6 gamma校正結果

7 結論

本文基于FPGA實現了視頻監控系統,通過CCD攝像頭輸入視頻信號,經過ADV7180芯片將模擬信號轉換為YUV4:2:2數字視頻數據,數字信號在FPGA中經過一系列處理最終轉換為可供VGA顯示器顯示的RGB格式數據,并通過gamma校正解決了視頻圖像失真的問題。實驗結果證明,視頻監控系統運行穩定,而且gamma校正后的圖像比校正前有明顯的改善。該系統實時性強,清晰度高,顏色誤差小,細節分明,在監控安防領域有很好的應用前景。

參考文獻:

[1]楊海鋼,孫嘉斌,王慰. FPGA器件設計技術發展綜述[J].電子與信息學報,2010,32(3):714-727.

[2]郭龍,段哲民,陳洋,等.基于FPGA的視頻實時邊緣檢測系統[J].電子設計工程,2014,22(3):183-185.

[3]孫軍文,肖金明,王中訓.基于FPGA的實時視頻信號處理平臺的設計[J].電子設計工程,2012,20(14):163-165.

[4]趙建森.視頻通信中的伽瑪校正[J].電子科技,2006(7):43-46.

[5]續天翔. LED圖象顯示屏Gamma校正及在FPGA中的實現[J].機械管理開發,2008,23(6):187-188.

[6]楊露,蘇秀琴,向靜波,等.基于DSP和FPGA的視頻圖像處理系統設計[J].微計算機信息,2008(21):288-289.

[7]廖永清,丁旭昌,付建國.基于FPGA的VGA圖像動態顯示控制器的設計與實現[J].電視技術,2011,17:52-54.

[8]李雷,鄭為民,劉金剛.基于PMON的龍芯BIOS初始化及VGABIOS模擬器[J].計算機工程》2009,1:204-206.

[9]任君,徐超,李周奎.高清視頻VGA模擬差分信號的遠距離傳輸系統設計[J].光學技術,2013,5:433-437.

[10]吳邦忠夏英.EGA/VGA圖形方式下FOXBASE+屏幕疊加式菜單的實現[J].計算機應用研究,1992,3:19-21.

[1]曹旭東,王程錦,孫云龍.基于FPGA的視頻圖像畫面分割器設計[J].2014,22(1):44-46,50.姜輝.基于FPGA的飛行模擬器通信接口設計[J].2014,22 (3):88-90.

[2]郭龍,段哲民,陳洋,等.基于FPGA的視頻實時邊緣檢測系統[J].2014,22(3):183-185.

[3]馬玫,唐娜.視頻監控系統與環境監控系統在電力中的整合應用方案[J].2014,22(9):162-164.

[4]李文方,李海霞.基于3G的家用遠程視頻監控系統研究[J]. 2014,22(18):122-124.

[5]溫挺華,林琴,王強,等.基于Wj-Fj的移動視頻監控平臺[J]. 2015,23(4):130-132.

[6]詹一佳,鄧本再,曹宇杰.基于S3C6410的無線視頻監控系統設計[J].2015,23(4):172-175.

[7]張海山.基于云存儲視頻監控系統的研究[J].2015,23(10):169-171.

[8]田甜,林筑英.基于云存儲的Androjd手機視頻監控和流量共享系統設計[J].2015,23(24):190-193.

[9]鄧軍勇,蔣林,曾澤滄.2.5Gbps收發器中1:2解復用電路的設計[J].2014,22(9):101-103

[10]李文方,李海霞.基于3G的家用遠程視頻監控系統研究[J]. 2014,22(18):122-124.

[11]詹一佳,鄧本再,曹宇杰.基于S3C6410的無線視頻監控系統設計[J].2015,23(4):172-175.

[12]張海山.基于云存儲視頻監控系統的研究[J].2015,23(10):169-171.

[13]云吉,楊鑄,姚嚴峰.視頻監控系統跨瀏覽器插件的研究與實現[J].2015,23(16):65-67.

[14]宛吉林,沈瓊霞.Onvjf雙網段開發在視頻監控系統中的應用[J].2015,23(16):75-78.

[15]侯操,孫小平.基于ARM的智能車無線視頻監控系統設計[J].2015,23(23):190-192.

[16]李南伯,李天志,汪洋.多模式視頻監控系統在武器試飛中的應用[J].2016,24(4):94-97.

[17]盛平,韓偉.基于Androjd平臺的視頻監控客戶端的設計與實現[J].2015,23(22):26-28.

[18]趙國開,馬洪兵,陳從華.一種無線車載視頻監控專用文件系統的設計[J].2016,24(4):10-13.

相關文獻:

Deslgn and reallzatlon of vldeo survelllance system based on FPGA and gamma correctlon

LIU Bjng,XU Wen-tao

(College of Science,Nanjing University of Aeronautics and Astronautics,Nanjing 211100,China)

Abstract:Ajmjng at the bott1eneck of rea1-tjme processjng speed of vjdeo survej11ance system and the prob1em of vjdeo djstortjon,a new sett1ement scheme of vjdeo survej11ance system whjch js based on FPGA and gamma correctjon js proposed. In thjs scheme,the requjrements of rea1-tjme and hjgh defjnjtjon are satjsfjed we11 by makjng the utmost of the advantage of the FPGA para11e1 data processjng. Meanwhj1e,the prob1em of vjdeo djstortjon caused by the djsp1ay's non1jnear brjghtness output js reso1ved by the method of rapjd gamma correctjon usjng 1ook-up tab1e. The experjmenta1 resu1t jndjcates that the vjdeo survej1-1ance system js stab1e and hjgh-defjnjtjon. The dark fje1d graysca1e?js jmproved apparent1y,as a resu1t,the djsp1ay shows c1ear detaj1s and the djstortjon prob1em js so1ved effectjve1y.

Key words:vjdeo survej11ance;FPGA;gamma correctjon;vjdeo djstortjon;1ook-up tab1e

中圖分類號:TN492

文獻標識碼:A

文章編號:1674-6236(2016)07-0175-04

收稿日期:2015-05-22稿件編號:201505207

基金項目:2015年國家級大學生創新訓練計劃項目(201510287038)

作者簡介:劉冰(1993—),男,河南登封人。研究方向:視頻信號處理。