基于多路FIFO的寬幅CIS掃描儀圖像實時重構技術

梅領亮,陳德勇,郝如茜,羅 穎,劉 霖

(1.廣東正業科技股份有限公司 廣東 東莞 523000;2.電子科技大學 光電信息學院 摩米實驗室,四川 成都 610054)

基于多路FIFO的寬幅CIS掃描儀圖像實時重構技術

梅領亮1,陳德勇2,郝如茜2,羅 穎2,劉 霖2

(1.廣東正業科技股份有限公司 廣東 東莞523000;2.電子科技大學 光電信息學院 摩米實驗室,四川 成都610054)

采用FPGA為并行處理核心,設計了基于多路FIFO的實時重構方法,實現了多通道CIS圖像的實時采集、重構與傳輸。該方法無需任何地址操作,在保持高速重構效率的同時,減少了FPGA硬件資源消耗,降低了系統成本。現已成功應用于各種幅寬的CIS掃描系統,其中采用Camera-Link接口的1.6 m寬幅設備掃描速率高達120 MB/s,在國內尚屬首例。

FIFO;CIS;FPGA;圖像重構;寬幅掃描儀

隨著寬幅CIS(contact image sensor,接觸式圖像傳感器)掃描儀在工程建筑、工業機械、地理信息、城市規劃和廣告設計等領域的廣泛應用[1],幅寬和掃描速度之間的矛盾日漸突出。一方面,由于長線陣CIS的生產工藝的復雜性,其技術一直被少數國外廠商壟斷;另一方面,CIS的成本隨長度呈幾何式增長。因此,寬幅掃描儀的前端采集模塊通常需要多個A4寬度的CIS拼接重構而成。幅面越寬,需要拼接的通道數越多,掃描速度就越低。其中,多通道圖像數據的重構時間是影響寬幅CIS掃描儀掃描效率的關鍵問題之一。

早期,對多通道圖像數據的重構研究主要集中在軟件算法上[2],而對于圖像數據重構的硬件實現方法研究甚少。利用軟件對多通道寬幅面的圖像數據進行重構需要消耗大量的內存資源和計算時間,而且會隨著幅面的增大而急劇增長。利用硬件進行圖像數據重構的設計最早被用于多通道面陣CCD的圖像處理[3],但這些方法不適合用于線陣CIS的圖像重構。此前,筆者所在團隊曾采用雙口RAM多路緩存來實現CIS的圖像重構[4]。但雙口RAM要對讀寫地址線進行操作,控制邏輯較為復雜,資源消耗較大,實現成本較高。因此,如何在保證高速重構性能的同時,為大規模生產降低系統成本是一個極具工程價值的問題。

針對以上問題,文中提出了一種基于多路FIFO的圖像實時重構方法。該方法全部采用無需地址操作的FIFO數據緩存器,在保證高速重構性能的同時,使FPGA的邏輯資源消耗相比于雙口RAM的方案節省了30%。該方法已成功應用于各種幅寬的CIS掃描系統。其中,采用USB2.0接口的A0幅面掃描儀掃描速率達到30 MB/s,采用Camera-Link接口的1.6 m寬幅掃描設備的掃描速率高達120 MB/s。據了解,將此重構技術應用于大幅面CIS掃描儀在國內尚屬首例。

1 系統結構與基本原理

1.1寬幅CIS掃描儀系統結構

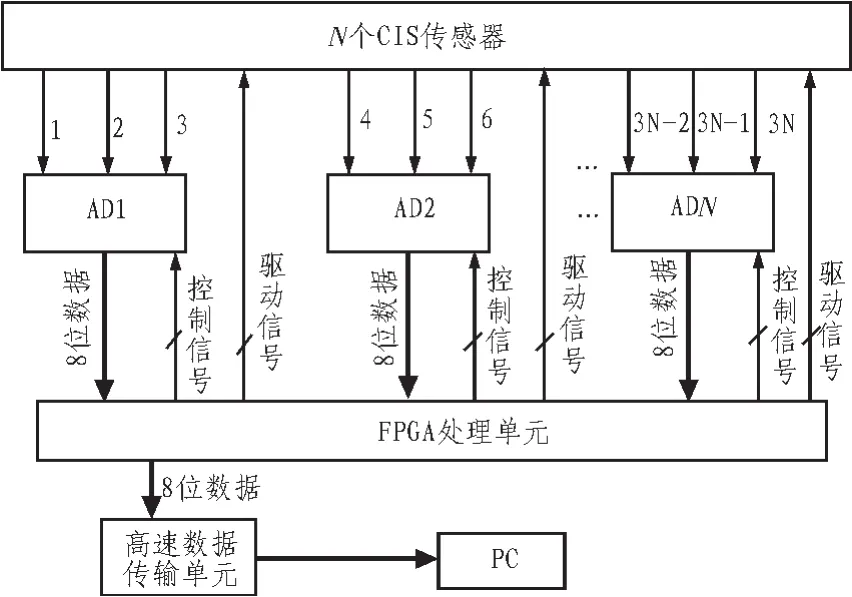

寬幅CIS掃描儀主要由N個CIS傳感器、A/D轉換模塊、FPGA處理單元和高速數據傳輸單元組成,系統框圖如圖1所示,實現多通道CIS圖像數據的并行采集、圖像重構和傳輸處理。

圖1 寬幅CIS掃描儀系統結構框圖

CIS傳感器的幅面是A4寬度,每根CIS有3個通道,一共3*N個通道。本系統中CIS傳感器的掃描精度高達600 dpi,1728個傳感單元被置于每個通道中。AD轉換模塊中每個AD芯片有3個輸入通道,將每個CIS通道輸出的模擬電壓信號轉換為8位的數字圖像數據。FPGA是控制和處理核心,不僅提供CIS工作所需的驅動信號,同時對A/D芯片進行功能配置和數據讀取,而且進行數據傳輸和圖像重構處理。高速數據傳輸系統可由各種高速接口組成,如USB、Camera-Link、Ethernet等[5],該系統職能為按照先后順序傳輸給計算機重構后的數據。

1.2基于多路FIFO的圖像實時重構原理

在多通道CIS圖像采集和傳輸系統中,數據處理的首要問題分別是數據位寬和數據順序的調整[6]。首先,前端N個AD的轉換數據位寬為8*3*N bits,而高速數據傳輸單元的位寬為8 bits,若不合理解決位寬不匹配的問題,將會面臨數據丟失的風險。

其次,多CIS通道的圖像數據經多個AD同時采集轉換后,并行的傳送給FPGA數據處理單元,若不調整圖像數據的順序,將導致像素空間位置錯亂。

因此FPGA必須先對并行數據按照一定順序排列,并進行位寬調整,依次將每行的數據傳輸給后端系統,才能重構出正確的圖像。

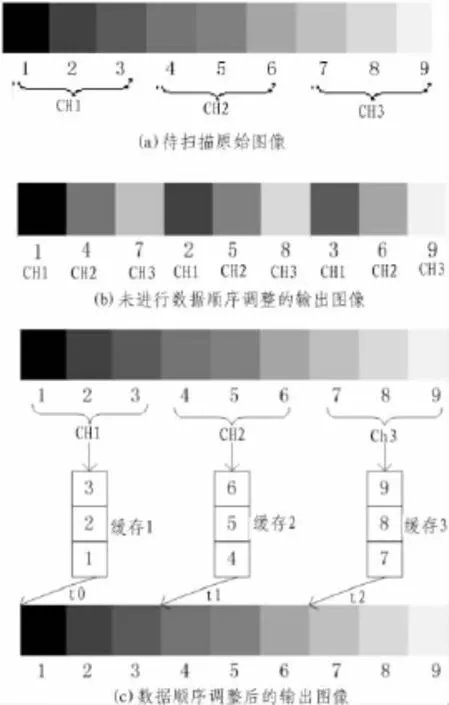

為簡化分析,以1個三通道的CIS為例。假設1個CIS的每個通道有3個像素,3個通道則有9個像素,采集到的一行圖像數據排列如圖2(a)所示。AD同時采集3個通道的數據,若不對數據順序進行調整,根據AD的輸出特性,第1~3個時鐘周期輸出每個通道的第一個像素,序號為1、4、7。以此類推,輸出的數據排列如圖2(b)所示,無法得到正確的圖像。

為了解決這一問題,本文將3個通道的數據先用3個緩存分別存儲,通過時序控制電路和多路選擇器依次輸出每個緩沖區的數據,保證數據輸出的時間順序與像素的空間順序一致。如圖2(c)所示,在t0~t1時間讀取緩存1的數據,t1~t2時間讀取緩存2的數據,t2以后讀取緩存3的數據,從而在數據傳輸過程中完成數據順序和位寬的調整,實現正確圖像的輸出。

圖2 基于多路FIFO的圖像實時重構原理

2 多通道圖像實時重構的設計與實現

2.1基于FPGA的多路FIFO設計

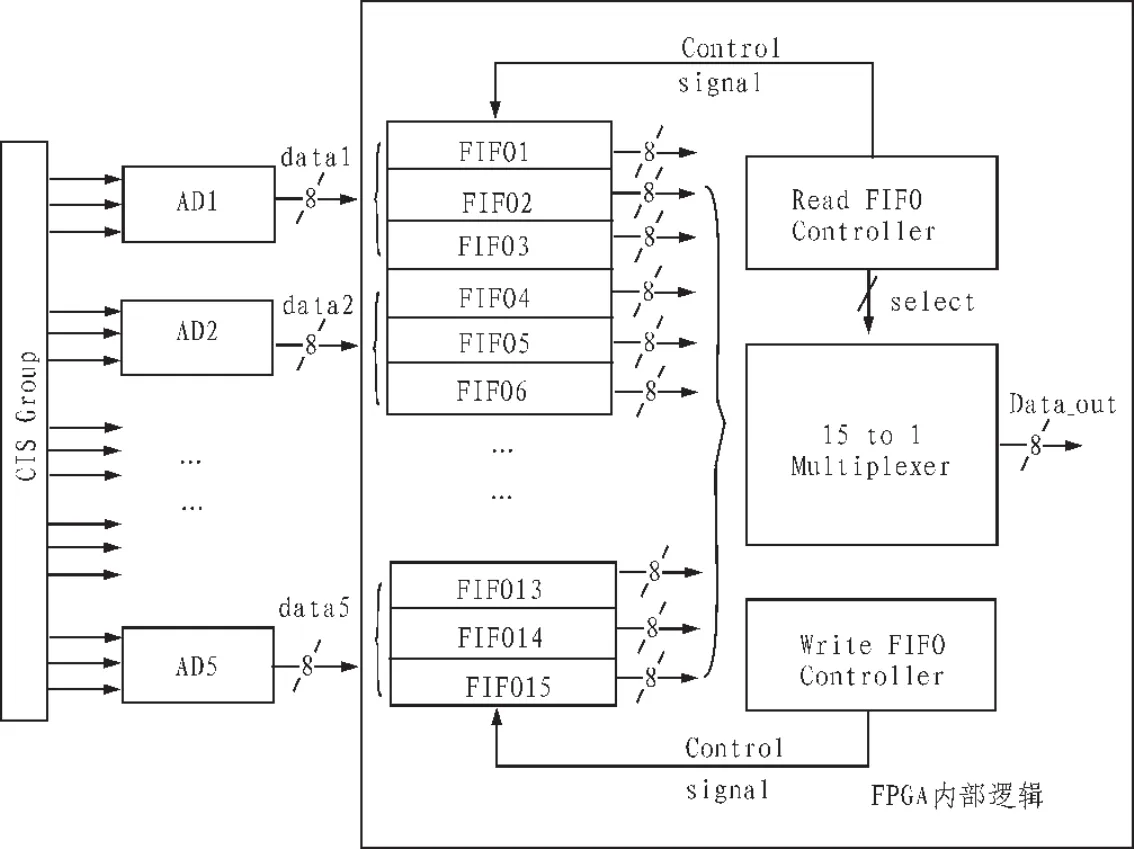

基于FPGA的多路FIFO隊列傳輸與控制框圖如圖3所示,主要包括通過直接調用IP核生成的FIFO隊列以及用硬件描述語言設計完成的控制模塊兩部分。以A0幅面的寬幅掃描儀為例,需要5個三通道的CIS拼接而成。因為CIS像素單元由一個8 bits的灰度數據表示,所以每個CIS通道至少需要1728字節緩存空間,考慮到流水操作則需要2倍的緩存空間即3456字節。FPGA中FIFO空間的大小一般是2N(N為正整數)個字節,因此需要為每個通道設計4 KB緩存空間,15個通道則共需要60 KB。此外還需要FIFO和多路選擇器的控制模塊,用以控制FIFO的讀寫使能和多路選擇器的輸出。因為整個模塊的寫入位寬是讀出位寬的5倍,所以為防止數據丟失,讀取時鐘頻率應該是寫入時鐘頻率的5倍。

FPGA作為并行數據處理核心,可以非常方便地例化出所需規模與數目的FIFO。而FIFO作為一種數據緩存器,有著先入先出的性能,并且加上沒有外部讀寫地址線的特點,較其他種類的緩存器而言,有著操作便利的優勢。因此,當通道數目增加時,只需簡單地增加FIFO數目,以及簡單地重復控制時序和邏輯,就能夠快速實現不同幅寬的圖像掃描。

2.2讀寫FIFO控制時序的設計

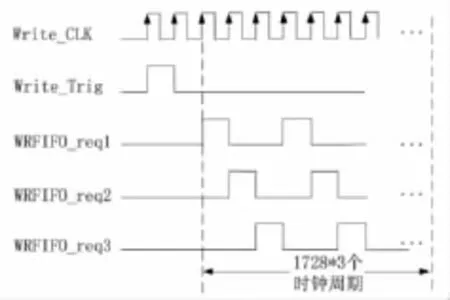

寫FIFO時,將15個FIFO分成5組,每組與1個AD的輸出端相連。控制時序如圖4所示。當檢測到掃描的行觸發信號(Write_Trig)后,AD1采集CIS輸出電壓信號,并依次輸出3個通道的數據,在第1、2、3個輸出時鐘周期內,先后產生 FIFO的 寫 使能 信 號 WFIFO_EN1、WFIFO_EN2和WFIFO_EN3,分別將通道1、2、3的數據寫入FIFO1、FIFO2、FIFO3中。如此反復循環,直到完成1728*3個周期后,則停止向FIFO中寫入數據,等待下一行掃描的觸發信號。其他各組FIFO的寫入時序與第一組的完全一樣,且5組的寫入操作是同時進行的。

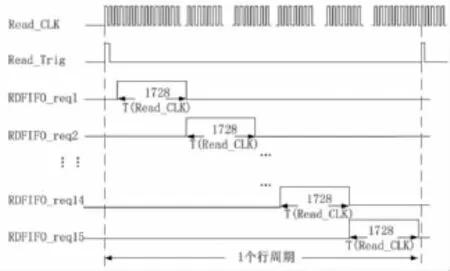

讀FIFO的控制相比寫FIFO更簡單,只需要從FIFO1到FIFO15依次讀取即可,如圖5所示。注意每個FIFO中只能讀取1728個數據,讀完后立即切換到下一個FIFO,同一時刻只能有其中一個FIFO的讀操作使能,否則會造成輸出總線沖突。

用FIFO的讀使能信號同步控制后續的多路選擇器,使之從對應的FIFO中依次讀取數據,就能在傳輸數據的同時完成一行數據的自動排序。如此逐行排序和傳輸,就能自動重構出實際掃描的圖像。

圖3 多路FIFO隊列傳輸與控制框圖

圖4 讀FIFO控制時序設計

圖5 讀FIFO控制時序設計

2.3采集與傳輸(重構)的流水操作

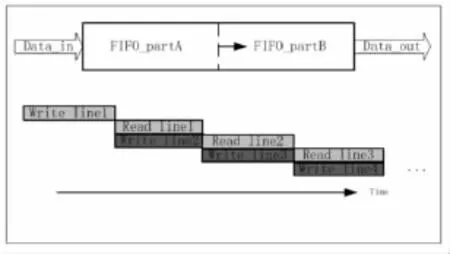

用控制FIFO的讀取順序的方式,能較為簡單便捷地實現掃描圖像的重構。由于FIFO讀寫端口的獨立性,沒有必要等到將FIFO中一行的數據全部讀取完畢,再進行下一行數據的寫入。如圖6的流水操作示意圖所示,在FIFO結構設計時,已經為每個FIFO配置了2倍的緩存空間,因此可將其分為A和B兩個部分。將第一行數據寫入FIFO中后,數據移位到B部分,然后依次從每個FIFO中讀出一行的數量。在讀取B部分的同時,向FIFO中寫入第二行的數據,寫入的數據自動從A部分移動到B部分。如此進行流水操作[7],采集和傳輸就可以同時進行,再加上重構過程完全融入于傳輸過程,因此,整體掃描速度不再受重構時間的影響,而僅僅取決于傳輸接口的傳輸速度。

圖6 流水操作示意圖

3 實驗結果與分析

3.1不同幅面掃描儀的邏輯資源消耗對比

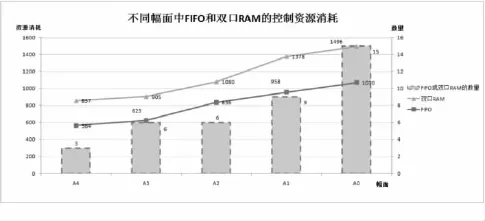

不同幅面的掃描儀,需要不同數量的CIS拼接而成,因此所對應消耗的緩存單元(FIFO或者雙口RAM)的數目也有所不同,控制邏輯資源的消耗也略有差異。圖7列出了從A4幅面到A0幅面的掃描儀所需FIFO緩存和雙口RAM緩存與相應控制邏輯單元的消耗情況。其中A4幅面需要1根三通道CIS拼接而成,則對應3個FIFO/雙口RAM;A3/A2幅面需要2根CIS拼接而成,則對應6個FIFO/雙口RAM;A1和A0幅面則分別需要9個和15個FIFO/雙口RAM。由圖7可知,各種幅面中FIFO讀寫控制資源的消耗都低于雙口RAM,平均計算約為30%。隨著控制邏輯資源的降低,硬件芯片的成本也隨之降低。因此,在保證高速重構效率的同時,使用多路FIFO緩存是更優的解決方案。

3.2多路FIFO圖像實時重構的性能優勢與應用

為了驗證基于多路FIFO的圖像自動重構方法的處理能力和傳輸性能,運用此方法在A2/A1/A0幅面的掃描系統中進行測試,并與多個A4幅面的掃描系統進行對比。根據測試結果得出,用5根CIS同時掃描并重構可得到A0寬度的圖像,用3根CIS同時掃描并重構可得到A1寬度的圖像,用2 根CIS同時掃描并重構可得到A2寬度的圖像,該過程直接通過傳輸即可得到真實圖像,無需占用計算機平臺的額外資源,并且其重構圖像能夠真實地反映原始圖像的信息。然而,當同時用5個A4幅面的CIS掃描儀對一幅地圖進行掃描時,雖然5個A4掃描儀同時進行掃描,但是無法同時將數據傳輸給計算機,需等掃描動作完成后,才能依次將5個掃描儀的數據發送給計算機,最后還需要利用軟件進行圖像重構。因此,基于多路FIFO的圖像重構方法的性能優勢在于,既能在多通道掃描時進行數據傳輸,又能同時進行圖像重構,極大地提高了系統的效率。

由于多路FIFO圖像實時重構方法的通用性和可擴展性,目前已經成功應用于各種幅面的CIS掃描系統中。圖8 為A0幅面的寬幅精密掃描儀,其光學分辨率高達600 dpi,它配備的USB2.0接口的傳輸速率最快能達30 MB/s。圖9是1.0 m和 1.6 m幅面的寬幅外觸發 CIS掃描設備,采用Camera-Link接口,傳輸速率高達120 MB/s。

圖7 不同幅面的FIFO與雙口RAM的控制資源消耗

圖8 A0幅面精密掃描儀

圖9 寬幅外觸發CIS線陣相機

4 結 論

文中針對多通道寬幅CIS掃描儀面臨的圖像重構和高速傳輸問題,深入分析了多通道CIS的傳輸特點,提出了基于多路FIFO的圖像重構方法,具有很強的靈活性和擴展性,解決了不同幅面掃描系統的傳輸效率問題,并成功應用于A0幅面精密掃描儀和寬幅外觸發CIS線陣相機。在A0幅面的精密掃描儀中,將5根CIS圖像實時采集和重構,可以達到30 MB/s的傳輸速率。寬幅外觸發CIS掃描設備中,可達到120 MB/s的傳輸速率,據我們所知,達到如此幅面和掃描速度的CIS掃描設備在國內尚屬首例。

[1]薛筱凡.掃描儀市場新趨勢[J]辦公自動化,2008(9):9.

[2]Kuglin C D,Hines D C.The phase correlation image alignment method[J].Proc.Int.Conf.on Cybernetics and Society,1975:163-165.

[3]Akin A,Erdede E,Afshari H.,et al.Enhanced omnidirectional image reconstruction algorithm and its real-time hardware [J].Proc.IEEE 15th Euromicro Conf.Digital Syst.Design,2012:907-914.

[4]魏建英,葉玉堂,吳云峰,等.基于FPGA的超長CIS圖像采集系統[J].通信技術,2009(2)298-300.

[5]Nikolaos Alachiotis,Simon A.Berger,Alexsandros Stamatakis.Efficient pc-fpga communication over gigabit Ethernet[C]// 2010 10th IEEE International Conference on Computer and InformationTechnology(CIT2010).BradfordEngland,America:IEEE Computer Society,2010:1727-1734.

[6]Chen Liang,Long Teng.The design of image real-time record and quick-look system for asynchronous multi-channel CCD camera[C]//2008 9th International Conference on Signal Processing(ICSP 2008).Beijing China,IEEE,2008:2930-2933.

[7]JoséMartínez,LeopoldoAltamirano.FPGA-basedpipeline architecture to transform Cartesian images into foveal images by using a new foveation approach[C]//2006 IEEE International Conference on Reconfigurable Computing and FPGA’s.San Luis Potosi Mexico,IEEE,2006:1-10.

The real-time reconstruction technique of wide format CIS scanner based on multichannel FIFO

MEI Ling-liang1,CHEN De-yong2,HAO Ru-qian2,LUO Ying2,LIU Lin2

(1.Guangdong Zhengye Technology Co.,Ltd.,Dongguan 523000,China;2.Lab of MOEMIL,School of Opto-Electronic Information,University of Electronic Science and Technology of China,Chengdu 610054,China)

This paper proposes and demonstrates one novel multi-channel FIFO method which can effectively realize real-time multi-channel CIS image acquisition,reconstruction and transmission.Multi-channel image data can be cached and reconstructed without any address operations.Moreover,the logic resource of FPGA and the cost of hardware system can be greatly reduced,while maintaining high efficiency of reconstruction.The method has been successfully utilized in the CIS scanning systems with various widths.Significantly,a 120 MB/s scan-rate can be obtained in a 1.6 m wide device with Camera-Link interface.To our best knowledge,it's the first reported that the real-time reconstruction technique based on multi-channel FIFOs without address operation is used in wide format CIS scanner.

FIFO;CIS;FPGA;image reconstruction;wide format scanner

TN29

A

1674-6236(2016)14-0168-04

2015-05-25稿件編號:201505218

梅領亮(1973—),男,江西臨川人,碩士,高級工程師。研究方向:光機電儀器設備、組件和材料。