利用Allegro實現(xiàn)萬兆子卡的高速電路設(shè)計

詹 萌,胡春暉

(1.武漢郵電科學(xué)研究院 湖北 武漢430074;2.武漢烽火網(wǎng)絡(luò)有限責(zé)任公司 湖北 武漢430074)

利用Allegro實現(xiàn)萬兆子卡的高速電路設(shè)計

詹 萌1,2,胡春暉2

(1.武漢郵電科學(xué)研究院 湖北 武漢430074;2.武漢烽火網(wǎng)絡(luò)有限責(zé)任公司湖北 武漢430074)

為了滿足日益增長的網(wǎng)絡(luò)需求,設(shè)計了一款用于萬兆以太網(wǎng)中高端路由器的光接口子卡,介紹了該子卡的硬件架構(gòu),使用的主要芯片及其能完成的功能。針對高速系統(tǒng)中存在的信號完整性的問題,提出了差分線對這一有效可靠的布線方式,重點(diǎn)說明了差分線對的布線準(zhǔn)則、設(shè)置方法以及其需要注意的問題。采用Cadence公司的Allegro軟件,以子卡上的SFP+接口信號為例,闡明了差分信號在PCB中的實現(xiàn)。最終通過各項測試,得以投入生產(chǎn)。

高速電路;萬兆子卡;差分線對;Allegro

隨著網(wǎng)絡(luò)技術(shù)和信息技術(shù)的高速發(fā)展,信息的交換速率和傳輸容量也在不斷提升,從以前10 Mbps、100 Mbps、1 000 Mbps到現(xiàn)在10 Gbps。以太網(wǎng)速率不斷提升的同時,光通信已發(fā)展成為現(xiàn)代信息的主要傳輸手段,而負(fù)責(zé)連接不同網(wǎng)絡(luò)的路由器為滿足當(dāng)今的數(shù)據(jù)傳輸需求,不僅擁有傳統(tǒng)的網(wǎng)絡(luò)接口,更增加了光模塊。不同速率的以太網(wǎng)相對應(yīng)使用的光模塊也不同,而本10 GbE子卡采用的是SFP+模塊。SFP+(10 Gigabit Small Form Factor Pluggable)光纖模塊,是一種可熱插拔的,獨(dú)立于通信協(xié)議的光學(xué)收發(fā)器,通常傳輸光的波長是850 nm,1 310 nm或1 550 nm,可以用于10 Gbps的SONET/ SDH,光纖通道,萬兆以太網(wǎng)中。相對之前的SFP或XFP,SFP+擁有更高的光模塊密度及更低的成本,因而是10 Gbps光收發(fā)器的最佳選擇。本文討論了四口萬兆子卡的硬件架構(gòu),主要芯片及其可以實現(xiàn)的功能,重點(diǎn)以SFP+接口部分的差分信號為例,介紹了在高速電路中高速信號的走線及阻抗控制。

1 硬件設(shè)計

1.1系統(tǒng)整體架構(gòu)

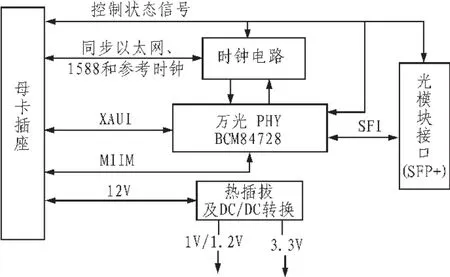

四口萬兆子卡是高端路由器的一塊接口子卡。發(fā)送數(shù)據(jù)時,先由母卡上的MAC交換芯片完成數(shù)據(jù)轉(zhuǎn)發(fā),再通過XAUI接口發(fā)送高速差分信號到萬兆PHY芯片,經(jīng)過處理后送入通過SFI接口送入SFP+光模塊再向上級設(shè)備輸入,接收數(shù)據(jù)過程則正好相反。子卡支持同步以太網(wǎng),支持LAN/WAN模式,同時提供2或4個10GBase-R/W萬兆以太網(wǎng)接口。整體架構(gòu)如圖1所示。

圖1 系統(tǒng)整體硬件架構(gòu)

1.2萬兆PHY電路(主要芯片)

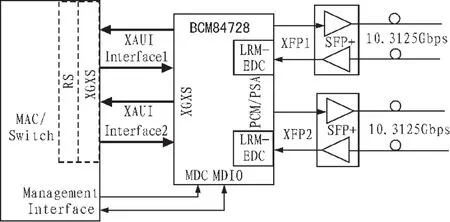

萬兆PHY電路的主要功能是完成XAUI和SFI之間的轉(zhuǎn)換,XAUI總線適用于PHY芯片及母板交換芯片之間的數(shù)據(jù)傳輸,SFI總線則用于PHY模塊和光模塊間的數(shù)據(jù)傳輸。

本子卡采用使用兩片 Broadcom公司的 BCM84728,BCM84728是一款雙通道SFI-to-XAUI的芯片,集成了能夠減小多模光纖散射效應(yīng)的EDC電路,提供4路10Gb/S的PHY通道。采用19 mm*19 mm,324-pin Rosh的BGA封裝。

整體接口框圖如圖2所示。

圖2 PHY芯片接口框圖

單片BCM84728可以實現(xiàn)以下功能:

1)XAUI可以靈活的配置成 1.0Gbps/10 Gbps XAUI/ HiGig2接口,通過AIRMAX高速連接器連接到母卡上面。

2)提供1對MDC/MDIO接口,母卡利用此接口通過連接器對PHY芯片進(jìn)行配置。

3)提供2個SFI接口與2個SFP+模塊相連。

4)母卡通過連接器給 BCM84728提供復(fù)位信號,BCM84728通過連接器給母卡提供中斷信號。

2 差分線對在本設(shè)計中的實現(xiàn)

通常的電路板使用的是單端信號線,它的接收信號等于信號與電源或地間的差值,這樣一來,信號上的噪聲就不能有效的被消除。由于子卡的速率超過了10 Gbps,如果使用單端信號線,會受到各種噪聲源的影響從而破壞系統(tǒng)的信號完整性。而差分線對是使收到的信號等于兩個互補(bǔ)并且彼此互為參考的信號之間的差值,能極大地降低信號的電氣噪聲干擾。因而在高速電路設(shè)計中,一般使用差分線對來傳輸數(shù)據(jù)。

Allegro是Cadence公司推出的先進(jìn) PCB設(shè)計布線工具,它提供了良好且交互的工作接口和強(qiáng)大完善的功能,和它前端產(chǎn)品Cadence、OrCAD、Capture的結(jié)合,為當(dāng)前高速、高密度、多層的復(fù)雜 PCB設(shè)計布線提供了最完美的解決方案[1]。

2.1差分線對

差分線對是指一對存在耦合的傳輸線。差分信號的傳輸是利用兩個輸出驅(qū)動來驅(qū)動差分線對,一根攜帶信號,另一根攜帶它的互補(bǔ)信號。我們需要的就是差分線對間的電壓差,它攜帶著要傳輸?shù)男畔ⅲ?]。

在實際進(jìn)行PCB布線時,差分走線的基本要求是等長和等距。

等長是為了確保兩根線上的差分信號的極性時刻相反,保證每個信號的傳輸時延相同,減少共模分量。在高速線路中,一般要求的等長匹配±10 mils之內(nèi)[3]。等距,即要求走線平行,則是為了使差分線對間的距離相等,從而保證差分線對差分阻抗全程都不會改變,減少反射[3]。

2.2差分線對的設(shè)置

以SFP+接口信號SG0_TXP/N為例,步驟如下:

1)創(chuàng)建差分對對象

在Allegro中,執(zhí)行Logic-assign Diff pair菜單命令,選擇建立差分對的信號TXP、TXN并命名為SG0_TX。

2)創(chuàng)建電氣約束。

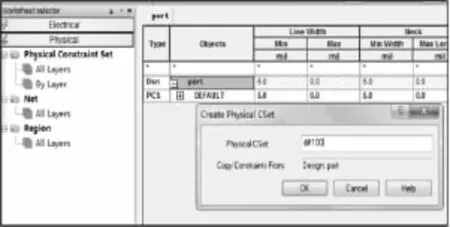

①在Electrical Constraint Set文件夾下的Routing工作表中選擇Differential Pair,如圖所示,在約束管理器中顯示出Differential Pair工作表。

②選擇設(shè)計port,單擊右鍵并從快捷菜單中選擇Ceate-Electrical Cset命令。彈出Ceate Electrical Cset窗口,輸入diff100并點(diǎn)擊OK,如圖3所示。

圖3 創(chuàng)建電氣約束

3)定義電氣約束

①選擇diff100的Primary Gap網(wǎng)絡(luò)表,單擊右鍵并從快捷菜單中選擇Change命令,彈出的對話框中選擇calculator。使用這個計數(shù)器可以幫助計算差分線間的距離和線寬,求出理想的差分阻抗。

傳輸線的特征阻抗是傳輸線的一個重要指標(biāo),不同的條件有不同的計算方法,針對母板設(shè)計的實際情況,可近似歸納成strilpline和Microstrip兩類。

對于微波帶狀線(strilpline),特征阻抗:

Z_O=60/√εγ In 4h/(0.67πω(0.8+t/ω))Ω

對于微帶線(Microstrip),特征阻抗:

Z_O=87/√(εγ+1.41)In 5.98h/(0.8ω+4)Ω

其中εγ為PCB板的介電常數(shù)。

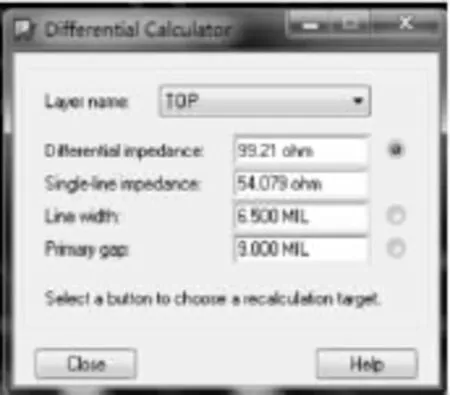

②在 Differential Calculator窗口,設(shè)置 Layer Name為TOP,選擇Primary Gap作為重新計算的目標(biāo)。根據(jù)信號對SG0_TXP/N的阻抗要求來計算差分對的線寬、線距,如圖4所示。

圖4 線寬線距計算

4)根據(jù)計算結(jié)果,定義差分對SG0_TXP/N電氣約束條件:

主要線寬/線間距:6.5 mil/9 mil;線最小間距:6 mil;差分線對不允許的非耦合線長:100 mil;差分線對Primary Gap允許的最大誤差值:0.1 mil。

5)將diff100設(shè)置應(yīng)用于SG0_TXP/N差分線對上。

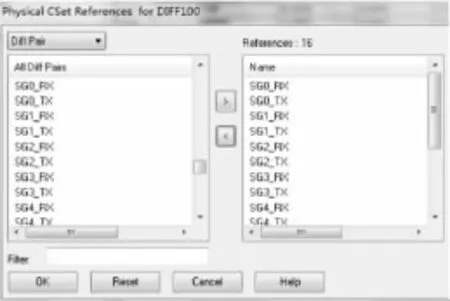

在Constraint Manager中選擇diff單擊鼠標(biāo)右鍵并選擇Constraint Set References命令,在彈出的對話框中選擇diff pair并將所有的SG差分對移到右邊窗口,點(diǎn)擊OK確定,如圖5所示。

圖5 運(yùn)用設(shè)置規(guī)則

6)布線

Allegro PCB擁有完善的Constraint設(shè)定,在按要求設(shè)定好布線規(guī)則后,在布線時只要不違反 DRC就可以達(dá)到這些要求,可以選擇自動布線或手動布線。如果違反了約束規(guī)則,將在 Constraint Manager上以紅色標(biāo)記或者在 Allegro PCB Editor的DRC上標(biāo)記出來。

然而自動布線會因為電路板的引腳分布、器件布局等原因,導(dǎo)致生成地差分線對在多數(shù)情況下都不會是完全等長。因此,為了減少差分線對的阻抗不連續(xù)點(diǎn),一般選擇手動繞線。

3 結(jié)束語

除了等長等距以外,差分線對的布線還需要注意以下規(guī)則:1)帶狀線應(yīng)保證有兩層完整的地參考平面,微帶線應(yīng)保證有完整的地參考平面。

2)走線應(yīng)該盡量短,并且過孔的數(shù)量不超過兩對。

3)滿足L>4w且L>3d原則,其中L表示差分線對和其他信號的間距,w表示差分線對的線寬,d表示差分線對的間距。

文中以光模塊接口信號為例,詳細(xì)描述了使用Allegro完成對差分線對的設(shè)置及應(yīng)用,盡可能的避免了由傳輸線效應(yīng)引起的串?dāng)_、反射及時延等問題,保證了高速電路的信號完整性。雖然在此同時也增加了對設(shè)計的要求和難度,但也從另外一方面說明,高速線路PCB的設(shè)計,不僅僅需要掌握各種芯片接口及傳輸線的理論知識,更需要在不斷地遇到問題解決問題的過程中積累經(jīng)驗并加以總結(jié),這樣才能夠取得滿意的效果。

通過PCB設(shè)計,PCB制版并完成元件焊接后,該子卡做出成品,通過了各項測試,驗證了該卡的實際參數(shù)滿足設(shè)計需要。參考文獻(xiàn):

[1]王劍宇.高速電路設(shè)計實踐[M].北京:電子工業(yè)出版社,2010.

[2]邱劍.差分線對的PCB設(shè)計要點(diǎn)[J].通信技術(shù),2010,43(6):221-223.DOI:10.3969/j.issn.1002-0802.2010.06.076.

[3]趙志超.高速差分傳輸線模型的分析與設(shè)計[D].西安:西安電子科技大學(xué),2012.

[4]賈凱賓.高速數(shù)字PCB互連設(shè)計信號完整性研究[D].南京:南京理工大學(xué),2008.

[5]楊章平.高速PCB設(shè)計中的信號完整性分析研究[D].成都:電子科技大學(xué),2014.

[6]鞏稼民,侯斌,楊祎.高速差分傳輸線的設(shè)計[J].西安郵電大學(xué)學(xué)報,2015,20(2):41-46.

[7]王延輝,謝锘.差分線對在高速PCB設(shè)計中的應(yīng)用[J].無線電通信技術(shù),2005,31(6):29-31.

The implement of high_speed circuit design in the 10GbE subcard by Allegro

ZHAN Meng1,2,HU Chun-hui2

(1.Wuhan Research Institute of Post and Telecommunications,Wuhan 430074,China;2.Wuhan Fiberhome Network Co.,Ltd.,Wuhan 430074,China)

In order to meet the growing demand of the network,a subcard in the 10Gigabit Ethernet high-end router is designed,then introduce the hardware architecture of it,the chip it used and its function.Aiming at the problems of signal integrity in the high speed system,the thesis proposes the differential pair which is an effective and reliable wiring way in the high speed system,puts the emphasis on the routing recommendation、setting methods and the roblems of attention while using differential pair.Using Allegro software,setting the SFP+interface as an example,illustrates the implementation of differential signal in PCB.Finally the subcard goes through the tests,and is put into production.

high_speed circuit;10GbE subcard;differential pair;Allegro

TN914

A

1674-6236(2016)14-0178-03

2015-07-02稿件編號:201507016

詹 萌(1991—),女,湖北武漢人,碩士研究生。研究方向:光通信系統(tǒng)。