基于HDMI標準的視頻數據編解碼器設計

肖 劍,陳 月,郭 亮

(長安大學 電子與控制工程學院,陜西 西安 710064)

基于HDMI標準的視頻數據編解碼器設計

肖 劍,陳 月,郭 亮

(長安大學電子與控制工程學院,陜西 西安 710064)

介紹了HDMI收發系統的鏈路結構,研究和分析了HDMI接口標準中視頻數據的接收方法和編解碼算法,使用Verilog HDL語言設計了視頻數據的編解碼電路,選用Modelsim6.5e工具進行了仿真驗證。仿真實驗的結果表明,所設計的各模塊電路均能夠對視頻數據進行正確的編解碼,滿足HDMI規范對視頻數據編解碼的要求。

高清晰度多媒體接口;視頻數據;編解碼算法;收發器

近年來,以高清晰多媒體接口(High Definition Multimedia Interface,HDMI)為代表的數字接口代替傳統的模擬接口已成為趨勢。HDMI接口實現了高速無壓縮的視頻和多聲道無損音頻數據傳輸,并向后兼容DVI標準。HDMI規范通過先進的編碼算法統一并簡化了用戶終端接線,能夠提供高達10.2 Gbps的數字化無損的音視頻信號傳送。選用最小化傳輸差分信號(T.M.D.S)技術,將8位像素數據轉換為10位像素數據進行傳輸,實現了較遠距離的高清晰度數字音視頻信號傳輸和直流平衡的數據傳輸[1-4]。但是即使滿足HDMI標準單鏈路數據傳輸的要求,收發系統中單個通道的數據傳輸速率也高達1.65 GHz,使得對高速的視頻數據信號進行實時的編解碼并滿足HDMI準則要求成為設計難點。

本文介紹了一種實現HDMI中數字視頻信號接收的方法,對其編解碼算法進行了分析與研究。使用硬件描述語言Verilog HDL設計完成了滿足HDMI準則要求的視頻信號編解碼器,選用Modelsim6.5e工具進行了仿真驗證,結果表明了設計的合理性,滿足HDMI規范對視頻數據編解碼的要求。

1 HDMI收發系統的鏈路結構

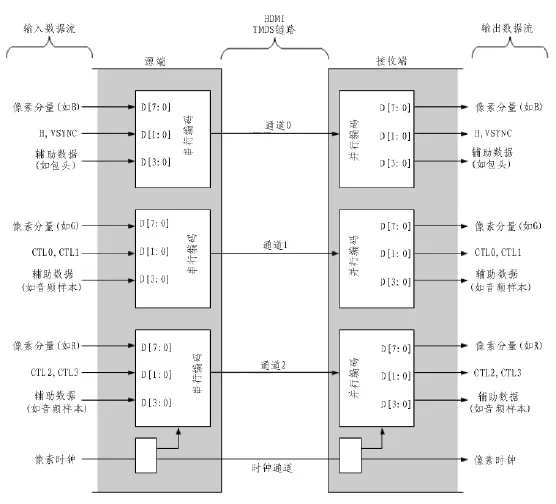

HDMI電纜和連接器中共包括4個差分線對,它們構成了T.M.D.S數據通道和T.M.D.S時鐘通道,用于實現滿足HDMI標準要求的視頻數據、音頻數據和輔助數據。在3條T.M.D.S數據通道中傳輸的是視頻編碼、音頻編碼和輔助數據。T.M.D.S時鐘通道傳送以像素時鐘速率運行的T.M.D.S時鐘,并作為接收端實現時鐘數據恢復的參考時鐘頻率。發送端視頻編碼過程中,三路數據通道中每一路中的8位視頻數據通過T.M.D.S編碼轉換為10位的直流平衡信號,以差分信號的模式串行輸出,每T.M.D.S時鐘周期傳輸10位數據。HDMI鏈路由三路T.M.D.S數據通道和一路T.M.D.S時鐘通道構成。T.M.D.S的時鐘通道的運行速率與被傳遞的視頻的像素速率有一定的比例關系。每一個T.M.D.S時鐘通道周期里數據通道傳輸10位的字數據到接收端,接收端在恢復時鐘和數據的同時,還要實現字符的同步和每一位數據的相位對齊傳輸。完整的HDMI編解碼鏈路結構如圖1所示[6]。

HDMI信源端編碼電路的輸入數據流一般包含視頻像素數據,數據封包和控制數據。數據封包流由音頻數據、輔助數據和相關聯的ECC組成。在每條T.M.D.S通道中,不管是8位的視頻數據,4位的音頻數據還是2位的控制數據,總共這些數據在通過眾多不同的方式處理后,最終傳送給T.M.D.S編碼器進行編碼。HDMI鏈路操作有3種形式,為視頻數據周期、數據島周期和控制周期。在視頻數據周期中,傳送的是數據通道的有效像素。在數據島周期中,音頻和輔助數據通過利用不同的數據包傳遞。控制周期出現在兩個非控制周期之間。

2 視頻編解碼算法及程序設計

2.1視頻編碼算法及程序設計

由HDMI編碼規范要求知,視頻數據或控制信號通過視頻數據周期與控制周期相協調來共同完成T.M.D.S編碼[4]。當使能信號DE為高電平時,通過對視頻數據周期的控制,將8位的視頻信號通過編碼轉換為10位信號輸出;當使能信號DE為低電平時,通過對控制周期的控制,2位控制信號經編碼后輸出10位碼元。每條T.M.D.S通道均有兩個控制信號介入編碼控制,3條通道總計6位數據,每一條通道的2位數據在控制周期被編碼為10位數據。視頻編碼過程可以分為兩步來實現,首先使用同或運算或者異或運算將8位的視頻信號編碼為9位的中間信號,具體選擇同或運算還是選擇異或運算作為編碼算法,是以輸入的8位視頻數據中 “1”的個數來作為判斷條件的。當輸入的數據值中“1”的個數大于4或輸入的數據值中“1”的個數等于4且輸入數據的D0位為0時,選擇同或運算的編碼算法;否則,選擇異或運算的編碼算法。其中,第一步編碼產生的9位編碼字的D8位用來表示用的是哪一種編碼算法類型,即當該過程選用的編碼算法是異或邏輯運算時,編碼輸出的D8位為邏輯高電平“1”;而當該過程選用的編碼算法是同或邏輯運算時,則編碼輸出的D8位為邏輯低電平“0”。

圖1 HDMI編解碼鏈路結構

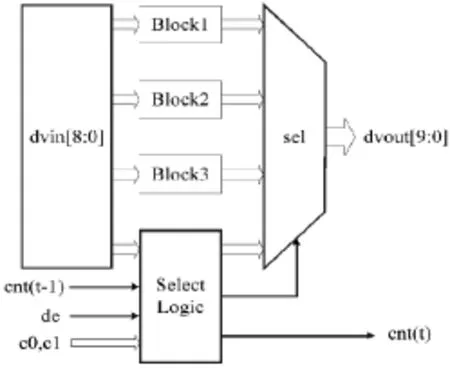

在第二步編碼流程中還包含了控制信號的編碼,通過寄存器參數cnt來控制編碼,以保證送出的10位編碼數據中的邏輯高電平“1”的個數和邏輯低電平“0”的個數盡可能相等,從而實現傳輸信號的直流平衡。當DE為高電平時,將對第一步編碼過程中輸出的9位編碼數據進行下一步的編碼運算,最終得到10位的T.M.D.S編碼。當DE為低電平時,將對控制信號進行編碼運算。因此,得出9位到10位編碼電路結構如圖2所示。

圖2 視頻信號9bit/10bit的編碼電路結構

本模塊的程序設計使用Verilog HDL語言,結合編碼電路結構和算法流程,首先對各個接口信號進行了定義,最后得到一路T.M.D.S鏈路的編碼程序encoder.v,通過對程序進行例化得到三路T.M.D.S鏈路的編碼器電路。

2.2視頻解碼算法及程序設計

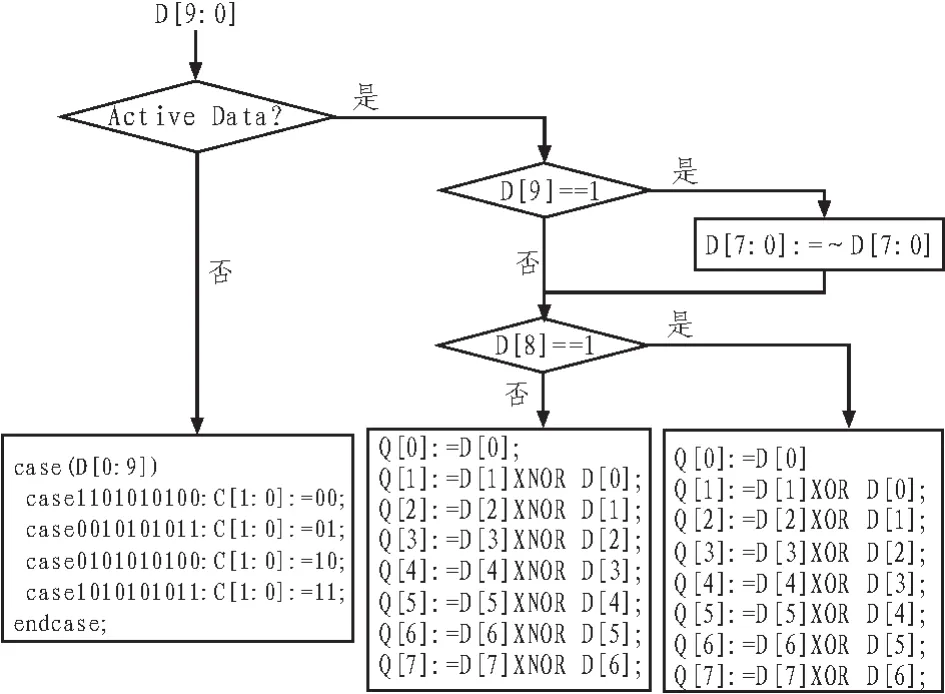

視頻解碼電路的算法流程如圖3所示[7,8]。10位串行數據通過HDMI傳輸通道送入接收端后,首先是進行串行—并行轉換,將串行數據轉換為并行數據,10位的并行數據通過解碼運算后得到恢復的8位視頻信號、2位控制信號和有效視頻使能信號DE。

圖3 視頻解碼電路的算法流程

HDMI接收端的解碼器能夠對10位的編碼信號同時進行解碼。視頻數據信號解碼模塊、控制數據信號解碼模塊和使能數據信號解碼模塊分別輸出的是8位視頻數據信號、2位控制數據信號和1位使能數據信號。解碼輸出的使能數據信號用于有效輸出標志,其用來判斷解碼出的信號類型,當使能數據信號解碼結果為邏輯高電平“1”時,視頻數據信號解碼模塊的輸出用于解碼電路的有效輸出,否則,控制數據信號解碼模塊的輸出用于解碼電路的有效輸出。

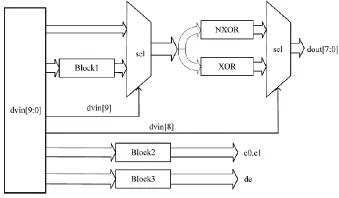

視頻數據解碼電路的程序設計如圖4所示,Din[9:0]是數據輸入的10位解碼信號。Block1是對輸入數據信號的Din[7: 0]位取反,在選通數據信號Din[9]的作用下,將Block1輸出的低8位取反數據信號各自送給同或和異或兩個解碼運算模塊,通過運算后根據解碼信號的Din[8]位的邏輯高低電平,經二選一的選擇器,選擇兩個邏輯運算結果中的一個作為最后解碼數據輸出的8位視頻數據信號Dout[7:0]。Block2是控制數據信號解碼模塊,其解碼數據輸出結果僅有四種情況。Block3是對使能數據信號DE進行解碼運算的模塊,當解碼電路輸入的10位的待解碼信號Din[9:0]是視頻數據信號的編碼結果時,使能信號數據解碼模塊、控制數據信號解碼模塊和視頻數據信號解碼模塊均會有解碼信號輸出。同樣的,當控制數據信號解碼模塊的輸入數據信號作為解碼電路輸入時,視頻數據信號解碼模塊和使能數據信號解碼模塊也有數據信號輸出。即不管是視頻數據信號編碼還是控制數據信號編碼,當這10位待解碼信號作為解碼電路輸入時,視頻數據解碼電路的各模塊均會有輸出。此時,視頻數據解碼電路選擇最終有效的輸出結果是視頻數據信號還是控制數據信號,由Block3的解碼輸出結果DE的邏輯電平狀態決定,當DE為邏輯高電平“1”時,視頻信號Dout[7:0]為有效的輸出信號,而當DE為邏輯低電平“0”時,則控制信號{C1,C0}為有效的輸出信號。

圖4 視頻解碼電路程序設計

3 視頻編解碼器的仿真結果

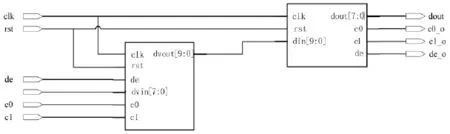

視頻編碼模塊和解碼模塊分別屬于HDMI發送端的發送芯片Transmitter和接收端的接收芯片Receiver,且它們之間也存在并轉串電路、驅動電路、T.M.D.S鏈路、字符調整和多通道同步電路、時鐘和數據恢復電路、串行轉并行電路等一系列功能電路,通過將發送端的編碼模塊和接收端的解碼模塊直接相連進行功能仿真驗證。新建top_hdmi.v文件,在此文件中對encoder和decoder進行例化,將各端口互連,編寫為整體仿真提供激勵信號的時序測試文件top_tf.v。連接好的頂層模塊如圖5所示。

圖5 編解碼模塊頂層連接原理

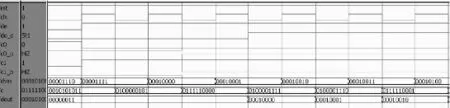

將top_hdmi.v和top_tf.v加入仿真軟件Modelsim6.5e中進行編譯仿真,在符合規范的基礎上,輸入信號激勵的描寫應盡量窮舉所有的可能性,因此,可以根據編碼模塊仿真時所使用的激勵文件來指定本模塊的激勵,仿真結果如圖6所示。從編解碼電路的聯合仿真結果可以看出,不管是視頻信號還是控制信號,當作為編碼電路的輸入信號時,若解碼電路輸出的信號與輸入信號能夠保持一致,那么就驗證了電路設計的正確性。

圖6 編解碼器仿真波形

4 結束語

論文通過對HDMI接口技術的研究,設計實現了HDMI視頻信號的編解碼器算法,并根據算法進行了程序設計,編寫完成了Verilog HDL代碼。最后,以Mentor公司的仿真工具Modelsim6.5e對編寫的代碼進行了仿真驗證,仿真結果表明了設計的正確性與合理性,滿足HDMI規范對視頻數據編解碼的要求。

[1]HDMI Licensing,LLC.HDMI Specification 1.4[S].www.hdmi. org,2009.

[2]Martin,Michael A.Assuring interoperability of HDMI Interface standards[C]//SID Conference Record of the International Display Research Conference,2005,79-82.

[3]N.Gupta,P.Bala,V.K.Singh.Area&Power Efficient 3.4Gbps/Channel HDMI Transmitter with Single-Ended Structure[C]//VLSI Design and 12th International Conference on Embedded Systems,2013:142-146.

[4]Nair,R.ComLSI Inc.,Mesa.Enhancing Signal Integrity in Cables:DVI to HDMI and Class-B Differential Signaling[C]. IEEE International Symposium on Consumer Electronics, 2007.

[5]Hao Liu,Islam Mohammed.An HDMI Cable Equalizer with Self-Generated Energy Ratio Adaptation Scheme[J].IEEE Transactions on Circuits and Systems II:Express Briefs, 2009,56(7):595-599.

[6]Bursky,Dave.High-def interface streamlines HDTV video processor[J].Electronic Design,2005,53(3):28.

[7]肖劍,王永順.基于DVI的時鐘數據數據電路設計[J].半導體學報,2008(6):63-67.

[8]李朝鋒,杜連芳,孫述桂.利用T.M.D.S均衡技術實現HDMI信號的遠距離傳輸[J].科技創新導報,2008(14):13.

[9]戴仕勇,馬潮,韋波.HDMI音頻傳輸技術及設計要領[J].電視技術,2007(S1):65-67.

Design of video data codec based on HDMI

XIAO Jian,CHEN Yue,GUO Liang

(Institute of Electronics and Control,Chang'an University,Xi'an 710064,China)

Introduced the link structure of the HDMI transceiver system Briefly,the Codec algorithm of the video data in HDMI protocol is studied and analyzed.The encoding and decoding circuit of video data is designed with Verilog HDL language and verificated by Modelsim6.5e tools.The simulation results show that the tranciever modules can realized the encoding and decoding functions and met the HDMI specification requirements.

HDMI;video data;codec algorithm;transceiver

TN919

A

1674-6236(2016)13-0190-04

2015-07-20稿件編號:201507144

肖 劍(1975—),男,陜西西安人,副教授。研究方向:控制理論與控制工程。