一種集成在DC-DC芯片中的電荷泵鎖相環設計

2016-09-19 01:13:18李容容

電子科技

2016年8期

李容容

(西安電子科技大學 電路CAD研究所,陜西 西安 710071)

?

一種集成在DC-DC芯片中的電荷泵鎖相環設計

李容容

(西安電子科技大學 電路CAD研究所,陜西 西安 710071)

設計了一種集成在DC-DC芯片中的電荷泵鎖相環。其中鑒頻鑒相器(PFD)在傳統的D觸發器結構的基礎上增加了復位延遲電路的延遲時間,減小了鑒相“死區”;電荷泵采用充放電電流對稱的源極開關結構,解決了電流失配和電荷注入作用的影響;另外,設計了一種可編程的由D觸發器構成的分頻器電路。基于CMOS工藝,采用Cadence仿真軟件對其進行仿真,結果表明該電荷泵鎖相環在鎖定時間、頻率范圍、相位抖動等方面均達到了指定的性能需求,且工作特性較好。其性能指標是:電源電壓2.4 V,頻率調節范圍250~750 kHz,鎖定時間<50 μs,相位抖動<30 ns。

DC-DC;PLL;PFD;電荷泵;可編程分頻器

隨著集成電路技術以及半導體工藝的快速發展,電源管理類芯片已廣泛應用到通信、計算機、電子等領域[1]。其中具有同步功能的DC-DC轉換器可實現多塊控制芯片的多相協同工作,提高負載驅動能力,適用于多相分布式電源管理系統[2-3]。本文所設計的電荷泵鎖相環就集成在一款同步、多相DC-DC變換器中。

1 電荷泵鎖相環基本原理

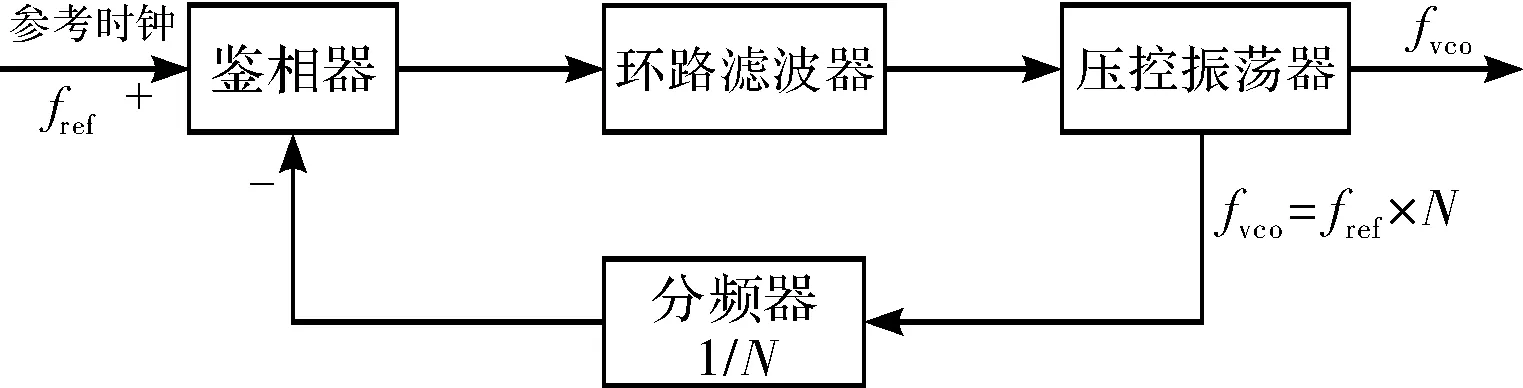

圖1 鎖相環簡化功能框圖

如圖1所示,鎖相環是一個負反饋系統,在反饋回路中壓控振蕩器的輸出被分頻器分頻(1/N倍)到低頻后,通過鑒相器和參考時鐘比較產生相位差值信號,接著相差信號在前向通道中通過電荷泵和環路濾波器處理產生電壓信號,控制壓控振蕩器產生頻率,然后這個頻率經過N分頻后,又被送入PFD和輸入參考時鐘進行比較,最終在環路的調試下,使得內部時鐘的相頻與外部同步。……

登錄APP查看全文

猜你喜歡

鴨綠江(2021年35期)2021-04-19 12:24:18

考試與評價·高一版(2020年6期)2020-11-02 02:45:24

現代裝飾(2020年7期)2020-07-27 01:27:42

流行色(2020年1期)2020-04-28 11:16:38

中國生殖健康(2019年3期)2019-02-01 06:12:26

藝術啟蒙(2018年7期)2018-08-23 09:14:18

海峽姐妹(2017年7期)2017-07-31 19:08:17

Coco薇(2017年5期)2017-06-05 08:53:16

鑿巖機械氣動工具(2016年3期)2016-03-01 04:00:25

海軍航空大學學報(2015年3期)2015-11-11 17:20:00