硅襯底GaN基LED薄膜芯片的應力調制

湯英文, 熊傳兵, 王佳斌

(1. 閩南師范大學 物理與信息工程學院, 福建 漳州 363000; 2. 南昌大學 國家硅基LED工程技術研究中心, 江西 南昌 330047)

?

硅襯底GaN基LED薄膜芯片的應力調制

湯英文1*, 熊傳兵1, 王佳斌2

(1. 閩南師范大學 物理與信息工程學院, 福建 漳州363000;2. 南昌大學 國家硅基LED工程技術研究中心, 江西 南昌330047)

將Si襯底GaN基LED外延薄膜經晶圓鍵合、去硅襯底等工藝制作成垂直結構GaN基LED薄膜芯片,并對其進行不同溫度的連續退火,通過高分辨X射線衍射(HRXRD)研究了連續退火過程中GaN薄膜芯片的應力變化。研究發現:垂直結構LED薄膜芯片在160~180 ℃下退火應力釋放明顯,200 ℃時應力釋放充分,GaN的晶格常數接近標準值。繼續升溫應力不再發生明顯變化,GaN薄膜的晶格常數只在標準晶格常數值附近波動。掃描電子顯微鏡給出的bonding層中Ag-In合金情況很好地解釋了薄膜芯片應力的變化。

硅襯底; GaN; 應力; XRD; Ag-In

1 引 言

LED已廣泛應用于顯示和照明領域[1-4]。近年來,LED的晶體生長、器件結構及器件制備等一直是產業界及研究領域的熱點。目前用來生產商品化的GaN基LED器件的襯底主要有3種:Si、SiC和藍寶石。與SiC和藍寶石相比,Si襯底具有成本低、尺寸大、質量高、導電性能好[5]等優點,但Si與GaN材料之間也具有更大的晶格失配(17%)和熱失配(56%),晶格常數和熱膨脹系數之間的差異使得Si襯底與GaN薄膜之間存在應力[6-7]。應力不只存在于外延薄膜中,也會轉移到Si襯底GaN薄膜垂直結構器件中。應力過大不僅會導致GaN薄膜出現開裂現象,嚴重影響芯片的良率,而且對LED的發光光強、波長和電流電壓也存在著一定的影響。

為了緩解GaN薄膜外延生長的應力,目前的解決辦法有生長緩沖層、使用圖形化襯底等,雖然能消除一部分應力,但殘余應力仍然很大,這是由膨脹系數和晶格常數決定的。雖然硅襯底GaN基LED得到了廣泛的市場認可,但要進入高端LED應用市場還面臨可靠性不足的問題。應力是造成芯片可靠性問題的最主要原因,要想有效釋放外延GaN薄膜給芯片帶來的殘余應力只能通過后續的芯片工藝。科研人員研發了各種釋放應力的辦法,但是總是存在一些后續問題,還需進一步完善。

本文通過優化制作垂直結構器件的晶圓鍵合(Bonding)及對去硅后的LED薄膜芯片進行熱處理等工藝來消除芯片中的應力。為了了解應力的變化,對LED薄膜芯片進行連續退火,每個溫度點退火后的LED薄膜芯片用X射線衍射法測量其應力隨退火溫度的變化情況,并用掃描電子顯微鏡(SEM)觀察Bonding層Ag、In熔化合金情況來解釋應力變化。

2 實 驗

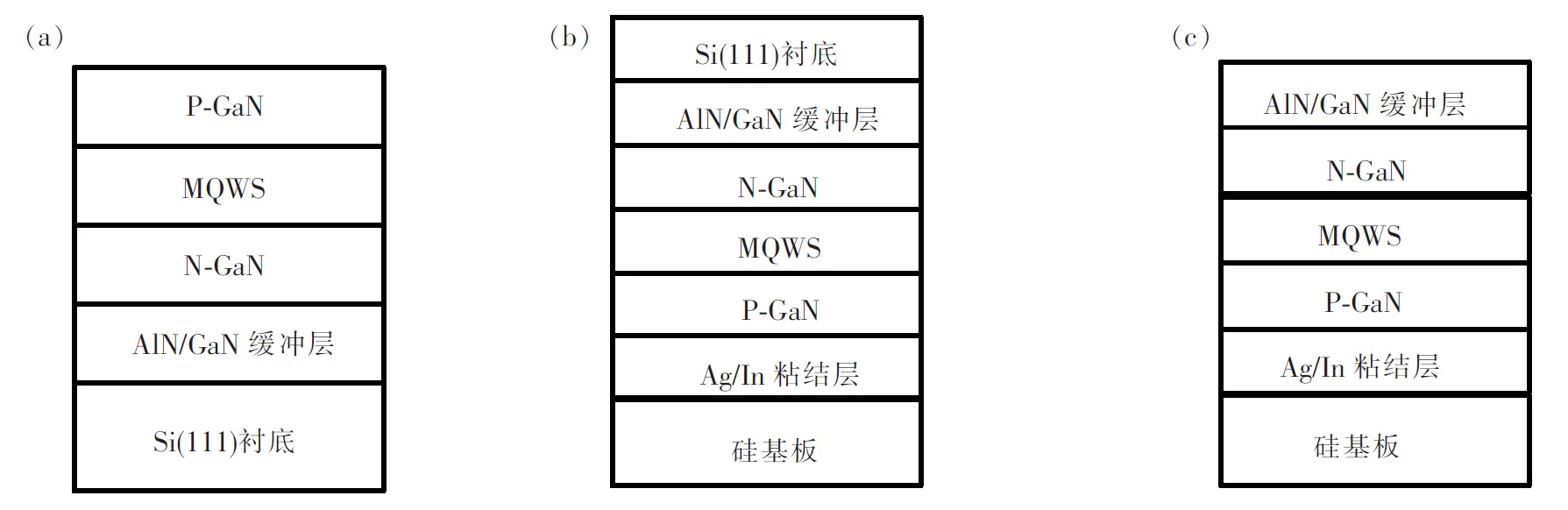

采用MOCVD生長實驗所需硅襯底GaN基藍光LED外延薄膜,生長方法見文獻[5]。將硅襯底外延薄膜經過p型激活、P電極蒸發合金、粘結層蒸發、鍵合(Bonding)、去硅襯底等工藝步驟做成樣品,樣品詳細制作方法見文獻[8], 樣品制作過程如圖1所示。

圖1樣品制作過程。(a)硅襯底GaN外延薄膜;(b)鍵合結構;(c)去硅襯底后的GaN。

Fig.1Fabricating steps of the sample. (a) GaN LED film grown on Si. (b) Wafer bonding. (c) Thin film LED chip after substrate removing.

將去硅后的晶圓片切割成25個小塊樣品,在晶圓中間取相鄰位置的8個樣品,編號為1~8,放入有氮氣保護的合金爐中退火,退火溫度分別為160,180,200,220,240,260,300 ℃,退火時間為15 min,升溫速率為1 ℃/min。每在一個溫度點退火后,將樣品1用HRXRD測量GaN薄膜的晶格常數,同時另外取一個樣品做SEM分析,觀察其粘結層金屬合金情況。

荷蘭帕納科高分辯衍射儀(XPert Pro MRD)用于研究芯片中應力的變化,衍射儀的靶材料為Cu,X射線波長為0.154 056 nm,X射線管工作電壓為40 kV,電流為40 mA,測試精度為0.000 1°,掃描范圍為0.4°~160°。Hitachi超高分辨率場發射掃描電子顯微鏡SU8010用于觀察Bonding層Ag、In熔化合金情況,加速電壓為15 kV。

3 結果與討論

3.1HRXRD圖譜計算與分析

當材料受到應力作用時,晶格間距會受應力的影響而發生變化。晶格常數可以通過提高測量衍射角的變化來計算,通過晶格常數變化可以判斷材料的應力變化[9-11]。

為了消除儀器零點誤差Δθ0,我們采用同一晶面(hkl) 的不同級數法來確定衍射峰的準確位置。設某一晶面的一級、二級衍射角的真值分別為θ1、θ2,實際測量值分別為ω1、ω2,則

(1)

根據布拉格公式2dsinθ=nλ(n為整數),有

(2)

那么

(3)

可得

(4)

那么布拉格衍射角為

由布拉格方程可計算出晶面間距

(6)

由于Si(111)面襯底上長出的GaN薄膜為六角晶系的纖鋅礦結構,則有

(7)

(8)

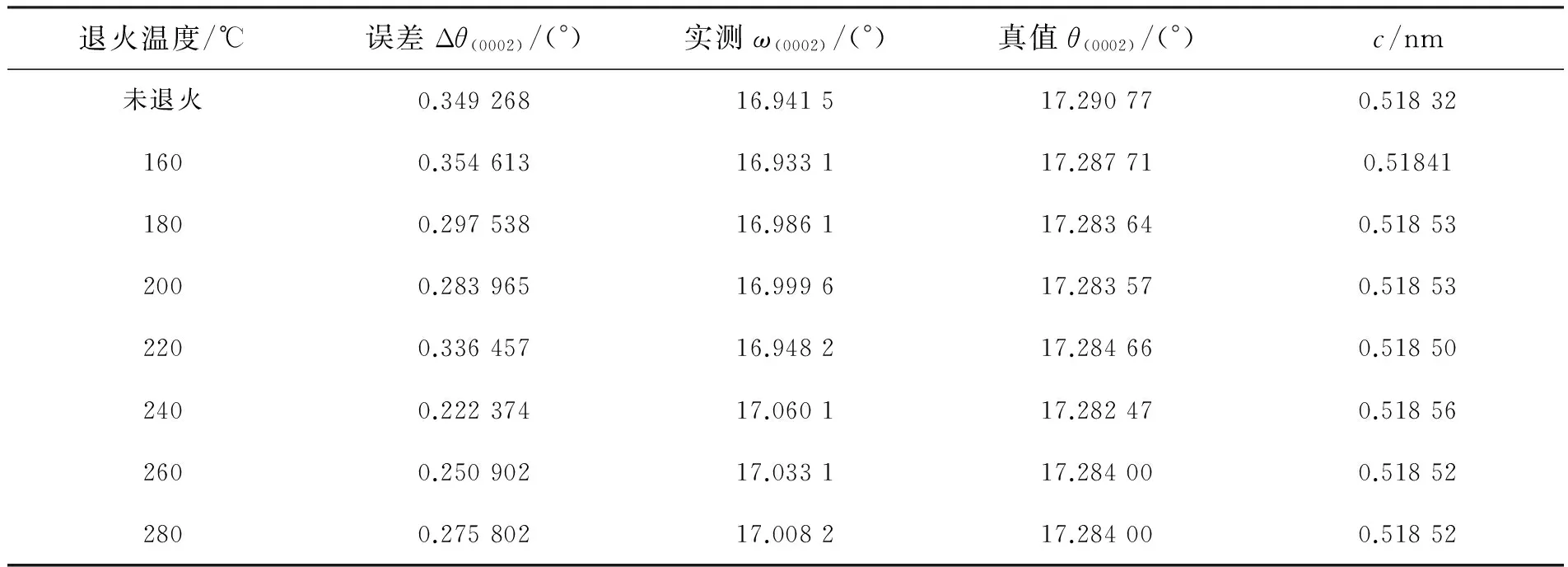

經上面公式計算出零點誤差和布拉格衍射角的真值,就可以算出GaN的a軸和c軸的晶格常數,計算結果見表1、表2。

表1 樣品1(0002)面的零點誤差、實測值、布拉格真值和晶格常數c

表2 樣品2)面的零點誤差、實測值、布拉格真值和晶格常數a

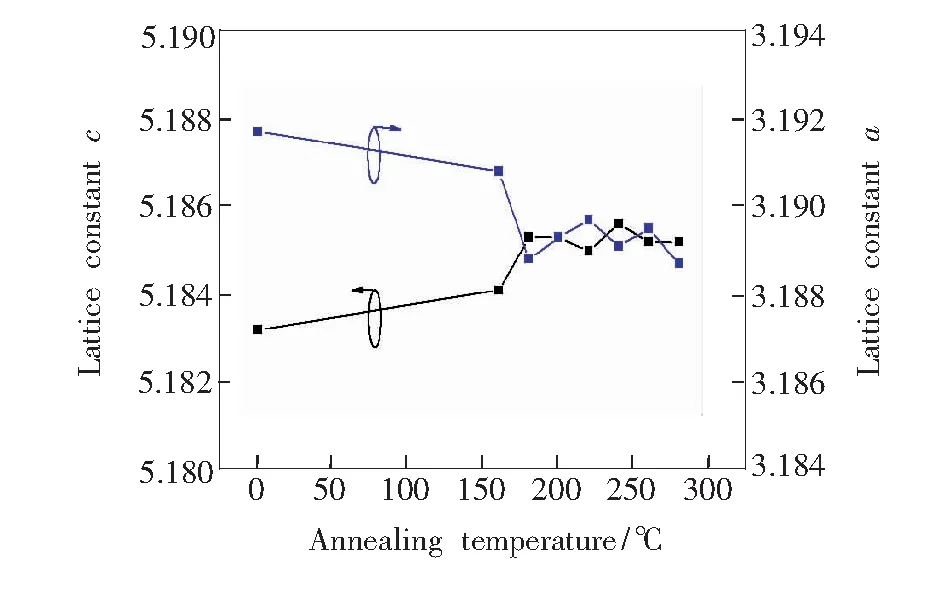

為了直觀地看到應力的變化,將表1、2制成圖2。可以看出,未退火的薄膜芯片處于張應力狀態,這和由于晶格失配和熱失配導致硅襯底和GaN之間形成張應力的結論相符。隨著退火溫度的升高,GaN薄膜的a值和c值逐漸發生改變,a值呈減小趨勢,c值呈增大趨勢。退火溫度在160~180 ℃時,a值和c值變化明顯,200 ℃時與GaN晶格常數標準值(a=3.189 1,c=5.185 5)接近。繼續升溫,a值和c值不再發生明顯變化,只在小范圍內波動。這說明隨著退火溫度的逐漸升高,薄膜中的應力是在逐漸釋放的;160~180 ℃時應力釋放明顯,200 ℃時薄膜應力釋放充分,再繼續升溫,其應力不再發生明顯變化。

圖2 連續退火中薄膜芯片GaN的應力變化情況Fig.2 Stress in GaN film as a function of annealing temperature

3.2SEM圖分析

去硅后的LED薄膜芯片由于受到Bonging的基板束縛,應力無法釋放,通過升溫退火達到了釋放應力的目的。我們通過掃描電子顯微鏡觀察Bonding層中Ag-In合金情況來分析其應力釋放機制。

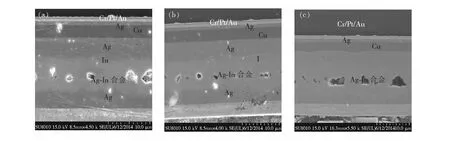

圖3是未退火以及180 ℃、200 ℃退火后的Bonding層Ag-In合金的SEM截面圖。GaN芯片薄膜在上表面,P型GaN的下面金屬依次為Ag反射鏡、Ag反射鏡保護層金屬Cr/Pt/Au、阻擋金屬Ag/Cu、粘結金屬In、阻擋金屬Ag/Cu、導電基板。根據EDS能譜分布圖和芯片的結構,已知的元素已標示在圖中。從圖中可以看出,去硅襯底后還未退火的芯片的Bonding層中的金屬擴散不充分,存在較明顯界面,低熔點的In單質較多;較低的退火溫度就可使In熔化,芯片下面金屬處于熔化狀態時,芯片就自由伸展,芯片釋放了應力;隨著退火溫度的逐漸升高,Ag和In之間發生相互擴散,界面逐漸模糊,處于可熔狀態的In也隨之減少;當溫度達到200 ℃時Ag-In界面消失,合金最為充分,應力釋放也最為充分,繼續升溫則合金區域變化不明顯,對應著薄膜應力變化也不明顯。

圖3 Ag-In合金的SEM圖。 (a) 退火前;(b) 180 ℃退火;(c) 200 ℃退火。

4 結 論

對去除硅襯底后采用導電硅基板作支撐的GaN基LED薄膜進行連續退火,通過高分辨X 射線衍射( HRXRD) 和掃描電子顯微鏡(SEM) 研究了連續退火過程中GaN 薄膜應力變化和Bonding層金屬之間的合金情況。退火溫度在160~180 ℃時,應力釋放明顯;芯片的晶格參數在200 ℃退火時最接近標準值,此時應力釋放最為充分;繼續升溫則應力值變化不大,晶格參數在標準值附近波動。未退火前,Bonding層的金屬界面較明顯;隨著溫度的升高,Ag和In相互擴散形成合金;當溫度達到200 ℃時,Bonding層中金屬界面消失,合金最為充分,應力釋放也最為充分。可見,通過鍵合層的設計及退火可以達到消除芯片應力的目的,為受應力困擾的其他芯片的制造提供了思路。本方法在硅襯底LED芯片的生產中得到了應用,芯片的良率及可靠性得到極大的提高,解決了大尺寸硅襯底GaN基LED在制造過程中良率很低、晶圓翹曲等一系列問題,為硅襯底LED的大規模市場化奠定了基礎。

[1] CRAWFORD M H. LEDs for solid-state lighting: performance challenges and recent advances [J].IEEEJ.Sel.Top.Quant.Electron., 2009, 15(4):1028-1040.

[2] NAKAMURA S. The roles of structural imperfections in InGaN-based blue light-emitting diodes and laser diodes [J].Science, 1998, 281(5379):956-961.

[3] 趙玲慧,張連,王曉東,等. 基于InGaN/GaN多量子阱雙波長發光二極管生長及發光性能 [J]. 光子學報, 2013, 42(10):1135-1139.

ZHAO L H, ZHANG L, WANG X D,etal.. Growth and optical properties of InGaN/GaN dual-wavelength light-emitting diodes [J].ActaPhoton.Sinica, 2013, 42(10):1135-1139. (in Chinese)

[4] 李正凱,嚴啟榮,羅長得,等. GaN壘層厚度漸變的雙藍光波長發光二極管 [J]. 光子學報, 2013, 42(7):757-762.

LI Z K, YAN Q R, LUO C D,etal.. Dual-blue wavelength light-emitting diodes based on varied GaN barrier thickness [J].ActaPhoton.Sinica, 2013, 42(7):757-762. (in Chinese)

[5] MO C L, FANG W Q, PU Y,etal.. Growth and characterization of InGaN blue LED structure on Si(111) by MOCVD[J].J.Cryst.Growth, 2005, 285(3):312-317.

[6] XIONG C B, JIANG F Y, FANG W Q,etal.. Different properties of GaN-based LED grown on Si(111) and transferred onto new substrate [J].Sci.ChinaSer. E, 2006, 49(3):313-321.

[7] 熊貽婧,張萌,熊傳兵,等. Si襯底GaN基LED外延薄膜轉移至金屬基板的應力變化 [J]. 發光學報, 2010, 31(4):531-537.

XIONG Y J, ZHANG M, XIONG C B,etal.. Investigation of strain of GaN light-emitting diode films transferred to metal substrate from Si(111) [J].Chin.J.Lumin., 2010, 31(4):531-537. (in Chinese)

[8] 江風益,劉軍林,王立,等. 硅襯底高光效GaN基藍色發光二極管 [J]. 中國科學: 物理學 力學 天文學, 2015, 45(6):067302-1-19.

JIANG F Y, LIU J L, WANG L,etal.. High optical efficiency GaN based blue LED on silicon substrate [J].Sci.Sin.Phys.,Mech.Astron., 2015, 45(6):067302-1-19. (in Chinese)

[9] 王雪蓉,魏莉萍,鄭會保,等. 利用高分辨X射線衍射技術計算鋁鎵氮外延膜的晶格參數 [J]. 分析測試技術與儀器, 2010, 16(3):152-156.

WANG X R, WEI L P, ZHENG H B,etal.. Study on crystal lattice constant of AlxGal-xN epitaxial film by high resolution X-ray diffraction technique [J].Anal.Test.Technol.Instrum., 2010, 16(3):152-156. (in Chinese)

[10] KISIELOWSKI C, KRüGER J, RUVIMOV S,etal.. Strain-related phenomena in GaN thin films [J].Phys.Rev. B, 1996, 54(24):17745-17753.

[11] DETCHPROHM T, HIRAMATSU K, ITOH K,etal.. Relaxation process of the thermal strain in the GaN/a-Al2O3hetero-structure and determination of the intrinsic lattice constants of GaN free from the strain [J].Jpn.J.Appl.Phys., 1992, 31(10B):L1454-L1456.

湯英文(1969-),男,湖南懷化人,博士,教授,2006年于中國科學院上海技術物理研究所獲得博士學位,主要從事GaN基寬禁帶半導體光電器件的研究。

E-mail: t-y-w2002@sohu.com

Stress Modulation of GaN Based LED Thin Film Chip on Silicon Substrate

TANG Ying-wen1*, XIONG Chuan-bing1, WANG Jia-bin2

(1.CollegeofPhysicsandInformationEngineering,MinnanNormalUniversity,Zhangzhou363000,China;2.NationalEngineeringTechnologyResearchCenterforLEDonSiSubstrate,NanchangUniversity,Nanchang330047,China)

,E-mail:t-y-w2002@sohu.com

Vertical structured thin film GaN LEDs on Si substrate were fabricated by wafer boding and substrate removing process. The LED chips were annealed at various temperatures, and high-resolution X-ray diffraction (HRXRD) measurements were performed to analyze the stress in GaN films. The results show that the annealing within 160-180 ℃ can obviously reduce the stress in GaN thin film, and the stress can be fully released at 200 ℃ and the measured lattice constants are close to the standard values of bulk GaN. Annealing at higher temperatures, the lattice constants of the GaN films only slightly fluctuate around the standard values. Scanning electron microscope (SEM) was used to analyze the cross-sectional morphology of the bonding layers. The evolution of the stress in GaN film can be well explained by the alloying degree of the Ag-In layers.

Si substrate; GaN; stress; XRD; Ag-In

1000-7032(2016)08-0979-05

2016-03-15;

2016-04-18

國家科技部支撐計劃(2011BAB32B01)資助項目

TN304

ADOI: 10.3788/fgxb20163708.0979