基于FPGA的DDR3 SDRAM控制器設計及實現

韓 進張 覽劉 鍇

(1.山東科技大學計算機科學與工程學院,山東 青島 266590;2.山東高云半導體科技有限公司,山東 濟南 250000)

基于FPGA的DDR3 SDRAM控制器設計及實現

韓 進1張 覽1劉 鍇2

(1.山東科技大學計算機科學與工程學院,山東 青島 266590;2.山東高云半導體科技有限公司,山東 濟南 250000)

文章基于Verilog語言設計并實現了一款基于高云FPGA芯片的DDR3 SDRAM控制器系統。本設計以GW2A55作為核心,參照JESD79-3F工業標準定義的DDR3 SDRAM時序操作、狀態轉換、接口定義等規范,實現了控制器的設計。設計主要分為控制層和物理傳輸層兩個邏輯層級。通過綜合驗證本設計數據傳輸接口的速率可達到800Mhz,高負載運行下錯誤數據校準率為100%,芯片邏輯資源占用率低于6.5%,因此能夠滿足用戶對高速數據傳輸以及可靠性和低資源占用的要求,同時具備同家族芯片可移植性強的優勢,并給出了系統功能仿真的驗證結果。

FPGA;高云GW2A55;DDR3 SDRAM控制器;JESD79-3F

1 引言

DDR3 SDRAM是由 JEDEC在 DDR SDRAM 的基礎上進行開發的內存技術標準,相對于 DDR SDRAM,其優勢非常明顯,使用SSTL 1.5作為核心電壓具有更低的功耗,采用“Fly-by”拓撲結構提高了信號完整性,具有8n-bit預取結構且在時鐘的上下沿均傳輸數據,從而大大提高了傳輸速率。但是由于DDR3 SDRAM操作時序繁多,模式寄存器參數眾多,工作狀態轉換復雜,需要有專門的控制器對它的讀取、寫入、刷新、預充電等進行控制。本設計目的就是充分利用FPGA邏輯資源,設計一種合理、可靠、符合實際應用且成本低的DDR3 SDRAM 控制器。論文給出整個控制器的系統設計方案,并搭建了testbench用于驗證設計的有效性,同時給出讀寫數據的RTL級仿真測試結果。

2 系統硬件設計

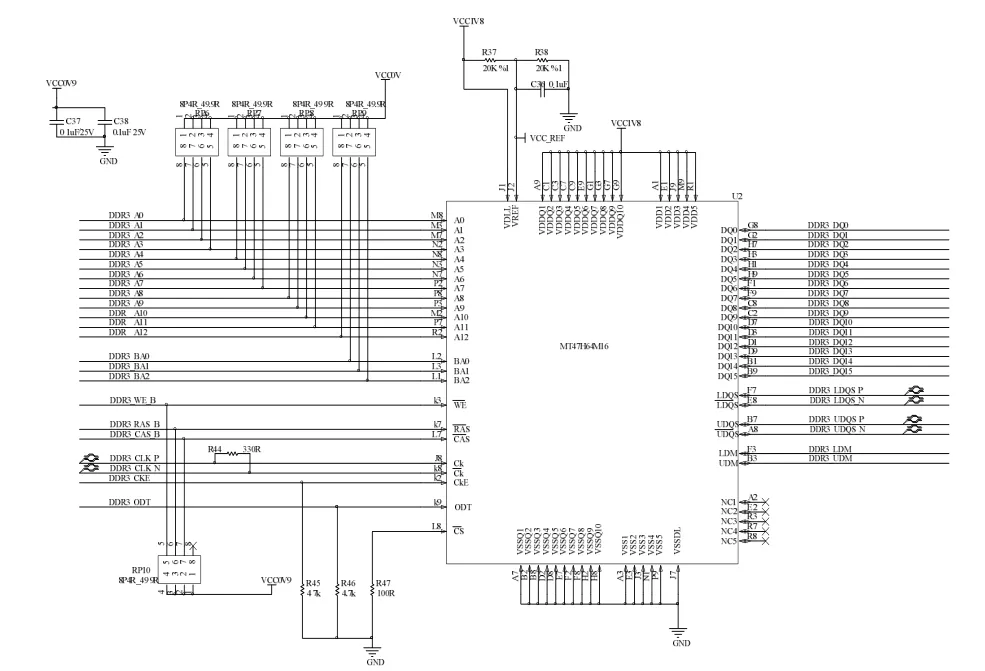

本設計的硬件平臺使用高云半導體55nm 制程PBGA484封裝的GW2A55芯片,擁有320個用戶可用管腳,具有低功耗、高性能和豐富的邏輯資源,且支持DDR3 SDRAM所使用的所有單端和差分電平標準。搭載GW2A55的開發板配置有外置鎂光 128MB X8位 DDR3 SDRAM 存儲芯片MT47H64M16HR-3,PCB上與GW2A55使用點對點連接,其電路連接原理圖如圖1所示。

圖1 DDR3 SDRAM連接管腳圖

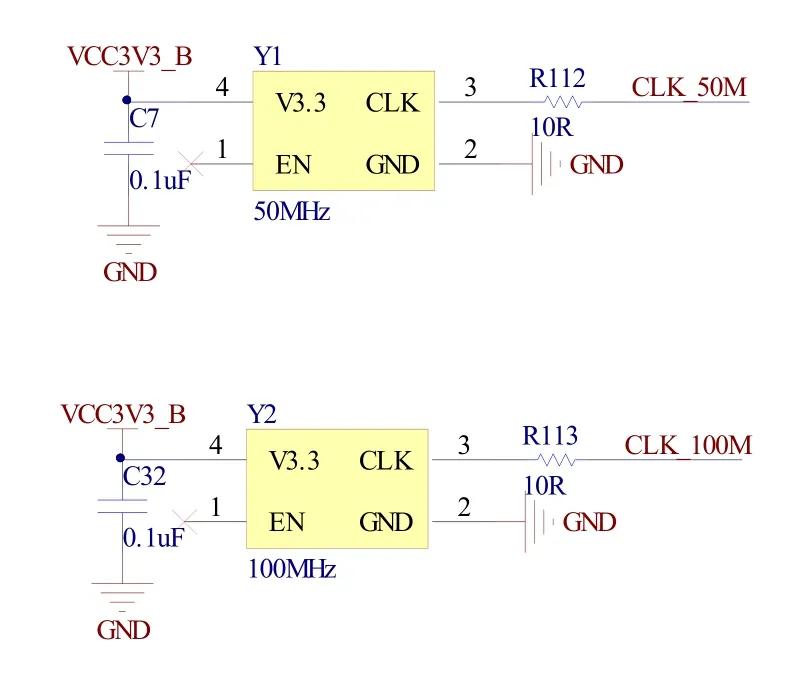

GW2A55產品的I/O 包括8個Bank,每個Bank有獨立的I/O 電源VCCO。為支持SSTL、HSTL 等I/O 輸入標準,每個Bank還提供一個獨立的參考電壓VREF。GW2A 系列FPGA 產品不同的Bank支持不同的片上電阻設置,包括單端電阻和差分電阻兩種。單端電阻用于SSTL、HSTL的輸入輸出,差分電阻用于LVDS輸入。開發板中提供了一個外部輸入50MHz晶振和一個100MHz晶振,這兩個時鐘均可以作為FPGA內部PLL的時鐘輸入。通過PLL的分倍頻可以輸出不同的時鐘并經過通用IO輸出。時鐘原理圖如圖2所示。

圖2 時鐘電路圖

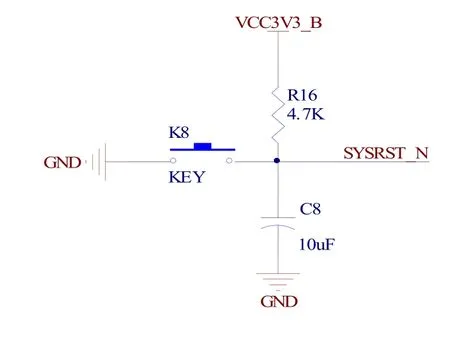

為了方便FPGA程序調試,在FPGA外面加了一個硬復位電路,通過按鍵K8、R16、C8電路實現。SYSRST_N對應FPGA管腳為N19。電路原理圖如圖3所示。

圖3 復位電路連接圖

3 系統軟件設計

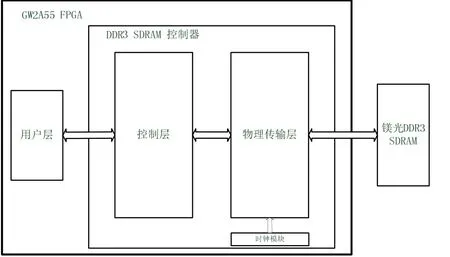

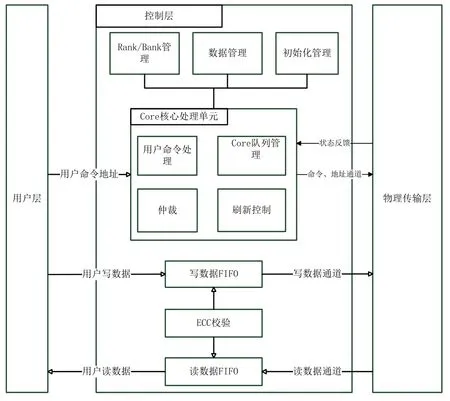

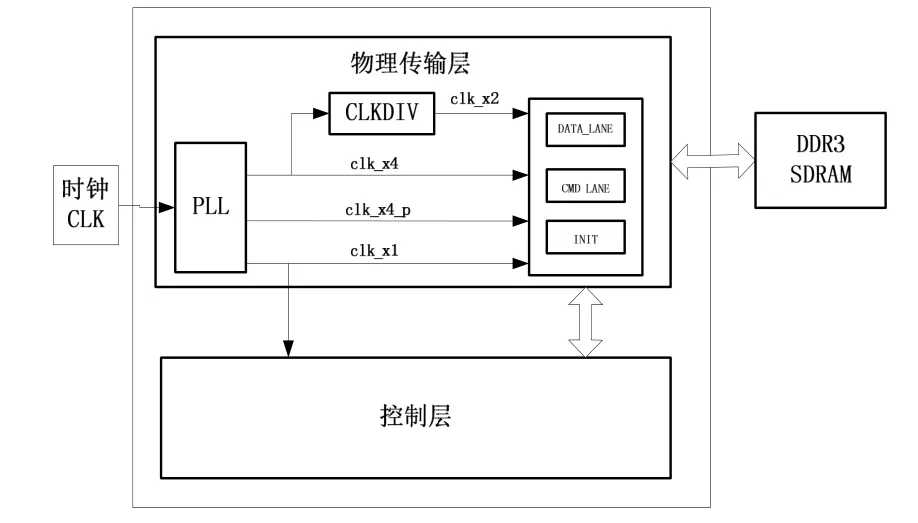

控制器屏蔽了內存操作的復雜性,用戶只需要對控制器提供的接口進行簡單的時序操作就可以對內存進行高效的讀寫。DDR3 SDRAM控制器邏輯體系結構主要由物理傳輸層及控制層構成,同時也包含時鐘模塊。用戶層將內存訪問請求發送到控制層,控制層對用戶請求進行處理后再發送到物理傳輸層,最終由物理傳輸層按照內存的時序操作要求將命令、地址、數據傳輸至內存。物理傳輸層也會接受來自內存的信號,并將信號處理后發送至控制層,然后將信號轉換成用戶能識別的信號格式發送到用戶層。控制器由Verilog語言實現,軟件開發環境使用高云半導體自主研發的新一代FPGA開發環境,支持 GW2A系列FPGA產品,能夠完成綜合、布局、布線、產生數據流文件及bit流下載等一站式工作。控制器邏輯結構設計圖如下圖4所示。

圖4 控制器邏輯結構框圖

3.1 控制器控制層設計

DDR3 SDRAM控制器控制層主要完成以下功能:

①將來自用戶的對 DDR3 SDRAM的操作請求進行轉換,包括激活、讀、寫、自動預充電讀、自動預充電寫以及預充電等命令。

②地址空間映射,將用戶發送的地址映射到相應的Bank、Row、Col,進入、退出自刷新模式。

③支持Burst Mode為4n、8n,以及OTF。

④支持ECC數據校驗(數據位寬為64位時)。

控制層介于用戶層和物理傳輸層之間,控制層的內部采用的是模塊化設計,依照控制層要完成的功能以及相關的特征需要對控制層按照不同功能進行劃分包括如下功能模塊:Rank及Bank管理模塊、數據管理模塊、初始化管理模塊、Core核心處理模塊、ECC數據校驗模塊、數據通道模塊及FIFO模塊。控制層邏輯框圖如圖5所示。

圖5 控制器控制層邏輯框圖

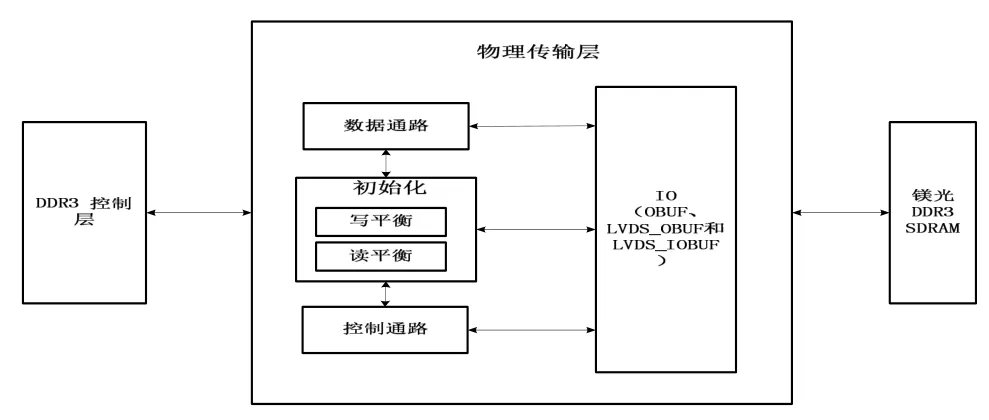

3.2 控制器物理傳輸層設計

物理傳輸層用于連接控制層和DDR3 SDRAM。物理傳輸層與控制層之間的接口符合 DDR PHY Interface(DFI)工業標準,同時兼容DDR2 SDRAM(通過Parameter進行配置),最高支持800Mhz的數據傳輸速率,DQ(物理傳輸層數據位)可以配置成8至72之間各種不同位寬,支持Burst Length4、Burst Length8和OTF模式,支持CWL、CL和AL等參數不同值的配置。

DDR3物理傳輸層主要完成以下工作:

①接收來自DDR3 SDRAM內存控制器控制層的命令,對DDR3 SDRAM進行數據讀寫操作。

②完成DDR3 SDRAM的初始化,對DDR3 SDRAM各個模式寄存器進行配置。

③完成初始化過程中DDR3 SDRAM的時鐘和復位信號的處理。

為了滿足信號的完整性要求,時鐘、地址、命令在 PCB版走線時可采用“Fly-by”拓撲結構,但會造成DQS和時鐘信號之間的歪斜,因此物理傳輸層必須支持寫平衡。寫平衡就是完成自動補償各個 DQS信號組和時鐘信號組之間的歪斜。時鐘信號組和各個DQS信號組組內的信號不用調整,因為內存芯片PCB走線時采用分組對齊的策略,組內的信號都是對齊的。同時,也必須支持讀平衡,讀平衡則是為了使得DQ能夠被正確的捕獲到,主要是根據DQS的相位來調整用于捕獲DQ的時鐘相位。物理傳輸層的邏輯結構如圖6所示。

圖6 物理傳輸層

控制通道需要完成地址、命令時鐘域的轉換,然后將控制層的命令、地址信號轉化成符合DDR3 SDRAM命令格式的信號,最后調用 ODDR硬核按照操作時序發送給 DDR3 SDRAM。數據通道用來處理用戶數據,將數據轉化成內存芯片能識別的數據格式。每一個數據通道能夠處理一位DQS和8位DQ,調用多少個通道由DQS及DQ的寬度決定。該模塊工作時會調用 FIFO對發送和接受的數據進行時鐘域的轉換,然后調用輸入解串器ISEDES4、輸出解串器OSERDES4和處理DQS的硬核模塊,最終使用IO口完成數據的發送和接受。物理傳輸層的初始化模塊配合控制層完成 DDR3 SDRAM的初始化工作,同時也包括寫平衡、讀平衡兩個重要的處理過程。

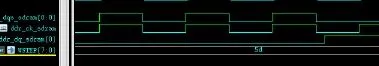

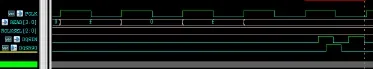

在GW2A55中,控制器是使用DQS硬核的輸出DQSW0來產生DQS信號的,在DQS硬核模塊中DQSW0會根據輸入 WSTEP[7∶0]的值產生延遲,因此調整 WSTEP[7∶0]的值可以調整DQS的相位,也就可以實現寫平衡調整。如圖7、圖8是寫平衡的調整圖。

圖7 寫平衡調整之前

圖8 寫平衡調整之后

從仿真波形中可以看到,寫平衡調整之前到達 DDR3 SDRAM端的CK和DQS之間有歪斜,寫平衡通過調整DQS的延時使得最終DQS和CK對齊。DDR3 SDRAM在PCB布線時遵守分組對齊的原則,所以DQS與CK的對齊保證了數據信號線和控制信號線的對齊。

讀平衡的目的之一是恢復出正確的 DQSR90,物理傳輸層會用DQSR90捕獲DQ,主要是通過調整DQS硬核模塊中的 RCLKSEL[2∶0]和 READ[3∶0]的值來實現。如圖 9、圖 10所示是讀平衡的仿真波形,由圖可以看出經過讀平衡調整之后DQSR90才是DQSIN經過90度相位延遲之后的信號,此時DQSR90的邊沿剛好在DQ數據的中間,數據的穩定性最強,所以系統就會用這個時鐘來捕獲正確的DQ。

圖9 讀平衡之前

圖1 0 讀平衡之后

3.3 時鐘模塊

圖11 時鐘設計圖

控制層與物理傳輸層的時鐘比例為固定的 1∶4,從 PCB板上引入的時鐘CLK經過PLL之后生成了同頻的clk_x1、4

倍頻的clk_x4、clk_x4_p,clk_x4經過CLKDIV模塊之后被2分頻生成了clk_x2。物理傳輸層內部會用到clk_x1、clk_x2、clk_x4、clk_x4_p這四個時鐘,控制層工作在clk_x1時鐘域,且發送給物理傳輸層的所有信號都應該與 clk_x1同步。PLL的倍頻倍數根據需要進行調整,比如PCB板載50Mhz時鐘源,需要使用800Mhz的數據傳輸速率,那就需要對50Mhz進行8倍頻產生400Mhz的時鐘信號,時鐘信號上下沿均采樣數據,則就會產生所需要的800MHz的數據傳輸速率。

4 仿真驗證結果

功能仿真是FPGA軟件設計和應用中的重要一步,設計完成之后需要對其進行RTL級功能仿真,來驗證本設計是否與預期一致,以及是否符合設計規范,同時也可以檢查設計中的不足之處來予以改進。以下是搭建testbench之后實際的仿真結果。如圖12所示為寫數據仿真結果。

圖12 寫同Bank同行仿真結果圖

在圖12中,給出了連續4次寫同一個Bank的同一行的情況。由控制層首先生成一個激活命令,激活該行,然后后面生成四個寫命令,完成之后跟一個預充電命令。

如圖13所示為帶預充電、不帶預充電的寫操作及含有數據掩碼的仿真結果。

圖13 預充電及數據掩碼仿真結果

圖13給出了寫同一個Bank不同行的情況。由控制層首先生成激活Bank及行的命令,然后生成帶預充的寫命令(地址位A10為1),最后行地址增加激活同Bank及不同行,生成不帶預充電的寫命令。圖中的第二個寫操作給出的數據掩碼為8’h09,可以觀察到在控制層的mc_wrdata_mask信號中也出現了該值。

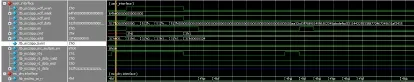

如圖14所示為讀數據仿真結果圖。

圖14 讀數據結果圖

從圖14仿真結果圖中可以看出用戶層給出了讀請求,在控制層解析產生了相應的命令并傳遞給了物理傳輸層,最終由DDR3 SDRAM相應用戶請求讀出用戶之前寫入的數據。

如圖15給出了Burst Mode為4,ECC為“ON”的情況下,寫入數據的仿真圖,64位的數據在經過ECC校驗之后,生成8bit校驗碼,將一共72bit數據發送給物理傳輸層。

圖15 ECC校驗仿真圖

5 結語

通過對JESD79-3F規定的DDR3 SDRAM規范、操作時序、特性以及物理結構進行分析,將控制器分成控制層及物理傳輸層兩層邏輯結構,使用Verilog語言實現了控制器的設計,同時對設計進行了功能仿真,結果證明了設計的可行性,能夠滿足對DDR3 SDRAM的高速讀寫操作。該設計可在所有高云GW2A家族芯片之間進行高效的移植,縮短了軟件設計的開發周期,降低了開發成本。

[1] 王巍.高性能FPGA系統:時序設計與分析[M].北京∶高等教育出版社,2014∶58-102.

[2] 楊軍.基于FPGA的DDR3控制器IP設計與研究[D].南京∶南京航空大學,2015:44-59.

[3] 劉梅.DDR3 SDRAM 控制器物理層DLL的設計與實現[D].長沙∶國防科技大學,2011∶11-18.

[4] 張永志.DDR2 內存控制器的模塊設計和驗證平臺技術研究[D].合肥∶合肥工業大學,2010∶33-36.

Design and implementation of DDR3 SDRAM controller based on FPGA

Using Verilog -HDL, Design and Implementation of DDR3 SDRAM Controller Based on Gowin FPGA, development Board useing GW2A55 as the core chip of the design. Refersto JESD79-3F Industry Standard which definition DDR3 SDRAM Operation Timing, finally Implementing the design.The design,data rate 800Mhz,calibration rate 100%,occupancy rate 6.5%,can meet the requirement of high-speed data transmission, system reliability, low resource utilization, high portability, at last given the waveform result of simulation.

FPGA; Gowin GW2A55; DDR3 SDRAM controller; JESD79-3F

TP399

A

1008-1151(2016)10-0001-04

2016-09-10

山東省自然科學基金資助(ZR2015DM013)。

韓進(1968-),女,山東青島人,山東科技大學計算機科學與工程學院教授,博士,碩士生導師,研究方向為嵌入式計算機控制、計算機系統結構、電子電路;張覽(1990-),男,山東菏澤人,山東科技大學計算機科學與工程學院碩士研究生,研究方向為嵌入式系統技術;劉鍇(1986-),男,山東煙臺人,山東高云半導體科技有限公司高級軟件工程師,碩士研究生,研究方向為嵌入式系統技術。