多串口并行通信數(shù)據(jù)傳輸系統(tǒng)設(shè)計

王春媚

摘 要: 傳統(tǒng)多串口并行通信數(shù)據(jù)傳輸系統(tǒng)無法自主獲取串口號,需手動選擇再打開串口,需要使用者事先了解接口編碼,這無形增加了系統(tǒng)的工作時間。為此,設(shè)計一種基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng),該系統(tǒng)中的串口數(shù)據(jù)接收模塊采集多串口數(shù)據(jù),并通過控制寄存器達到控制通信數(shù)據(jù)波特率的目的。系統(tǒng)利用Nios Ⅱ處理器使8種信道共同進行傳輸工作,其將數(shù)據(jù)傳輸?shù)讲⒋D(zhuǎn)換模塊。并串轉(zhuǎn)換模塊對輸出的8位并行數(shù)據(jù)添加通道標(biāo)識、并串轉(zhuǎn)換處理,再將處理后的并行數(shù)據(jù)傳遞到串口輸出選擇模塊中。依據(jù)數(shù)據(jù)脈沖上升沿設(shè)計串口輸出選擇模塊,該模塊通過多路分配器將有數(shù)據(jù)通道的數(shù)據(jù)串行逐位送出。系統(tǒng)在軟件中進行了傳輸設(shè)計、Nios Ⅱ處理器流程設(shè)計以及通信設(shè)備類的設(shè)計與封裝。實驗結(jié)果表明,所設(shè)計系統(tǒng)在 FPGA上正確實現(xiàn)了8個串口數(shù)據(jù)的傳輸,并且具有較高的數(shù)據(jù)接收成功率。

關(guān)鍵詞: 多串口; 并行通信; 數(shù)據(jù)傳輸系統(tǒng); 數(shù)據(jù)采集

中圖分類號: TN911?34; TP393 文獻標(biāo)識碼: A 文章編號: 1004?373X(2017)04?0086?05

Design of a data transmission system for multi?serial port parallel communication

WANG Chunmei

(Tianjin Light Industry Vocational Technical College, Tianjin 300350, China)

Abstract: The traditional multi?serial port parallel communication data transmission system is unable to obtain the serial port number autonomously, which means that its users must know the interface code in advance. This increases the working time of the system intangibly. Therefore, a multi?serial port parallel communication data transmission system based on FPGA was designed. In this system, the serial port data receiving module is used to collect the multi?serial port data and control the communication data baud rate through the control register, and the Nios Ⅱ processor is adopted to make eight kinds of channels work together for data transmission to the parallel?serial conversion module. The parallel?serial conversion module adds channel identification to the output 8?bit parallel data, executes the conversion processing. and sends the processed parallel data to the serial port output choosing module. The serial port output choosing module is designed according to the data pulse rising edge. The module sends out the data in each channel bit by bit in serial mode through demux. The transmission system design, the workflow design of Nios Ⅱ processor and communication equipment design and packaging are performed in the software. The experimental results show that the system has realized the data transmission in eight serial ports on the FPGA, and has high success rate of data reception.

Keywords: multi?serial port; parallel communication; data transmission system; data acquisition

0 引 言

隨著計算機技術(shù)的迅猛發(fā)展,測試系統(tǒng)的總線技術(shù)也得到了一定的提高,人們對計算機與設(shè)備的通信能力要求越來越高。串口傳輸技術(shù)的出現(xiàn),是實現(xiàn)以上要求的重要發(fā)明[1?4]。傳統(tǒng)多串口并行通信數(shù)據(jù)傳輸系統(tǒng)無法自主獲取串口號,需手動選擇再打開串口,需要使用者事先了解串口號,大大降低了系統(tǒng)的運行效率。因此,研究出可自主辨識串口號的多串口并行通信數(shù)據(jù)傳輸系統(tǒng),成為相關(guān)人員分析的熱點[5?6]。

文獻[7]通過串行處理方式完成串口數(shù)據(jù)的并行通信,但是該方式處理長數(shù)據(jù)幀時,容易出現(xiàn)部分串行口通信數(shù)據(jù)幀被截斷的問題。文獻[8]通過RTS/CTS硬件流控制串口數(shù)據(jù),將串口通信兩端的RTS和CTS線對應(yīng)相連,數(shù)據(jù)終端通過RTS調(diào)控數(shù)據(jù)流,數(shù)據(jù)通信設(shè)備用CTS控制計算機的數(shù)據(jù)流。該方法的缺點是控制過程復(fù)雜,效率低。文獻[1]采用XON/OFF完成基于軟件流的多串口并行通信數(shù)據(jù)傳輸控制,當(dāng)串口接收端的軟件輸入范圍的數(shù)據(jù)量高于閾值,則向串口數(shù)據(jù)發(fā)送端傳遞XOFF字符,發(fā)送端采集到XOFF自發(fā)地后,終止發(fā)送數(shù)據(jù);否則,當(dāng)接收端的數(shù)據(jù)量低于閾值時,向串口數(shù)據(jù)發(fā)送端發(fā)送XOF字符,并開始發(fā)送數(shù)據(jù)。但是該方法用于文本的數(shù)據(jù)通信,具有較高的局限性。文獻[3]提出一種采用多線程并行的方式,完成多串口并行數(shù)據(jù)通信的有效控制,但是該方法的控制精度較差,會出現(xiàn)數(shù)據(jù)幀缺失的問題。針對上述問題,設(shè)計基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng)。實驗結(jié)果表明,在 FPGA上正確實現(xiàn)了8個串口數(shù)據(jù)的傳輸,并且具有較高的數(shù)據(jù)接收成功率。

1 多串口并行通信數(shù)據(jù)傳輸系統(tǒng)設(shè)計與實現(xiàn)

1.1 系統(tǒng)總體設(shè)計

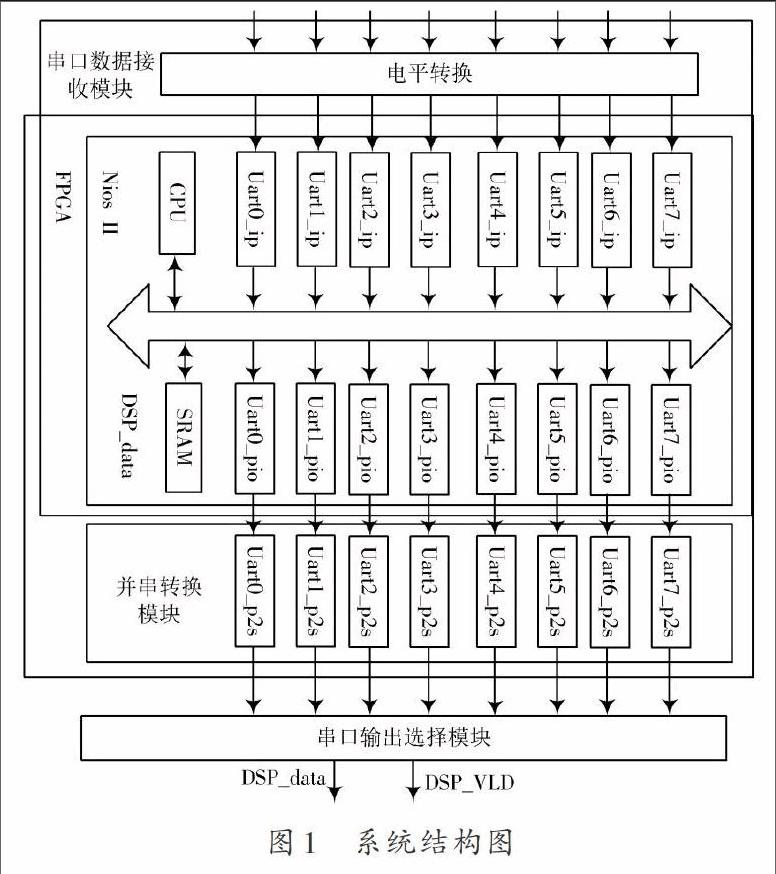

基于FPGA的多串口數(shù)據(jù)傳輸系統(tǒng)包括串口數(shù)據(jù)接收模塊、并串轉(zhuǎn)換模塊以及串口輸出選擇模塊,串口數(shù)據(jù)接收模塊的主要工作內(nèi)容是電平轉(zhuǎn)換和數(shù)據(jù)收發(fā),如圖1所示。系統(tǒng)對串口數(shù)據(jù)接收模塊的設(shè)計,主要進行了電平轉(zhuǎn)換、UART IP特性參數(shù)分析,以及寄存器控制數(shù)據(jù)波特率的設(shè)計;系統(tǒng)對數(shù)據(jù)并串轉(zhuǎn)換模塊的設(shè)計,主要進行了解析外接信道信號、并串互轉(zhuǎn)方式和時序模擬設(shè)計;系統(tǒng)對串口輸出選擇模塊的設(shè)計,主要進行了解析目標(biāo)信道串口數(shù)據(jù)以及ModelSim時序仿真,從中可以看出設(shè)計的系統(tǒng)實現(xiàn)了多串口數(shù)據(jù)傳輸?shù)墓δ埽⑶掖诓ㄌ芈士烧{(diào)。

通過FPGA UART IP將多串口數(shù)據(jù)傳遞到DSP處理器中,通過8個UART IP實現(xiàn)了8種串口數(shù)據(jù)的接收工作,以及通信數(shù)據(jù)波特率的實時調(diào)整,其將8種串口信道中的數(shù)據(jù)融合成1路數(shù)據(jù),串行傳輸?shù)紻SP處理器中。通過FPGA完成DSP多串口的拓展工作,簡化系統(tǒng)通信的數(shù)據(jù)傳輸流程,縮減系統(tǒng)運行成本。

1.2 串口數(shù)據(jù)接收模塊設(shè)計

1.2.1 電平轉(zhuǎn)換電路設(shè)計

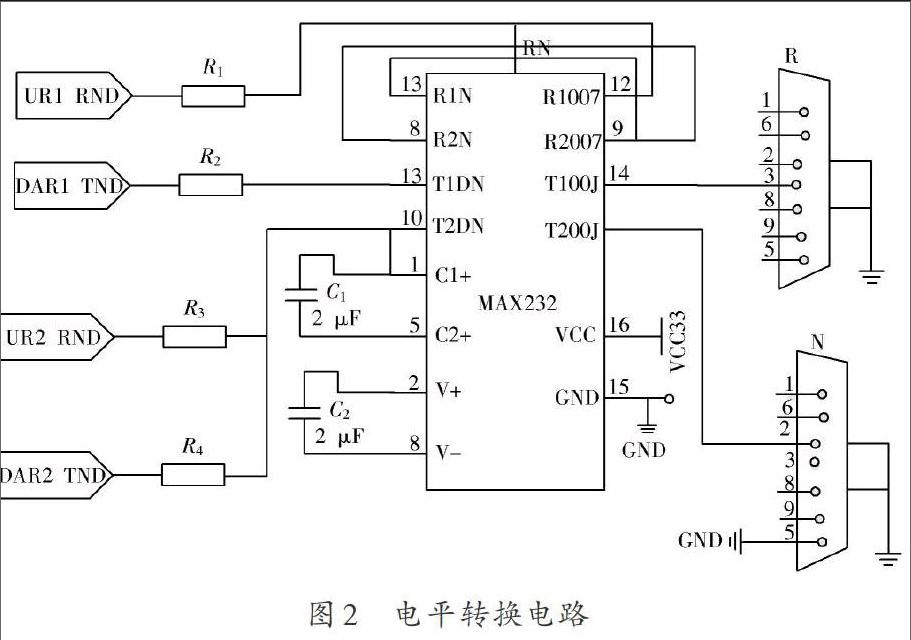

串口并行通信數(shù)據(jù)先通過電平轉(zhuǎn)換電路實現(xiàn)數(shù)據(jù)信號轉(zhuǎn)換,再將數(shù)據(jù)傳至FPGA 引腳。設(shè)計的串口數(shù)據(jù)接收模塊采用4片 MAX232芯片,完成8路UART的電平轉(zhuǎn)換,其中的2路電平轉(zhuǎn)換電路圖,如圖2所示。其他6路與此相似。

1.2.2 NiosⅡ處理器設(shè)計

基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng)中的FPGA中NiosⅡ處理器,用于采集數(shù)據(jù)并將其發(fā)送到計算機,顯控軟件接收數(shù)據(jù)并存儲。NiosⅡ處理器的組件設(shè)計以及如何搭建實現(xiàn)。設(shè)計的NiosⅡ處理器架構(gòu)如圖3所示。

從圖3中可以看出,NiosⅡ處理器包括四種組件,分別為:

(1) NiosⅡ運行μC/OS?Ⅱ所需組件:PLL,CPU,UART,其中的PLL和UART用于系統(tǒng)的調(diào)試和信息反饋;

(2) 存儲組件:SRAM Controler,EPCS Controler分別用于控制,系統(tǒng)的易失性存儲器件和非易失性存儲器件。

(3) 以太網(wǎng)組件:TSE是以太網(wǎng)的通信層,SG?DMA用于完成串口數(shù)據(jù)的傳輸。

(4) 管控組件:停止輸入、輸出PIO串口數(shù)據(jù),進而實現(xiàn)對串口數(shù)據(jù)的管控。

基于上述設(shè)計的NiosⅡ處理器,系統(tǒng)利用Altera NiosⅡ UART IP內(nèi)核實現(xiàn)多串口通信數(shù)據(jù)的收取。其利用UART IP RXD進行經(jīng)電平轉(zhuǎn)換后的串口通信數(shù)據(jù)的獲取,最后通過移位寄存器將獲取到的數(shù)據(jù)反饋給rxdata,經(jīng)由Avalon總線讀取rxdata數(shù)據(jù),并將數(shù)據(jù)傳遞到數(shù)據(jù)并串轉(zhuǎn)換模塊中。UART IP核在系統(tǒng)中的應(yīng)用如圖4所示。

UART IP核寄存器中的rxdata和txdata能夠進行串口通信數(shù)據(jù)的收發(fā)工作;status主要對數(shù)據(jù)輸入和讀取進行標(biāo)識;control管理寄存器,對接收發(fā)送數(shù)據(jù)時的中斷使能進行管理;divisor寄存器,對串口波特率進行調(diào)整。系統(tǒng) NiosⅡ處理器經(jīng)由多個UART IP進行8種串口信道的傳遞工作,主要將PIO 輸出的通信數(shù)據(jù)傳輸?shù)讲⒋D(zhuǎn)換模塊。

1.3 并串轉(zhuǎn)換模塊設(shè)計

系統(tǒng)利用UART IP中的PIO傳遞出8位串口并行數(shù)據(jù)(取pio_0_data[7:0]通道為分析對象),這些數(shù)據(jù)傳遞給并串轉(zhuǎn)換模塊,該模塊對數(shù)據(jù)進行通道標(biāo)識和并串轉(zhuǎn)換處理,再將處理后的數(shù)據(jù)傳遞到串口輸出選擇模塊中。并串轉(zhuǎn)換模塊對串口數(shù)據(jù)進行通道標(biāo)識的過程,也就是擴展串口數(shù)據(jù)pio_0_data到16位,高8位是通道標(biāo)志,標(biāo)識第一通道為1,第二通道為2,……,第八通道為8。通過移位寄存器完成16位數(shù)據(jù)的并串轉(zhuǎn)換。p2s_u0串口的數(shù)據(jù)并串轉(zhuǎn)換RTL視圖如圖5所示,可以看出8′h01被當(dāng)成首路串口標(biāo)識賦值在pio_data[15:0]的高8位。

1.4 串口輸出選擇模塊設(shè)計

NiosⅡ UART IP 每次接收到串口數(shù)據(jù)后,會形成對應(yīng)的脈沖信號,脈沖信號將指引著串口輸出選擇模塊進行工作。每個脈沖信號均會令data_vld產(chǎn)生周期性的電平信號,通常為高電平信號。這是由于Nios Ⅱ為該通道設(shè)置了特定的優(yōu)先處理參數(shù),使其在相同情況下僅產(chǎn)生惟一中斷。因此設(shè)計多路分配器DSP,逐次輸出存在數(shù)據(jù)通道的數(shù)據(jù)串行。DSP 處理器利用其收取到的16位通信數(shù)據(jù),進行數(shù)據(jù)串口的選擇。

2 軟件實現(xiàn)

2.1 μC/OS?Ⅱ多任務(wù)執(zhí)行流程設(shè)計同通信數(shù)據(jù)的管控

μC/OS?Ⅱ操作平臺的多方處理能力,使其能夠進行多任務(wù)的同時處理,使得CPU在多個程序間進行高速變換,確保各程序在一段時間中獲取多次的CPU占用。在NiosⅡ處理器中嵌入μC/OS?Ⅱ操作系統(tǒng),再在該操作系統(tǒng)中塑造兩個任務(wù):任務(wù)Concisee AssociatArchitec Work用于塑造斷開網(wǎng)絡(luò)關(guān)聯(lián)和數(shù)據(jù)傳輸管理;任務(wù)Concisee AssociatArchitec_trans Work用于發(fā)送串口數(shù)據(jù)。具體實現(xiàn)過程為:驅(qū)動μC/OS?Ⅱ中 UEBegain()函數(shù)運行,逐次進行Concisee AssociatArchitec Work任務(wù)和Concisee AssociatArchitec_ trans Work 任務(wù)的初始化,確保兩個任務(wù)并行工作,Concisee AssociatArchitec Work 接收到客戶端的網(wǎng)絡(luò)關(guān)聯(lián)申請時,連接網(wǎng)絡(luò)。

(1) Concisee AssociatArchitec Work獲取客戶端端口網(wǎng)絡(luò)指令時,網(wǎng)絡(luò)中斷;

(2) Concisee AssociatArchitec Work 獲取客戶端終止發(fā)送指令時,RAM無法進行寫操作,停止串口數(shù)據(jù)發(fā)送;

(3) Concisee AssociatArchitec Work 采集客戶端發(fā)送串口數(shù)據(jù)指令后,RAM進行數(shù)據(jù)的寫操作,若RAM寫入31 543個數(shù)據(jù),此時的輸入中斷將移動至脈沖信號的攀升處,調(diào)用UEEin Post()進程令數(shù)據(jù)數(shù)量自動傳送出去,Concisee AssociatArchitec_trans Work中UEEin Sinre()函數(shù)發(fā)現(xiàn)該信號量后,開始發(fā)送數(shù)據(jù),完成全部數(shù)據(jù)的發(fā)送后,驅(qū)動UEEin Glv()函數(shù)過濾信號量,接收后續(xù)脈沖沿形成的信號量,上述過程不斷運行,完成串口數(shù)據(jù)的發(fā)送。

NiosⅡ處理器中融入μC/OS?Ⅱ的工作流程以及串口數(shù)據(jù)發(fā)送控制過程,如圖6所示。

2.2 通信設(shè)備設(shè)計和其封裝技術(shù)

系統(tǒng)利用Pcomm數(shù)據(jù)庫對通信設(shè)備進行設(shè)計,并根據(jù)其載入和封裝技術(shù),將其分為串口和設(shè)備兩種類型。串口類型能夠進行串口的開啟、封閉以及通信數(shù)據(jù)的預(yù)設(shè)工作。

設(shè)備類型則能夠?qū)⒍啻诘氖瞻l(fā)特點一一分析出并存儲,隨即對其進行編譯和解編譯,CALLBACK函數(shù)能夠?qū)崿F(xiàn)這一操作的調(diào)用。

圖6 Nios Ⅱ處理器的工作流程

軟件為串口類型設(shè)計的語言如下:

# include"P"

# Circumscription G_ins G_Subscriber+1

classGMoniaIInterface :common MSoe{

common :

int BaudRate,Parity,Amount symbol acters ,StopAmount ,Interface BKU; //串口號和通信參數(shù)

Int Kossymbol BKU,iKosAmount ;

//需要接收的字符數(shù)和實際的接收字符數(shù)

symbol Kosesymbol ;symbol *InBuf;

//接收的終止字符和接收字符串指針

urreKKceRunFlag; //串口打開標(biāo)識

MSoe* m_phold; //父窗口指針

GMon iaIInterface ();

fiction ?PSerial Interface () ;

remove GMonial Interface *pComArray[10];

remove int Com BKU;

int RunStation (MSoe* pInterface hold,useless(Rreceive *Koseinterrupt request)(int nozzle )); //將串口開啟

null cease Por(); //將串口封閉

null WriteToInterface (CSymbol Uis OutBuf); //寫串口

remove useless Rreceive Teminterrupt request (int nozzle );

//將串口數(shù)據(jù)讀取出來

null UisBaud(int baud,record,cease,parity);

//設(shè)定串口參數(shù)

useless UisKosesymbol (symbol BKU){Kose symbol =BKU;}

useless UisKossymbol BKU(int BKU){Kossymbol BKU=BKU;} };

設(shè)備類實現(xiàn)代碼如下:

class Element INS:common MSoe{

common :

Dev iceINS();

fiction ?Element INS();

CSymbol Uis Out Cache ,In Cache ;

PSerialInterface Com;

useless Mlcinge(useless){//編碼函數(shù)};

useless PctMlcinge(useless){//解碼函數(shù)};

useless Imitation (useless){//模擬函數(shù)};

};

設(shè)備初始化和數(shù)據(jù)通信控制代碼如下:

urreCPseriaIInterface View::OnKKceunication(LPARAM Interface ){

CPserial Interface Doc* uMre=GetDocument();

If(Interface ==uMre?>ume3.Com.GetInterface BKU()){

uMre?>ume3.In Cache .Empty();

for(int i=0;i

//數(shù)據(jù)轉(zhuǎn)移

uMre?>ume3.In Cache +=BYTE(uMre?>ume3.Com.InBuf[i]);

uMre?>ume3.PctMlcinge(); //數(shù)據(jù)解碼

}return 0;

}

根據(jù)上述語言為多串口構(gòu)建模型,假設(shè)該模型是設(shè)備類型內(nèi)的重要組成變量,將文本的初始數(shù)據(jù)納入到文本模型和串口通信中,并引用上述語言預(yù)設(shè)串口通信傳輸類型,進而開啟模型入口,并塑造相應(yīng)的線程;采用CALLBACK語言對所構(gòu)建的設(shè)備類型模型中的線程進行整理和控制,進而實現(xiàn)多串口并行通信數(shù)據(jù)的通信處理。

3 實驗分析

實驗在計算機USB接口上連接了UART轉(zhuǎn)換器,并參考說明對其進行啟動,當(dāng)UART轉(zhuǎn)換器亮起綠燈,則代表模型已完成構(gòu)建。令UART轉(zhuǎn)換器的信號總線短路,排除外部信號干擾,實現(xiàn)傳輸信號的自動收發(fā)。利用本文所設(shè)計的基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng)在上述模型中進行工作,UART轉(zhuǎn)換器的面板燈的亮滅,代表本文系統(tǒng)的工作狀態(tài)是否正常。利用UART轉(zhuǎn)換器的串口號,設(shè)置合理的比特率、校驗位和停止位,并向發(fā)送區(qū)輸入一周期的正弦數(shù)據(jù),按下發(fā)送數(shù)據(jù)鍵,接收數(shù)據(jù)區(qū)會呈現(xiàn)發(fā)送的正弦波形,同時隨著時間的變化而進行平穩(wěn)移動,直至按下終止鍵。自發(fā)自收情況下的系統(tǒng)檢測結(jié)果如圖7所示。用本文設(shè)計的基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng)獲取的結(jié)果如圖8所示。

對比分析圖7和圖8能夠看出,本文系統(tǒng)檢測到的串口通信數(shù)據(jù)與正常運行狀態(tài)下的輸出數(shù)據(jù)無較大差別,證明本文系統(tǒng)是有效的。實驗解析了本文系統(tǒng)中兩個驗證標(biāo)準(zhǔn),分別為數(shù)據(jù)接收的時間延遲以及其成功率。利用多串口將通信數(shù)據(jù)從各并列系統(tǒng)向終端傳輸,必然會引起數(shù)據(jù)接收的時間延遲,且不同系統(tǒng)的延遲時間狀態(tài)均不一致。把接收數(shù)據(jù)的終端時間減去并列系統(tǒng)的時間延遲時間,即可得到延遲時間(稱作“延時值”);數(shù)據(jù)接收的成功率則用終端接收數(shù)據(jù)的有效量與并列系統(tǒng)總數(shù)據(jù)量相比表示。

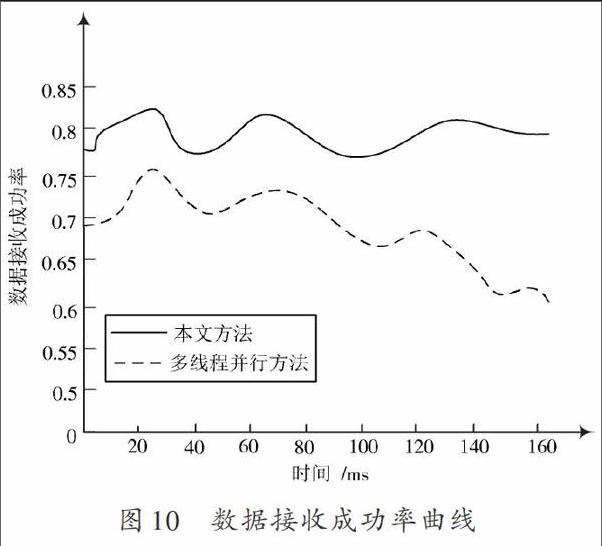

實驗選取12 m長的串口線,該串口線的收據(jù)發(fā)送頻率高達15 Hz,通信中的數(shù)據(jù)波特率是1 029 622 b/s。通過多次長時間實驗,實驗獲取本文方法和多線程并行方法的相關(guān)數(shù)據(jù)分析結(jié)果,如圖9和圖10所示。

分析圖9和圖10可得,相對于多線程并行方法,本文方法具有較低的通信延時和較高的數(shù)據(jù)接收成功率,能夠?qū)崿F(xiàn)串口數(shù)據(jù)的可靠通信。

4 結(jié) 論

本文設(shè)計基于FPGA的多串口并行通信數(shù)據(jù)傳輸系統(tǒng),該系統(tǒng)中的串口數(shù)據(jù)接收模塊采集多串口數(shù)據(jù),并通過控制寄存器達到控制通信數(shù)據(jù)波特率的目的。系統(tǒng)利用NiosⅡ處理器使8種信道共同進行傳輸工作,其將數(shù)據(jù)傳輸?shù)讲⒋D(zhuǎn)換模塊。并串轉(zhuǎn)換模塊對輸出的8位并行數(shù)據(jù)添加通道標(biāo)識、并串轉(zhuǎn)換處理,再將處理后的并行數(shù)據(jù)傳遞到串口輸出選擇模塊中。依據(jù)數(shù)據(jù)脈沖上升沿設(shè)計串口輸出選擇模塊,該模塊通過多路分配器將有數(shù)據(jù)通道的數(shù)據(jù)串行逐位送出。系統(tǒng)在軟件中進行了傳輸設(shè)計、NiosⅡ處理器流程設(shè)計以及通信設(shè)備類的設(shè)計與封裝過程。實驗結(jié)果表明,在 FPGA上正確實現(xiàn)了8個串口數(shù)據(jù)的傳輸,并且具有較高的數(shù)據(jù)接收成功率。

參考文獻

[1] 唐普英,謝啟.基于LabVIEW的多串口通信及數(shù)據(jù)存儲的研究與實現(xiàn)[J].實驗室研究與探索,2015,34(8):93?97.

[2] 侯志偉,安麗霞,包理群,等.片上雙核數(shù)據(jù)并行采集及核間通信研究[J].計算機工程,2015,41(5):83?88.

[3] 李曉,李芮,王志斌,等.基于DSP和FPGA的CAN總線通信系統(tǒng)設(shè)計[J].計算機測量與控制,2015,23(1):284?286.

[4] 璩金超,周勍.基于XPC目標(biāo)的數(shù)據(jù)并行實時通信[J].測控技術(shù),2014,33(2):46?48.

[5] 郭黎利,王百川,孫志國,等.并行組合擴頻通信系統(tǒng)變換域干擾抑制技術(shù)研究[J].遙測遙控,2015,36(1):30?35.

[6] 張庭園,李俊,李小兵,等.基于VBLAST系統(tǒng)的并行圖像傳輸策略優(yōu)化[J].重慶郵電大學(xué)學(xué)報(自然科學(xué)版),2014,26(4):488?493.

[7] 崔蔚,周力,吳凱峰,等.基于Hadoop平臺的并行線損分析系統(tǒng)研究與實現(xiàn)[J].電力信息與通信技術(shù),2014,12(2):60?63.

[8] 霍菁,雷曉鳳,李強,等.支持異構(gòu)集群并行的高能物理數(shù)據(jù)處理系統(tǒng)[J].計算機工程,2015,41(1):1?5.