基于射頻收發應用的低噪聲頻率綜合器設計

曲 明,翟 越,王 楠

(中國電子科技集團公司第五十四研究所,河北 石家莊050081)

基于射頻收發應用的低噪聲頻率綜合器設計

曲 明,翟 越,王 楠

(中國電子科技集團公司第五十四研究所,河北 石家莊050081)

隨著無線通信技術的高速發展,載波頻段的不斷升高,對收發芯片中頻率綜合器的噪聲性能提出了較高的要求。針對通信收發系統中頻率綜合器的設計,提出了一些低噪聲的設計技術,電源電壓1.2 V,采用SMIC 0.13 μm CMOS 工藝。主要對頻率綜合器主要組成模塊鑒相器、電荷泵、LC型壓控振蕩器以及ΔΣ調制器的噪聲性能進行了分析和優化,在此基礎上提出了優化相位噪聲的方案,并展示了關鍵模塊的仿真結果和整體電路相位噪聲的測試情況。結果顯示其噪聲性能達到了國內較高水平。

頻率綜合器;低相位噪聲;電荷泵;ΔΣ調制器;LC壓控振蕩器

0 引言

隨著射頻集成電路制造工藝的快速發展,基于CMOS射頻工藝的頻率綜合器可以很容易地實現數GHz的頻率時鐘信號輸出,使利用CMOS射頻工藝實現前端接收機和發射機成為可能。但隨著通信系統中頻帶資源的變大,對信號通信質量要求的提高,尤其是在射頻通信、無線廣播的接收設備中,為了更好地改善信噪比,對接收芯片中本振信號的質量提出了較高的要求。因此,研究滿足通信行業發展需求的低相位噪聲頻率綜合器已成為當下的研究熱點[1-2]。

1 延遲可調鑒相器(PFD)的設計

目前,在大多數鎖相環的設計中通常采用的都是無死區的鑒頻鑒相器,因為死區是引起雜散、相噪的主要因素之一,死區使后級壓控振蕩器的相對輸入必須將隨機相位差累積到額定值時,環路才得到有效的反饋。壓控振蕩器的輸出在這些過零點時,就會使輸出時鐘產生抖動[3]。

消除“死區”的方法為:在復位路徑上插入延時單元,從而使PFD產生的UP和DOWN信號在高電平末尾會同時為高,使電荷泵的開關不會出現因為信號時間過短而導致電荷泵無法輸出或輸入電流,從而消除該電路的死區效應。

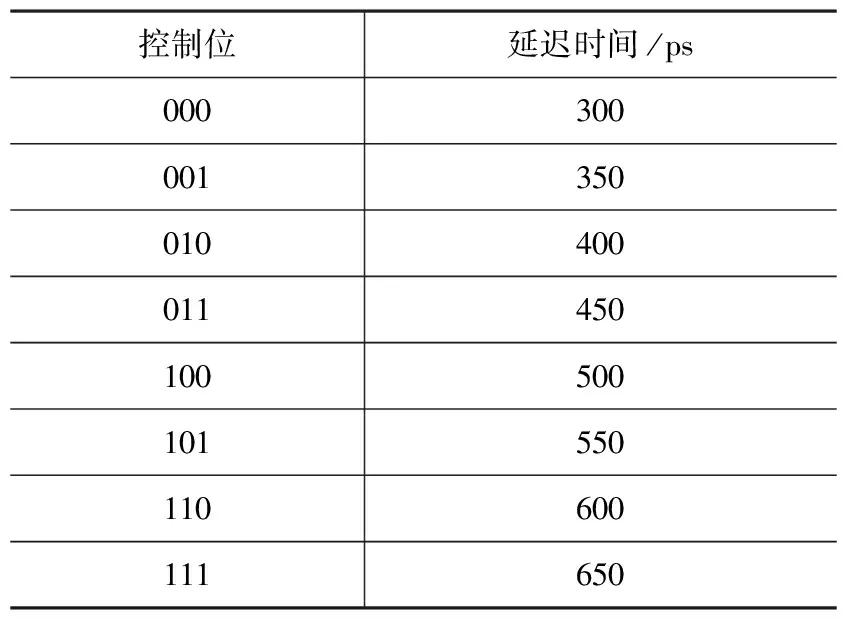

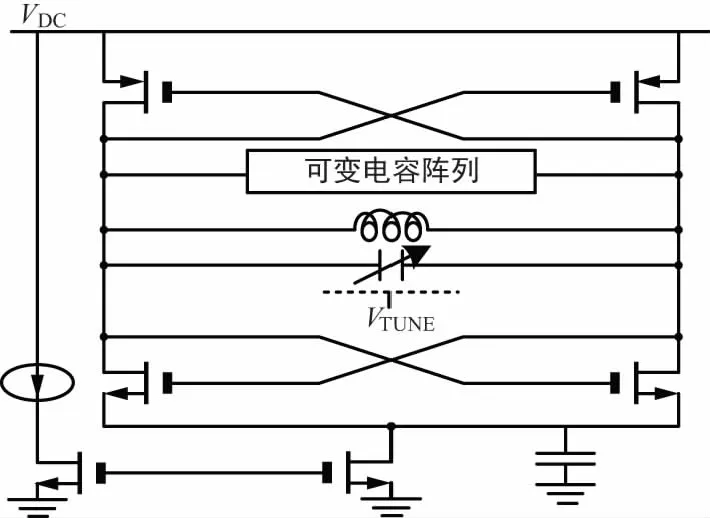

通過以上分析可知,死區是可以消除的,但PFD中復位延遲時間過長,會將后級電荷泵中(CP)的電流失配效應累積放大,即使在電荷泵完全匹配的情況下,也存在參考時鐘的饋通,在鎖相環的輸出存在著參考頻率的毛刺。而復位時間過短,則又不能做到無死區的鑒相。因此,在延遲單元設置上,本文在PFD的復位延遲設計了3 bit延遲可調,從而能夠靈活地控制延遲時間,如表1所示,具體電路如圖1所示。

表1 延遲配置

控制位延遲時間/ps000300001350010400011450100500101550110600111650

圖1 3 bit延遲可調PFD

2 自校準差分電荷泵(CP)的設計

通常電荷泵在工作時不可避免地有電荷泄漏、充放電流適配等非理想性因素存在,使得電壓存在抖動,造成輸出頻率的相位偏差,引起VCO的頻率抖動而產生噪聲[5-6]。所以,設計一個高性能的電荷泵電路對鎖相環路來說是非常重要的。

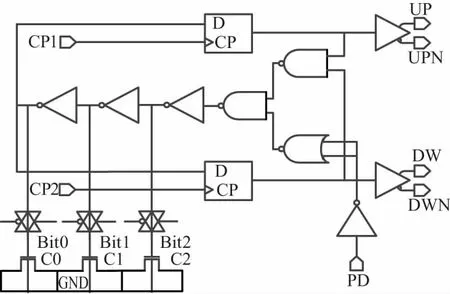

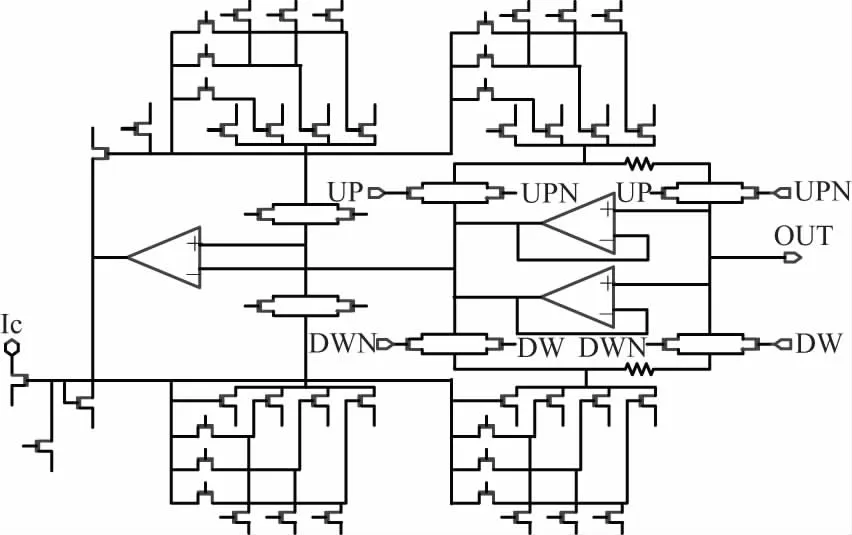

為了消除上述的電荷泄漏、充放電流適配等非理想性因素,可采用自校準電荷泵電路,其原理和電路結構如圖2所示。

由于CMOS實現的開關電流源的內阻并非無窮大,電荷泵在輸出電壓范圍較大時泵出或者泵入的電流不能完全匹配,這個電流誤差將引入雜散。自校準電路的引入可以克服這個問題,引入復制電荷泵電流支路的參考支路,把參考支路和電荷泵電流支路的輸出節點電壓作為放大器的輸入,放大器的輸出直接調節2條支路的電流偏置。這種電路可以保證電荷泵的泵出或者泵入電流的匹配特性不隨輸出電壓的改變而改變,完全由器件工藝尺寸誤差決定輸出電流的適配。

圖2 自校準電荷泵原理圖

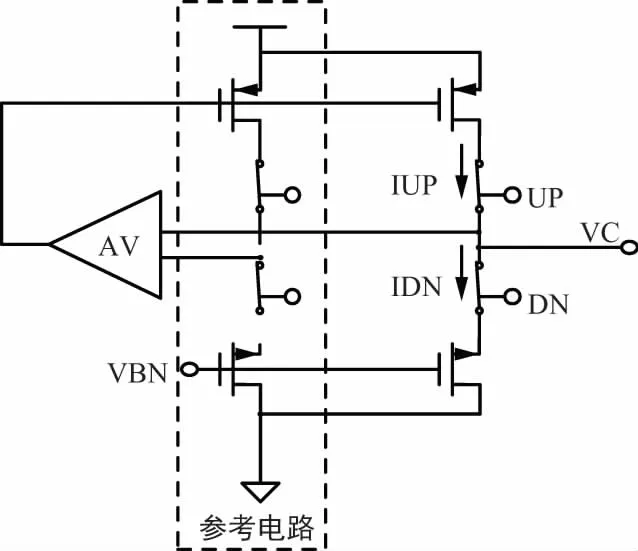

為了確保環路的穩定性,又增加跨導運算放大器,如圖3所示。在參考支路以外又增添了偏置支路,把放大器的輸出連接到偏置支路上,降低放大器這一級的增益,使反饋回路的開環等效為一級放大,則反饋回路處于無條件穩定狀態,無需進行頻率補償。改進電路的優點是在保證輸出范圍大、電流匹配性好的同時,極大地增強了電路的穩定性。

圖3 本文設計采用的自校準差分電荷泵

另外,由于電流源MP3和MN3的漏端有限寄生電容不一樣,會引起電荷共享的問題,即MP3和MN3的漏端在開關開啟和關斷時,電荷的變化量不一樣,這將導致凈電荷量流入或流出環路,最終導致環路濾波器的電壓出現紋波,惡化鎖相環的相噪[8]。為了解決這一問題,采用了差分電荷泵,如圖3所示,將差分兩端用一個單位增益放大器連接起來,使得兩邊的共模電平保持相等,兩側電壓保持恒定,也就不會產生電荷共享的問題。

本設計采用的具體電荷泵電路如圖4所示,開關管的設計采用互補式對管,降低時鐘饋通效應;單位增益運放采用了PMOS尾電流源和NMOS尾電流源兩級運放,以保持運放兩側電壓范圍的一致性,同時還增加了一些電流控制位。

圖4 電荷泵電路

3 無源濾波器的分析設計

電荷泵輸出信號包含有直流成分和高階諧波成分,其中高頻成分則是不需要的信號,這些高頻成分通常由環路低通濾波器濾除。

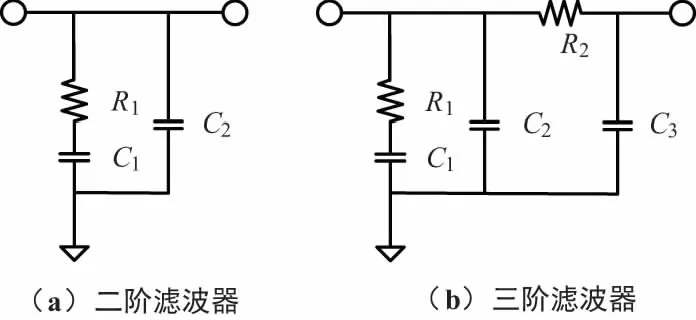

環路濾波器有2種實現方式:無源和有源,兩者具有相同的零極點位置,只是有源的在輸出增加了增益[9]。一般來講,無源濾波器的噪聲比有源濾波器的噪聲小,所以本設計采用無源濾波器,無源濾波器的常用結構如圖5所示。

圖5 環路濾波器

圖5 (a)是二階環路濾波器,它有1個零點和2個極點。其傳輸函數為:

(1)

圖5 (b)是三階環路濾波器,其傳輸函數為:

(2)

通過傳輸函數式(1)和式(2)的對比,較二階濾波器來說,三階濾波器又增加了一個高頻極點,因此環路濾波器對高頻噪聲有較好的抑制作用。

本文設計采用三階環路濾波器,在實際設計中,C1遠大于C2和C3,R1遠大于R2。

無源濾波器的噪聲主要來源于電阻的熱噪聲,一般設計中,電阻R值越小越好。因為R越小,輸出噪聲系數越小。但是R越小,則系統的相位裕度越小,系統越不穩定,而且使得系統跟蹤的速度變慢,系統帶寬變小,所以本文電路設計在滿足帶寬前提下盡量降低電阻R1和R2的值。

4 低噪聲LC型VCO設計

基于射頻收發的本振輸出頻率一般在幾GHz左右,因此VCO的振蕩頻率一般也在幾GHz,若有正交輸出的要求,需要引入高速二分頻電路,則振蕩頻率還會有一個成倍的變化。

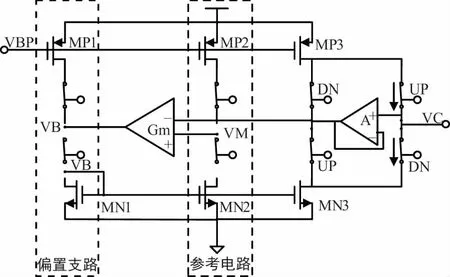

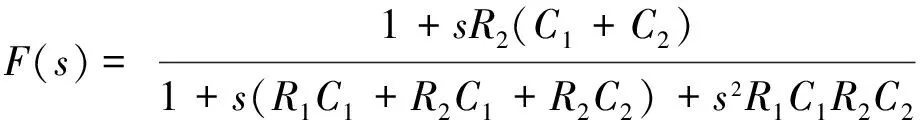

壓控振蕩器主要分為環形振蕩器和LC型振蕩器兩大類,環形振蕩器一般為多個放大器級聯反饋而成,但是由于其可實現頻段不高,而且相位噪聲比LC壓控振蕩器差,因此,在射頻收發本振的設計上,主要采用LC型壓控振蕩器。該結構主要由高Q值的電感、可變電容陣列和MOS交叉負阻管組成。常用的結構包括NMOS交叉耦合管、PMOS交叉耦合管和NMOS/PMOS互補交叉耦合管3種[10-12]。

本文采用NMOS/PMOS交叉耦合負阻振蕩電路,如圖6所示,這樣對耦合晶體管跨導的要求較低,約為LC環路寄生電阻的1.25~1.5倍即可。另外,采用該結構,可以保證電路的對稱性,能夠輸出質量較高的差分信號。

圖6 本電路采用的交叉耦合LC型VCO

LC型振蕩器的噪聲水平,主要和其中電感的Q值有很大關系,因此,在設計仿真時,通過降低電感匝數,來提高電感的Q值。此外,還采取了以下措施來降低相噪[14-17]。

措施一,通過在差分對管共源點加一個與尾電流源管并聯的大電容,來濾除二次及二次以上諧波附近的噪聲,這樣做也削弱了尾電流源管的溝道長度調制效應,使振蕩器輸出波形更加對稱。

措施二,降低振蕩器的調諧增益。由于輸出相位和頻率的變化是控制線上的噪聲所導致的結果,對于給定的噪聲幅度:

wout=w0+KVCOVcont。

(3)

由式(3)可知,輸出頻率中的噪聲正比于Kvco,所以要使Vcont上的噪聲效應減到最小,VCO的增益必須最小,這就需增加調諧曲線的數量。

措施三,在VCO版圖的設計中,LC的環路走線盡量采用高層寬金屬,以減小寄生電阻對相位噪聲的貢獻。

本文設計的VCO調諧范圍從2~4 GHz,采用3個VCO,每個VCO采用5 bit控制電容陣列,共32根調諧曲線,這樣可以將Kvco控制在20 MHz/V左右。

5 小數分頻ΔΣ調制器的分析設計

頻率綜合器必然要用到小數分頻技術,其中減少分數雜散的方法,目前較多采用的是ΔΣ技術,該技術能夠有效地將量化噪聲隨機化,低頻率段的量化噪聲推移到較高的頻率段,以提高信號帶內的信噪比[4]。

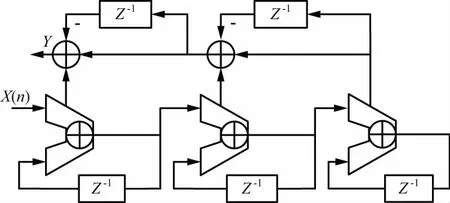

本文ΔΣ調制器采用的是基于MASH 1-1-1結構的三階調制器,如圖7所示。

圖7 典型MASH1-1-1結構

該結構簡單,主要是由累加器和延遲單元組成,由于經過了三級噪聲整形,輸出電平從-3~4,因此對相位噪聲的抑制效果好,非線性噪聲電平一般可以達到<-45 dB@300 kHz[7]。

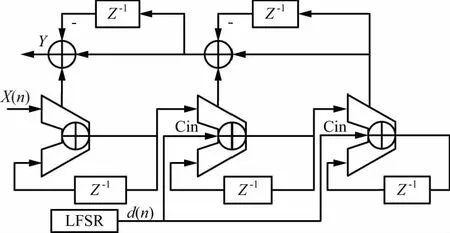

高階全數字調制器的寄存器是有限的,輸出序列還是無法避免周期性的存在,這將會導致雜散噪聲的產生,特別在輸入x(n)為一些周期性的小數時,輸出序列的周期性會更強。為了消除輸出序列的周期性,將三階調制器中的第1級累加器的進位輸入端置零,同時分別在第2級和第3級累加器的進位輸入端口輸入一個7位線性反饋移位寄存器(LFSR)產生的偽隨機序列d(n)。如圖8所示,這種偽隨機序列近似為高斯白噪聲,沒有任何能量,只會破壞輸出序列的周期性,并不會對調制器的調制功能產生影響。

圖8 帶偽隨機產生器Mash結構

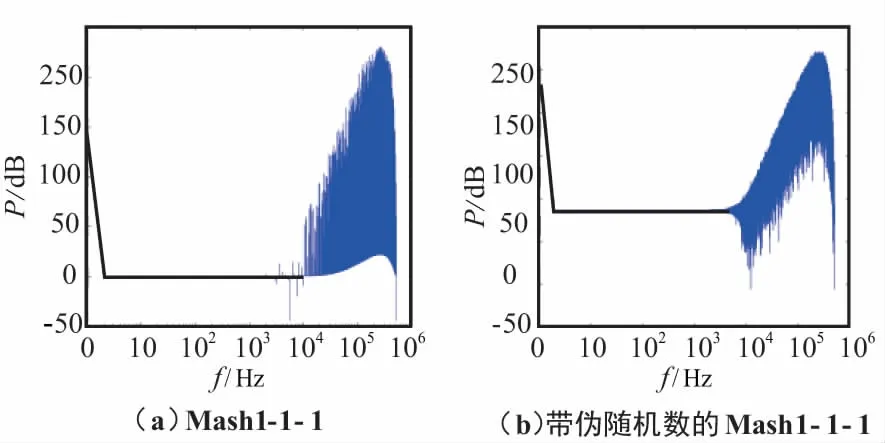

本文基于matlab對典型Mash1-1-1和帶偽隨機產生器Mash結構進行了建模仿真,仿真結果如圖9所示。

圖9 Matlab建模仿真結果

圖9(a)是典型Mash 1-1-1的仿真結果,圖9(b)是帶偽隨機產生器的仿真結果,可以明顯看到,雖然二者都實現了將低頻的小數雜散向高頻搬移,但左圖中在104頻率處雜散的能量是在70 dB左右,而右圖中在相同位置的能量是在10 dB左右,由于偽隨機數的加入削弱了雜散的能量,并且使雜散的能量更為集中。

6 頻率綜合器整體環路帶寬的分析設計

前面在降低頻率綜合器各個模塊自身噪聲方面進行了分析研究,然而整體頻率綜合器輸出頻率的相位噪聲性能不僅同各模塊的設計相關,而且嚴重依賴整個環路帶寬的選擇[13]。

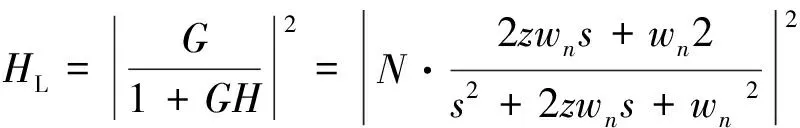

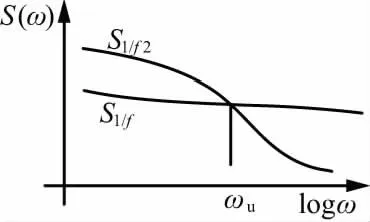

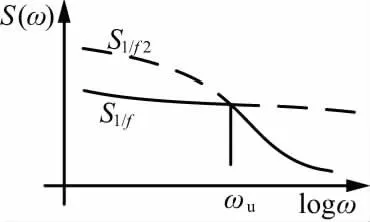

各模塊噪聲可被劃分為2類:① 電荷泵和分頻器的固有相位噪聲(具有1/f頻域特性);② VCO和濾波電阻等效的相位噪聲(具有1/f2頻域特性)。相應環路傳輸函數HL和HH分別為低通和高通函數:

(4)

(5)

2類噪聲源對輸出總噪聲的貢獻大小取決于各自到輸出傳輸函數式(4)和式(5)的帶寬。

圖10為2類噪聲源的功率密度譜,圖11為引入了環路高通和低通效應修正后的密度譜,可以看到,當帶寬正好在2根譜線交點ωu頻率處時,2根譜線交叉高出部分將能夠被抑制掉,如圖中虛線部分,這樣能進一步減弱各個模塊噪聲源所引入的相位噪聲。

圖10 2類噪聲源的 功率密度譜

圖11 環路調整后噪聲 功率密度譜

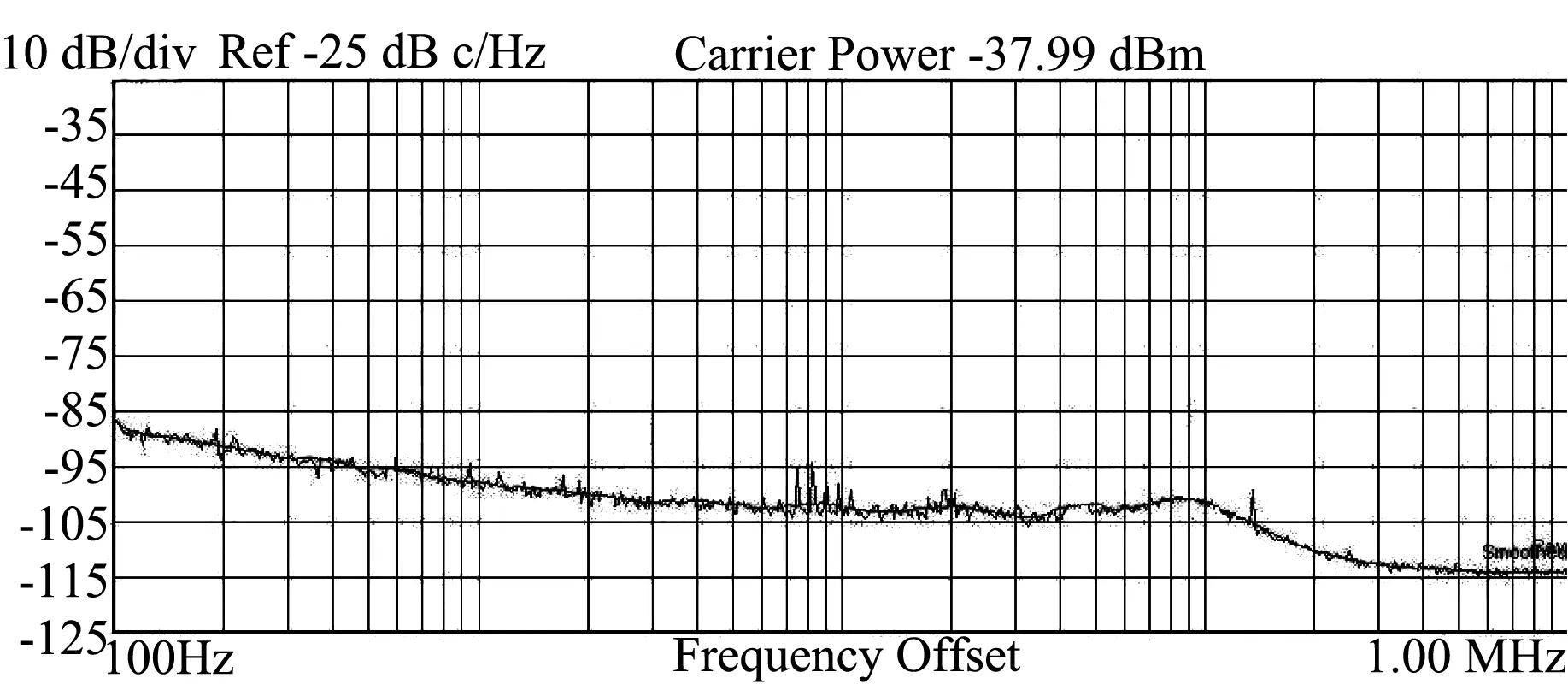

本文設計頻率綜合器,在VCO振蕩在2 GHz時,分頻輸出400 MHz,輸入鑒相頻率為3 MHz,帶寬設置在100 kHz,對輸出的相位噪聲進行了測試,結果如圖12所示。

圖12 相位噪聲測試結果圖

可以看到相位噪聲在1 kHz處達到了-97 dB,在10 kHz處達到了-102 dB,在100 kHz處達到了-101 dB,在1 MHz處達到了-115 dB,該指標達到了國內在該頻率段相噪的較好水平。

7 結束語

本文在對射頻收發器中的頻率綜合器的低噪聲設計中,對鑒相器、電荷泵、環路濾波器、LC振蕩器和小數分頻ΔΣ調制器進行了優化,并對環路帶寬進行了合理設計,仿真及測試結果表明,各模塊的噪聲性能得到了改善,整體頻率綜合器輸出頻率的噪聲性能得到了較大提高,能夠適應當前射頻收發器的應用要求。

[1] Phillip E A.CMOS模擬集成電路設計(第2版)[M].北京:電子工業出版社,2011.

[2] Sansen W M C.模擬集成電路設計精粹[M].北京:清華大學出版社,2008.

[3] 拉扎維.模擬CMOS集成電路設計[M].西安:西安交通大學出版社,2008.

[4] Pamarti S,Jansson L,Galton I.A Wideband 2.4 GHz Delta-Sigma Fraetional-N PLL with l-Mb/s In-LooP Modulation[J].IEEE Journal of Solid-State Circuits,2004,39(1):49-62.

[5] Temporit E,Albasini G,Bietti I,et al.A 700-kHz Bandwidth ΔΣ Fractional Synthesizer with Spurs Compensation and Linearization Techniq-ues for WCDMA Applications [J].IEEE Journal of Solid-State Circuits,2004,39(9):1446-1454.

[6] Swaminathan A,Wang K J,Galton I.A Wide-Bandwidth 2.4 GHz ISM Band Fractional-N PLL With Adaptive Phase Noise Cancellation [J].IEEE Journal of Solid-State Circuits,2007,42 (12):2639-2650.

[7] Meninger S E,Perrott M H.A 1-MHz Bandwidth 3.6-GHz 0.18-um CMOS Fractional-Synthesizer Utilizing a Hybrid PFD/DAC Structure for Reduced Broadband Phase Noise [J].IEEE Journal of Solid-State Circuits,2006,41(4):966-980.

[8] Hedayati H ,Khalil W ,Bakkaloglu B.A 1 MHz Bandwidth,6 GHz 0.18 um CMOS Type-I ΔΣ Fractional-N Synthesizer for WiMAX Application [J].IEEE Journal of Solid-State Circuits,2009,44(12):3244-3252.

[9] 何 捷.DVB-T 接收機中頻率綜合器的研究[D].上海:上海交通大學,2005.

[10]鄧賢進,李家胤,張 健.鎖相頻率合成器相位噪聲的精確估計與仿真[J].電路與系統學報,2006,11(5):128-131.

[11]張淑娥,王 丹.基于LTC1562的諧振器設計與實現[J].無線電工程,2011,41(11):40-42,60.

[12]劉 欣,井科學,歐陽萍.基于YIG振蕩器的寬帶頻率綜合器設計[J].無線電工程,2012,42(2):58-61.

[13]彭志華,周存麒.C波段低相噪頻率合成器設計[J].無線電工程,2012,42(3):44-46.

[14]吳俊晨,任文成,徐志平.利用PLL減小時鐘前沿抖動的研究[J].無線電工程,2013,43(2):52-54.

[15]楊 強,李棟賢.毫米波衛星通信頻段功率合成器的研究[J].無線電工程,2013,43(5):59-61.

[16]胡麗格.一種S波段寬帶小步進頻率合成器的設計與實現[J].無線電工程,2015,45(5):70-72.

[17]王戰永.基于DDS+PLL一種快速跳頻頻率合成電路的設計與實現[J].移動通信,2014,38(24):57-61,66.

Design of Low Noise Frequency Synthesizer Based on RF Transceiver Applications

QU Ming,ZHAI Yue,WANG Nan

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

The rapid development of wireless communication technology and the higher and higher carrier frequency band put higher demands on the noise performance of the frequency synthesizer in the transceiver chip.For the design of frequency synthesizers in communication transceiver system,some low noise design techniques are proposed.The power supply voltage of the design is 1.2 V,and the process is CMOS 0.13 um.The paper analyzes and optimizes the noise performance of the main components of the frequency synthesizer,including the phase detector,charge pump,LC type oscillator and the ΔΣ modulator.Based on this,the paper proposes the scheme of phase noise optimization and presents the simulation results of key modules and phase noise test results of the whole circuits.The results show that the noise performance has reached the high domestic level.

synthesizer;low phase noise;charge pump;ΔΣ modulator;LC oscillator

10.3969/j.issn.1003-3114.2017.03.19

曲 明,翟 越,王 楠.基于射頻收發應用的低噪聲頻率綜合器設計[J].無線電通信技術,2017,43(3):76-80.

[QU Ming,ZHAI Yue,WANG Nan.Design of Low Noise Frequency Synthesizer Based on RF Transceiver Applications[J].Radio Communications Technology,2017,43(3):76-80.]

2016-11-23

國家部委基金資助項目

曲 明(1982—),男,工程師,主要研究方向:模擬集成電路設計。翟 越(1989—),男,助工,主要研究方向:模擬集成電路設計。

TN911.7

A

1003-3114(2017)03-76-5