HS6L高速數據總線設計

李 震,張 鵬

(中車青島四方車輛研究所有限公司,青島 266031)

HS6L高速數據總線設計

李 震,張 鵬

(中車青島四方車輛研究所有限公司,青島 266031)

本文提出了一種高速總線的設計方法。HS6L是一種高速全雙工總線,主要應用于短距離高速數據傳輸領域。在短距離傳輸場合,相對于普通的并行總線以及串行總線,HS6L總線具有明顯的優勢。介紹了HS6L總線的幀格式和硬件組成,重點介紹了HS6L總線收發控制器的設計方法。

HS6L總線;高速總線;串行總線

0 引言

工業控制領域經常需要較短距離的高速數據傳輸,目前可應用于短距離數據傳輸的總線機制有:普通并行總線傳輸、PCI和PCI-E總線傳輸、CAN總線傳輸、RS232和RS485總線傳輸等等。本文介紹的HS6L總線是一種全雙工高速總線,由4根數據總線、2根時鐘線組成。相對于并行總線而言,HS6L總線具有更少的硬件資源消耗;相對于PCI和PCI-E而言,HS6L總線具有較低的成本,并且對系統平臺的依賴較小;相對于CAN總線、RS232、RS485總線,HS6L總線具有更高的傳輸速率。

簡要概括HS6L總線的特點如下:

1)點對點傳輸,采用全雙工的總線收發機制,每組由2根數據線、1根時鐘線組成,可取代普通的并行總線,可降低硬件設計成本。

2)單向最高傳輸速度可達240Mbps,雙向最高傳輸速度可達480Mbps。

3)在時鐘上升沿和下降沿都進行數據采集。

4)采用固定數據幀長度通訊,且數據幀長度可配置。

5)具有自檢和重發功能。

6)帶隔離功能的HS6L總線可實現不同電平之間的設備通訊,可滿足高可靠性場合的要求。

HS6L總線的主要應用領域為:1)板卡內功能模塊之間高速通訊。2)機箱內部板卡之間高速通訊。3)設備間短距離高速通訊。

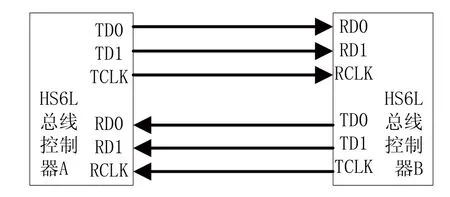

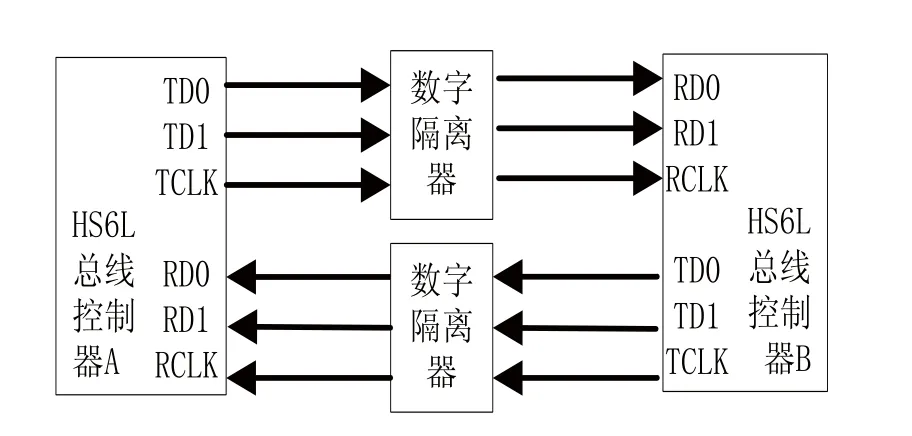

1 HS6L總線的硬件組成

HS6L總線采用4根數據總線和2根時鐘線。其硬件構成框圖如圖1所示。帶隔離功能的HS6L總線系統框圖如圖2所示。帶隔離功能的HS6L總線是在2路通訊線中加入數字隔離器,以滿足不同電平標準的設備之間的數據通訊,同時這種總線可以應對工業現場對高可靠性的要求。

在數字隔離器輸出端口處需要加總線匹配電阻來降低接收端信號的過沖,進一步提高信號的質量。

系統運行在全雙工模式,同一時刻既可以發送也可以接收,在總線空閑時,數字隔離器輸出高阻態。總線工作時各個節點使用相同的波特率,接收端采用2倍通訊頻率進行信號采集。

圖1 HS6L總線框圖

圖2 HS6L隔離總線框圖

2 HS6L總線的通訊協議

HS6L總線的幀格式如表1所示。

表1 HS6L總線幀格式

幀頭標示符有3個作用:1)通知接收端準備接收,2)接收端通過接收幀頭標示符來精確確定可靠的采樣間隔,3)如果總線上有兩個節點同時嘗試發送,可通過總線沖突自檢機制,在幀頭標識符發送階段進行沖突檢測。幀頭標示符由7~10個0x7E組成。

幀頭標示符結束后緊跟著一個4位的控制位。控制位的第0~1位為控制信息位。控制信息標示有兩種,表示的意義如下:

01:主機發出的數據幀標示。數據幀標示后緊跟接收節點的地址(4位)和本幀傳輸的字長度(4位)。

10:從機發出的響應幀標示。響應幀標示后緊跟接收節點自身的地址(4位)和本次接收的字長度(4位)。

控制位的第2~3位為發送個數計數器,在正常情況下,針對同一個主機(發送節點),每成功發送一幀數據幀,計數器中的計數加1。如果主機在發送一個數據幀后在規定時間內沒有收到從機(接收節點)的響應幀(響應超時),主機將在規定時間之后重新發送本次數據幀,此時計數器中的計數值保持不變。

傳輸內容及通訊發送的數據,只在數據幀中體現,響應幀中沒有傳輸內容。

CRC校驗為數據幀中控制信息和傳輸內容的CRC校驗。響應幀中CRC校驗為控制信息的CRC校驗。

如果從機接收到的數據幀CRC校驗正確,將在規定時間內自動發送正常響應幀。如果CRC校驗錯誤,從機也會在規定時間自動發送響應幀,但是響應幀中的CRC校驗將為控制信息CRC的校驗加1。主機發現接收的校驗幀CRC錯誤,會自動重發上一幀的數據幀。

結束符為本次通訊的結束標志。由一個0x7E組成。主機在發送完結束符以后,必須在發送頻率一個周期之內,將發送端口置為高阻態。當總線上的其他節點接收到通訊結束符以后,可以在一個通信時鐘周期之后搶占總線。

3 HS6L總線收發控制器設計

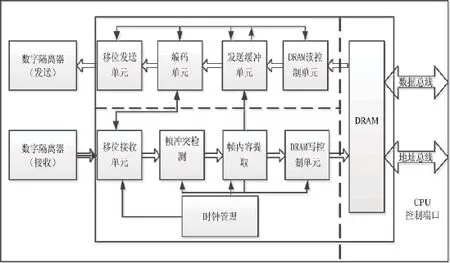

這里使用FPGA進行控制器的設計,HS6L總線控制器的組成框圖如圖3所示。

從圖中可以看出控制器主要由3個部分組成:發送部分、接收部分和雙口RAM(DRAM)。DRAM為HS6L總線和控制端口之間提供緩沖;發送部分提供從DRAM中讀取發送內容,轉換成HS6L總線可發送的編碼,并通過數字隔離器發送出去;接收部分實時監測HS6L總線上存在的數據,作為節點接收的情況下,提供接收功能,在節點發送的情況下,提供幀沖突監測功能。下面分別對各個部分展開說明。

3.1 發送部分

發送部分由移位發送單元、編碼單元、發送緩沖單元和DRAM讀控制單元組成。

DRAM讀控制單元通過內部并行總線實時監視發送指令存儲器,一旦收到發送指令,則立即將發送數據從DRAM中讀取出來,并傳遞給發送緩沖單元。由于DRAM控制單元采用系統內部的高速并行總線,因此對DRAM的寫速度非常快。

圖3 HS6L總線控制器框圖

發送緩沖單元的核心由一個大小為64個字的內存組成,這個單元的作用為接收到DRAM中的數據以后,根據數據的長度和內容,得到幀頭的控制信息、幀內容和幀CRC的校驗和,并將這些信息以32位的形式存儲到內存中,以提供下一個接口單元使用。發送緩沖單元中的內容會一直保持有效,一直到接收控制器收到本次發送幀對應的響應幀為止。如果CPU控制器控制端口強行復位HS6L總線控制器,發送緩沖單元中的內容也將失效。

發送緩沖單元將發送內容準備好以后會將需要發送的內容傳給編碼單元,編碼單元會將需要發送的數據由32位轉換成2位的形式,并且在數據幀的頭部添加幀頭標示符和幀尾結束符。同時編碼單元接收從移位接收單元發送過來的使能信號,這個使能信號在檢測到HS6L總線空閑的時候有效。當編碼單元內有有效信息時,一旦使能信號有效,編碼單元將立即將發送數據發給移位發送單元。

移位發送單元接收由編碼單元傳遞過來處理好的數據,通過2位數據總線發送到數字隔離器的接口,開始發送。當發送結束的時候,移位發送單元會立即將數字隔離器(發送)置為高阻態。

3.2 接收部分

接收部分由移位接收單元、幀沖突檢測單元、幀內容提取單元和DRAM寫控制單元組成。

接收部分一直處于工作狀態。當控制器發送數據的時候,接收部分會不斷檢測總線上的實際信號,一旦發現總線沖突,則立即通知移位發送單元將總線端口置為高阻態,并在總線空閑的時候重新發送。當控制器不發送數據的時候,接收部分一直接收來自總線的數據。

移位接收單元使用2倍HS6L總線頻率進行采樣,從采樣數據中提取出可靠的采樣數據并且傳遞給下一個環節。移位接收單元通過幀頭標示符進行準確的采樣定位,并使用定位結果對此幀剩下部分進行接收。一旦移位接收單元檢測到幀頭標示符有效,就會立即將接收的結果發送給幀沖突檢測單元。

幀沖突檢測單元只在此控制器發送數據的時候有效,一旦檢測到發送的數據和總線上其他節點有沖突,幀沖突檢測單元會在一個系統時鐘之后發命令給移位發送單元和發送緩沖單元,立刻禁止輸出。如果控制器不發送數據,幀沖突檢測單元無效,并直接將數據傳遞給幀內容提取單元。

幀內容提取單元負責將接收到的數據進行ID檢驗和CRC校驗,如果CRC校驗失敗,幀內容提取單元會通知發送緩沖單元發送CRC錯誤響應幀。如果ID校驗失敗(接收到的數據幀不是發給本節點),幀內容提取單元會自動將該幀拋棄掉。如果ID和CRC校驗成功,則將接收到的2位帶寬數據轉換成32位數據,并將轉換后的數據傳遞給DRAM控制單元。

DRAM寫控制單元將幀內容提取單元發送過來的數據內容寫入DRAM內存單元。CPU控制端口可以通過并行總線高速訪問DRAM內接收到的數據。

4 結束語

本文介紹了HS6L總線的設計方案。實踐證明在短距離高速數據傳輸的情況下,HS6L總線具有很大優勢。在保證系統可靠性的同時,可以保證較高的通信速率。同時HS6L總線采用4根數據線+2根時鐘線的結構,在機箱背板的應用場合可以極大的降低硬件的設計難度。在短距離設備間使用線纜通信的場合,可以使用4芯屏蔽線作為理想的傳輸線纜,屏蔽層可作為地線,且具有很好的電磁兼容性能。

[1] Dean J. Ghemawat S. MapReduce:Simplified data processing on large clusters[J].ACM Communication,2008,51(1):107-113.

[2] Lubomir F B, Show A C.Operation System Principles[M].New Jersey: Prentice Hall.2003.

[3] Kaashoek F,Morris R,Mao Y.Optimizing MapReduce for multicore architectures[J].MIT Computer Science and Artificial Intelligence Laboratory:Technical Report MIT-CSAILTR-2010-020,2010.

Design of HS6L high speed data bus

LI Zhen, ZHANG Peng

TN92

:A

1009-0134(2017)03-0142-03

2016-12-26

李震(1986 -),男,工程師,碩士,主要從事動車組列車車載設備的研究。