一種LVDS接口的液晶顯示驅動設計

徐巧玉,李坤鵬,王軍委,王紅梅

一種LVDS接口的液晶顯示驅動設計

徐巧玉1,李坤鵬1,王軍委2,王紅梅1

(1.河南科技大學機電工程學院,河南洛陽471003;2.洛陽銀杏科技有限公司,河南洛陽471003)

為了解決目前嵌入式液晶顯示技術中存在的顯示驅動支持分辨率低、數據更新慢及控制靈活性差等問題,設計了一種基于現場可編程門陣列(FPGA)的LVDS接口的液晶顯示驅動。對數據緩存技術中數據讀寫控制等關鍵問題進行了分析,研究了對液晶顯示驅動時序和低電壓差分信號(LVDS)傳輸時序。基于FPGA構建緩存控制模塊和顯示控制模塊,實現數據快速更新及LVDS接口液晶顯示屏的顯示。通過QuartusⅡ軟件,對緩存控制模塊控制時序進行了采樣分析驗證。驗證結果表明:第二代雙倍數據率同步動態隨機存取存儲器(DDR2 SDRAM)在166 MHz下工作,LVDS接口液晶顯示屏分辨率為1 024 pixel×768 pixel,位寬為16 bit時,數據更新率達82 MHz,且控制靈活,能夠滿足目前對液晶顯示驅動的需求。

現場可編程門陣列;第二代雙倍數據率;低電壓差分信號;顯示驅動

0 引言

近年來,隨著嵌入式技術的快速發展,嵌入式顯示終端的應用越來越廣泛。應用領域的多樣化以及高分辨率液晶顯示的需求,對嵌入式液晶顯示技術的靈活性以及高分辨率提出了更高要求。

目前,嵌入式液晶顯示實現方法主要包括單端并行傳輸方式和低電壓差分信號(low-voltage differential signaling,LVDS)差分傳輸方式。其中,單端并行傳輸方式簡單易用,在嵌入式顯示設備中廣泛運用。文獻[1-2]采用單端并行數據傳輸方式,以基于現場可編程門陣列(field-programmable gate array,FPGA)作為液晶顯示驅動器,實現了多分辨率顯示。該方法邏輯簡單,操作靈活,但在傳輸高頻信號時,信號串擾和噪聲干擾等問題明顯,因此不適用于高分辨率顯示。LVDS傳輸方式以其高速穩定的特性被推廣。文獻[3-4]采用LVDS傳輸方式,通過LVDS專用芯片實現并行數據與串行差分信號的轉換,從而驅動液晶顯示。該方法具有很好的抗干擾及串擾能力[5],但專用芯片一般適用于常見分辨率及時序固定的應用場合,對于特殊分辨率的液晶顯示應用場合,其應用受到一定的限制。

針對上述問題,本文提出了一種基于FPGA的LVDS接口的液晶顯示驅動設計。該方案以第二代雙倍數據率同步動態隨機存取存儲器(double-data-rate two synchronous dynamic random access memory,DDR2 SDRAM)作為數據緩存單元,基于FPGA構建緩存控制模塊,通過對第二代雙倍數據率(doubledata-rate two,DDR2)大容量數據緩存器的控制,實現數據的快速更新和顯示數據的及時傳輸。基于FPGA構建顯示驅動模塊,產生相應的顯示時序并完成LVDS接口時序的轉換,從而實現圖像的顯示。該方案同時擁有FPGA的靈活性及LVDS傳輸的穩定性,可以很好地解決上述問題。

1 系統設計及工作原理

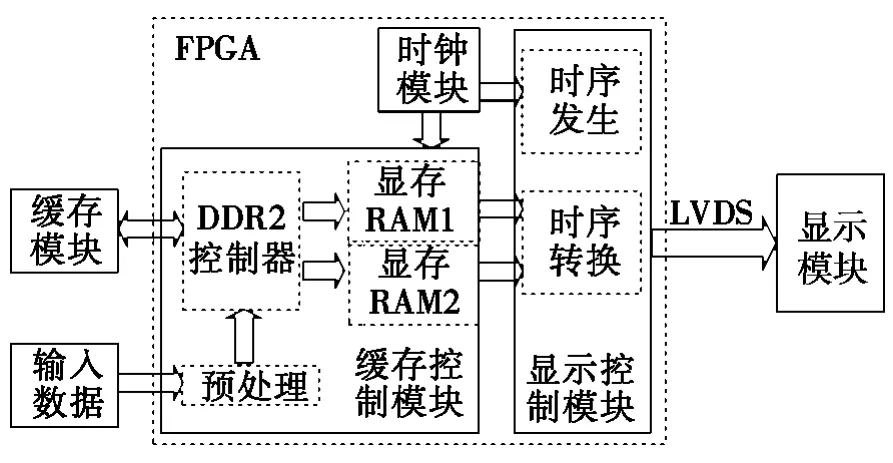

本系統總體設計方案如圖1所示。系統主要包括:時鐘模塊、緩存模塊、緩存控制模塊、顯示控制模塊和顯示模塊(即液晶顯示屏)等。時鐘模塊對輸入的時鐘信號進行倍頻和分頻等處理,為系統各模塊提供工作時鐘。緩存模塊為大容量數據存儲設備,本設計采用DDR2 SDRAM存儲器完成輸入圖像數據的暫存。緩存控制模塊通過協調緩存模塊與顯示控制模塊之間的數據傳輸,完成對輸入數據和顯示數據的處理和控制,實現更新數據的快速寫入和顯示數據的及時讀出,保證圖像的實時顯示。顯示控制模塊包括用于產生與像素信息相對應的時序發生模塊以及依據LVDS時序進行轉換的時序轉換模塊,最終實現LVDS信號輸出以及圖像數據的顯示。

外部輸入數據首先進入系統的預處理模塊,在該模塊中完成數據的預處理操作。DDR2控制器控制數據的寫入與讀出,在沒有收到讀請求時則進行寫操作,將數據從預處理模塊中寫入緩存模塊,在顯示的準備階段,從緩存模塊中讀出數據到顯存RAM1和顯存RAM2中。控制著兩個隨機存取存儲器(random access memory,RAM)的乒乓操作將數據送入顯示控制模塊。顯示控制模塊對顯示數據及時序控制信號進行處理并轉換為LVDS顯示時序,通過LVDS接口傳輸到液晶顯示屏顯示。數據緩存控制模塊和顯示控制模塊為本設計的核心部分。

圖1 系統總體設計方案

2 基于FPGA的數據緩存控制模塊設計

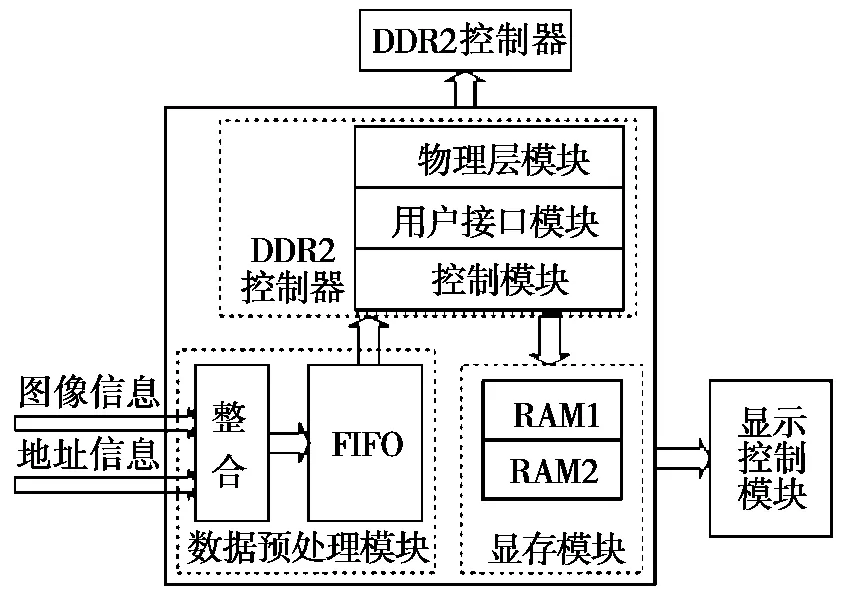

數據緩存控制模塊結構如圖2所示。該模塊由數據預處理模塊、顯存模塊及DDR2控制器組成,主要完成對輸入數據存儲及顯示圖像數據讀取的協調控制。

2.1 數據預處理模塊

數據預處理包括數據的整合及緩存。由于輸入數據與DDR2存儲數據速率不匹配,因此需對外部輸入數據進行緩存處理。進入系統的數據包含圖像信息及地址信息,并且兩者一一對應,為了避免圖像信息與地址信息不對應而導致的顯示錯誤等問題,在緩存處理之前對數據進行整合處理[6]。將數據和地址鎖存之后整合為一個數高位地址低位數據的多位數據,從而避免出現顯示圖像和顯示地址不同步的問題。合并之后的多位數據存入數據緩存先入先出隊列(first input first output,FIFO)中,等待被寫入緩存模塊。

2.2 顯存模塊

顯存模塊包含兩個單口RAM,顯示過程中,數據從DDR2讀出。為了匹配速率先進入到顯存模塊,該模塊的每個RAM深度可以存儲一行數據,位寬為16 bit,液晶顯示屏顯示時讀取其中一個RAM的同時,對另一個RAM進行數據填充,兩個RAM乒乓讀寫實現數據連續輸出。

2.3 DDR2控制器

DDR2控制器為緩存控制模塊的核心部分,包括物理層模塊、用戶接口模塊和控制模塊。物理層模塊對用戶的訪問地址和指令進行解釋和匹配。用戶接口模塊在控制信號的控制下接收和存儲用戶的數據、命令和地址等信息。控制模塊在系統正常工作期間,為用戶接口模塊和物理層模塊提供相應的控制信號,并為系統提供控制器狀態指示信號[7]。本文設計的DDR2驅動器采用Altera公司的IP核,其已包含物理層模塊和用戶接口模塊,本控制器的設計主要完成控制模塊的構建,實現對DDR2的讀寫控制。DDR2控制模塊主要完成對DDR2的初始參數配置、刷新以及讀寫操作等控制,其中DDR2的讀寫控制為本模塊的核心。

圖2 數據緩存控制模塊結構

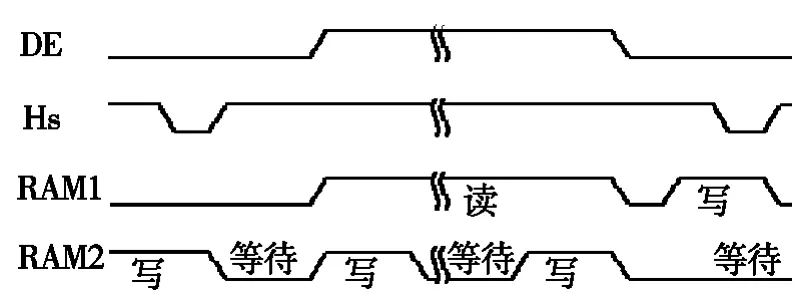

液晶顯示屏在每個顯示使能期間要求數據連續輸出,不允許數據中斷,因此對DDR2的讀取操作設置為最高優先級,在整個DDR2的控制模塊中都以數據的讀取控制為中心進行設計。每一幀顯示中,第一個顯示使能信號DE使能區開始向液晶屏傳輸顯示數據,需提前從DDR2讀出數據寫入顯存RAM1和RAM2,第一個DE使能區讀出RAM1的數據送往液晶顯示屏,顯示完畢之后立即從DDR2讀取數據寫入RAM1中。此時采用分段讀取方式,每讀取256個數據設置一次等待,再進行下次讀取,直至讀取完一行數據。每段等待區間為DDR2的寫操作時間,此設計縮短了寫DDR2的等待時間,從而有效地緩解了不能及時處理高速輸入的數據而導致數據丟失的問題,提高了數據更新率。在第二個DE使能區對RAM2進行操作,操作過程與RAM1相同。依次交替讀寫兩個RAM的數據完成圖像顯示。RAM讀寫操作時序如圖3所示。圖3中,DE為顯示使能信號,Hs為行同步信號。

為了減少DDR2帶寬的浪費,提高數據更新率,在RAM的讀寫操作中各設置一個計數器,每當RAM讀寫完成一次計數器加1,當累加至列像素點值時計數器清零,表明一幀數據顯示完畢,RAM進入等待狀態直至開始下一幀數據的顯示。此設計在一幀圖像顯示完畢之后不再對DDR2進行讀操作,以節省DDR2的帶寬,增加DDR2的寫操作時間,從而提高數據更新率。DDR2的刷新操作設計在固定的時間執行,每一幀的前N個場周期設置為刷新時間(N根據液晶顯示屏分辨率調整),經過計算,此設計可以保證在64 ms內完成對DDR2所有Bank的刷新,同時也避免刷新操作與讀寫操作發生沖突。

圖3 RAM讀寫操作時序

3 基于FPGA的顯示控制模塊設計

顯示控制模塊主要包括時序發生模塊和時序轉換模塊,以實現輸入數據與顯示時序的整合,并最終完成時序的轉換。其中,時序發生模塊實現液晶顯示時序的發生,時序轉換模塊完成顯示數據的調整,并將液晶顯示時序信號及數據信號轉換為LVDS傳輸格式。

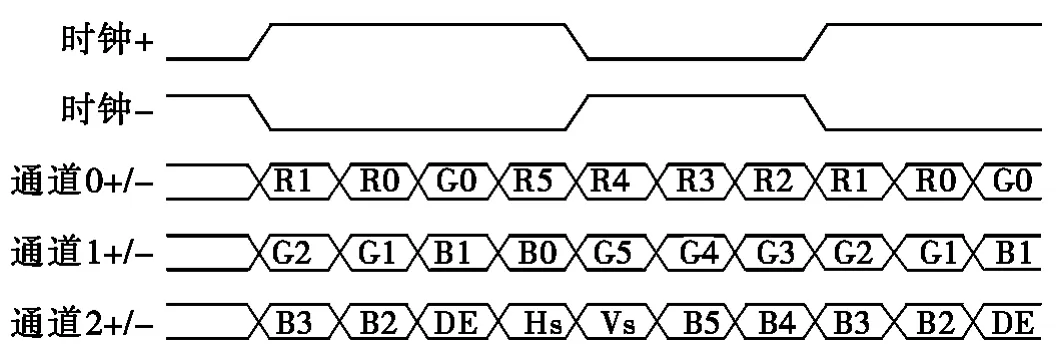

3.1 LVDS接口時序

本設計采用單路6 bit的LVDS接口實現數據傳輸,傳輸接口包含3路差分數據通道和1路差分時鐘通道。LVDS接口信號取消單端并行傳輸方式中獨立的控制信號線,將RGB圖像數據和控制信號重新采樣編碼,并通過3路差分數據通道傳輸,具有較強的抗干擾能力[8]。控制信號包括行同步信號Hs、場同步信號Vs以及顯示使能信號DE。數據信號采用單基色6位,共18位RGB數據的格式。LVDS傳輸時序如圖4所示。通道0和通道1傳輸RGB數據,通道2除了傳輸剩余的RGB數據以外還要傳輸控制信號,3路差分數據通道同時傳輸,每一個時鐘完成7次移位,實現21位數據傳輸。

3.2 時序發生器設計

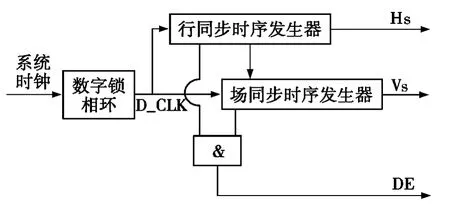

時序發生模塊主要產生液晶顯示時序信號,包括像素時鐘信號D_CLK、行同步信號Hs、場同步信號Vs、顯示使能信號DE和RGB數據信號[9]。利用邏輯編程方法產生行場掃描時序是一個發展方向。此方法電路簡單、功能強、修改方便、可靠性高,只需在代碼中修改一些時序參數就能產生任意時序波形,可以支持各種接口時序要求的液晶顯示屏[10]。時序發生模塊原理如圖5所示。

圖4 LVDS傳輸時序圖

行、場同步信號包含Sync、Front Porch、Active Video、Back Porch等信號段[11]。設計時序發生器時,分別設置兩個計數器作為行、場同步信號的基準。通過FPGA內部鎖相環對輸入的時鐘信號進行倍頻獲得像素時鐘,在像素時鐘下對行計數器計數,根據液晶顯示時序標準,行計數器累加至行像素點值時,行計數器清零并循環計數。行同步信號在行sync區間時,使行同步信號置為低,其他區間行同步信號置為高。場計數器在行同步信號下累加到列像素點值后,場計數器清零并循環計數,作為場同步信號的基準。場同步信號在場Sync區間時,使場同步信號置為低,其余時間置為高,此區間類似于行同步信號。根據時序標準,DE信號僅在行、場信號的Active Video重疊區域置為高時,開啟顯示使能,其他時間關閉顯示使能。

圖5 時序發生模塊原理圖

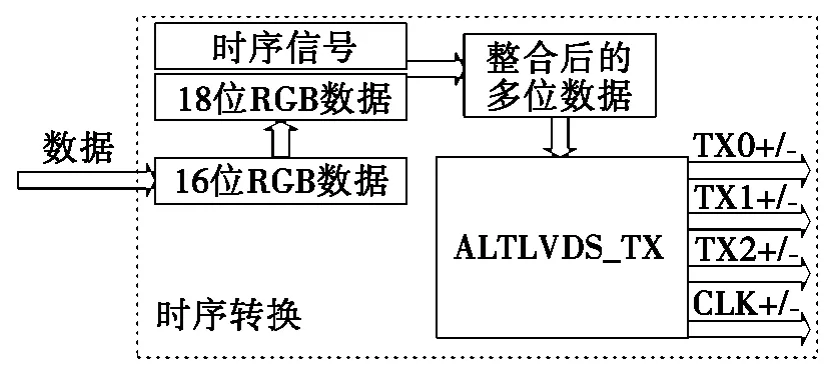

3.3 時序轉換設計

圖6 時序轉換模塊

實現LVDS信號輸出有兩種處理方式:一種是選用LVDS轉換芯片;另一種是選用支持LVDS電平標準的FPGA,既可省去LVDS轉換芯片,又可降低系統的復雜度。考慮到該設計要兼容多種分辨率液晶顯示屏,單一的LVDS轉換芯片不能滿足需求,因此采用第二種方案,以FPGA作為LVDS轉換芯片。時序轉換模塊如圖6所示。

本文設計的緩存模塊與輸入系統的圖像數據位寬均為16 bit,而液晶顯示屏接收的數據位寬為18 bit,在對數據格式進行轉換時,既要保證數據的精度也要保證系統的數據傳輸速率。565結構的16位數據轉換為666結構的18位數據,R(紅)和B(藍)兩個基色的最低位各增加一位,并將最高位數據賦給最低位,此方法在不增加過多運算的情況下,最大限度地保證了數據精度[12]。在時序轉換時,輸入的數據包括數據和液晶顯示時序控制信號,在進行時序轉換之前需對數據進行整合。在像素時鐘下同時對3個控制信號進行采樣,并與轉換后的RGB數據合并為一個多位數據,高位至低位依次為顯示使能信號DE、行同步信號Hs、場同步信號Vs和18位RGB數據,共21位。

ALTLVDS_TX的輸入端接入轉換后的多位數據及像素時鐘,輸出為3路差分數據信號和1路差分時鐘信號。在并轉串后會將數據重新排列,輸入的21位數據分為3通道7 bit輸出,高7位為一組,中間7位為一組,低7位為一組。為了實現每個通道在一個時鐘輸出7位數據,ALTLVDS_TX中的鎖相環根據輸出與輸入的速率比,計算出倍頻后的時鐘為像素時鐘×7。倍頻后的時鐘為移位時鐘,第一個移位時鐘輸出每組的最高位數據,第二個移位時鐘輸出每組的次高位數據,依次進行至輸出整個數據。

4 實驗結果與分析

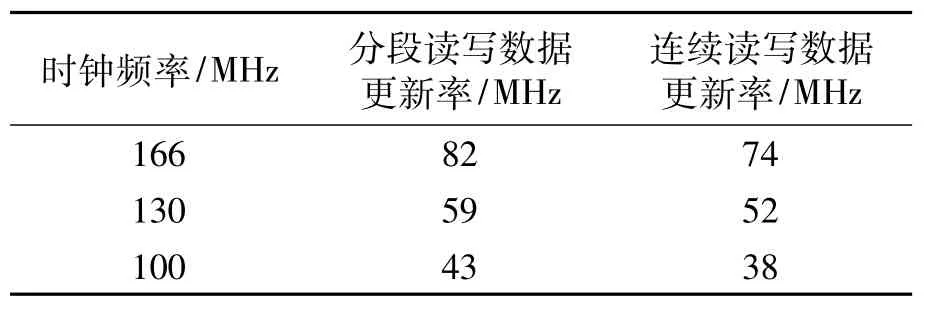

數據更新率是顯示性能的關鍵參數,影響數據更新率的因素主要有DDR2的工作時鐘及讀寫操作控制。為了驗證系統性能,以本顯示驅動器為實驗平臺進行實驗驗證。顯示驅動器是型號為EP4CE15F23C8N的FPGA,數據緩存器為400 MHz的DDR2存儲器,顯示裝置為1 024 pixel×768 pixel分辨率的具有LVDS接口的液晶顯示屏。該FPGA的DDR2驅動時鐘最高輸出為166 MHz,因此將此時鐘作為最高測試時鐘。利用QuartusII軟件中的SignalTap II Logic Analyzer工具對DDR2的讀寫過程進行采樣分析,本文設計采用的分段讀寫方式,使得讀寫交替的時間縮短,輸入數據的等待時間減小,可最大限度利用總線帶寬,提高數據更新率。

利用發送一幀數據的時間測算數據更新率,每發送完一幀數據計時信號取反,根據計時信號計算數據更新率,在同一實驗平臺分別對分段讀寫模式及傳統的連續讀寫模式進行數據更新率測試。測試3組不同時鐘頻率下的實驗數據,測試數據如表1所示。從表1的測試結果可以看到:相對于普通的連續讀寫方式,本文設計的分段讀寫具有更好的數據更新率。

表1 數據更新率測試數據

5 結論

本文設計的基于FPGA的LVDS接口顯示屏驅動,圖像數據更新率達到了高清屏的顯示需求,并且LVDS接口使得數據傳輸的抗干擾能力更強,采用FPGA進行邏輯編程使得設計控制靈活。此設計能夠滿足目前對液晶顯示驅動的需求,與傳統的顯示驅動模式相比,具有更好的實用價值。

[1]程明,肖祖勝.基于FPGA的TFT-LCD顯示驅動設計[J].液晶與顯示,2009,24(2):228-231.

[2]張超建,王厚軍.基于FPGA的TFT-LCD液晶顯示模塊設計[J].中國測試,2010,36(5):73-75.

[3]董春雷,王康平,陳威,等.LVDS技術在LCD數據傳輸中的應用[J].電子技術,2011,38(2):48-49.

[4]劉杰,程松華,張永棟,等.基于Mini-LVDS技術的TFT-LCD時序控制器的設計[J].液晶與顯示,2014,29(2): 238-244.

[5]潘子升,苗繪玲.時序控制器TCON的研究與設計[J].電子設計工程,2011,19(3):67-70.

[6]梁皓東,張國平.基于ARM9+FPGA的便攜式視頻展示臺的設計[J].電視技術,2014,38(3):60-63.

[7]陳建軍,金強寧,章鵬,等.基于FPGA的TFT液晶顯示時序控制器設計[J].液晶與顯示,2015,30(4):647-654.

[8]陳俊,唐小琦,周會成,等.基于FPGA的TFT大屏幕液晶顯示控制器設計[J].組合機床與自動化加工技術,2014(3):13-15.

[9]薛家祥,黃澤林,沈棟,等.TFT-LCD驅動中SDRAM控制器的仲裁器設計[J].液晶與顯示,2013,28(6):877-882.

[10]劉亮.特定需求液晶顯示控制器的設計實現[J].液晶與顯示,2015,30(1):109-113.

[11]王軍,張福弟,王磊,等.基于STM32的R61581驅動液晶屏顯示方法研究[J].液晶與顯示,2016,31(1):93-96.

[12]張斌,解宇,劉陳曦,等.基于液晶顯示屏的低功耗驅動技術[J].液晶與顯示,2016,31(3):290-294.

TN27

A

1672-6871(2017)05-0016-04

10.15926/j.cnki.issn1672-6871.2017.05.004

國家自然科學基金項目(51205108);河南省高等學校重點科研基金項目(15A535001)

徐巧玉(1979-),女,河南洛陽人,副教授,博士,碩士生導師,主要研究方向為嵌入式系統、機器視覺、智能測試技術及儀器.

2016-09-07