一種S波段高線性度下變頻模塊的設計

閆 超,趙家敏,姚武生

(中國電子科技集團公司第三十八研究所,合肥 230088)

一種S波段高線性度下變頻模塊的設計

閆 超,趙家敏,姚武生

(中國電子科技集團公司第三十八研究所,合肥 230088)

描述了一種應用于S波段接收通道的高線性度下變頻模塊設計,針對模塊的增益、線性度、雜諧波抑制等關鍵技術指標進行了詳細的理論和仿真分析,并硬件實現了該模塊。該模塊主要采用SMD器件,包括有源混頻器、高OIP3放大器和LC濾波器等。測試結果顯示,模塊增益為21 dB,雜諧波抑制度大于65 dBc,對特定頻點的抑制度大于40 dBc,IIP3大于24 dBm,表明該模塊滿足指標要求,能夠充分適應高性能接收通道的應用要求。

下變頻模塊;增益;線性度;雜諧波抑制

0 引 言

現代通信、雷達接收機大多采用超外差接收體制,下變頻器是超外差接收機的關鍵組成部分。下變頻器將適于傳輸的射頻信號變換為較低的頻率進行處理。下變頻器的性能直接影響到接收機的性能指標[1],而其中的線性度、雜諧波抑制度、通道增益則是下變頻模塊的關鍵指標。

本文介紹了一種高線性度S波段下變頻模塊,模塊將S波段射頻信號變換至260~460 MHz中頻,且具有高線性度、較好的雜諧波抑制度等特點。文章重點分析了關鍵指標的電路實現方法,并進行了測試,結果表明模塊的性能完全滿足指標要求。

1 下變頻模塊技術要求

S波段下變頻模塊的主要技術指標:

(1) 中頻:260~460 MHz;

(2) 增益:G≥17 dB;

(3) IIP3:≥24 dBm(增益G=16 dB時測試);

(4) 雜諧波抑制度:≥60 dBc;

(5) 中頻抑制:≥38 dBc(輸出頻率為220 MHz和500 MHz時)。

2 電路結構與設計方案

2.1 電路結構

下變頻模塊主要由低通濾波器、帶通濾波器、功率合成/功分器、混頻器、數控衰減器、放大器、耦合器和功率檢測電路構成,電路結構示意圖如圖1所示。射頻信號經低通濾波器濾除帶外噪聲和干擾后進入混頻器。混頻器將射頻信號下混頻至260~460 MHz的中頻,再經過一級低通濾波器濾除諧波及雜散信號。中頻信號通過功分器將功率一分為二,二路分別放大再合成,以提高輸出功率。最后將已放大的中頻信號進一步濾波后輸出,模塊內的功率電路檢測輸出功率大小。系統監控根據輸出功率的大小控制數控衰減器的衰減碼,從而調節電路的增益。

圖1 電路結構示意圖

2.2 關鍵技術指標設計分析

2.2.1 線性度、增益設計方案

在射頻電路設計中,通常采用IP3(third-order intercept point,三階交調截取點)指標來衡量系統的線性度。其定義為系統的三階非線性輸出與一階線性輸出相等時的輸入或輸出功率,分別被稱為輸入三階交調截取點IIP3(input IP3)和輸出三階交調截取點OIP3(Output IP3)。[2]

設一個非線性系統的傳輸函數為

(1)

其中k1、k2、k3分別為系統的電壓增益、二階、三階非線性項系數。當同時輸入兩個頻率相近的信號Acosω1t、Acosω2t時,系統將產生多個不屬于輸入信號諧波的頻率分量,即為兩個信號的交調分量。

(2)

二階交調項為

(3)

三階交調項為

(4)

由式(2)、(4)可知,基頻與信號幅度A成比例增加,而三階交調項與A3成比例增加。所以,隨著輸入信號幅度的增加,基頻與三階交調項必相交于一點,該點即為三階交調點[3],如圖2和式(5)所示,其中G為系統增益。

(5)

圖2 三階交調截取點示意圖

由上述理論可知,在射頻電路中,非線性的有源器件對系統的線性度影響較大,如有源混頻器、放大器[4],因此需要依托仿真軟件和理論計算對有源器件進行精心選擇與對比,才能保證鏈路性能。在本設計中,混頻器選用IDTF1763有源混頻芯片。該芯片增益為11.7dB,OIP3可達45dBm,二次諧波及交調抑制可達60dBc以上。同時,為了保證系統增益和線性度,放大器的選擇也至關重要,電路選用HXG-122放大模塊。該模塊的OIP3高達47dBm,放大增益為16dB。選定器件后,利用ADS仿真軟件對該模塊的射頻鏈路預算做仿真分析,重點關注整個鏈路的增益、IIP3、諧波抑制度等指標。鏈路預算仿真模型和仿真結果如圖3、圖4所示。

圖3 下變頻模塊鏈路預算仿真

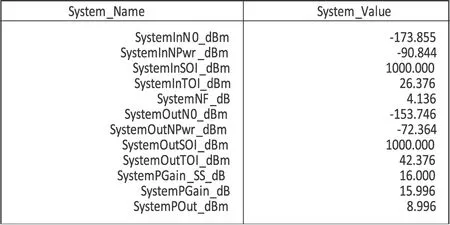

圖4 下變頻模塊鏈路預算仿真結果

圖4中“SystemPGain_dB”項為鏈路的增益,“SystemInTOI_dBm”項為鏈路的IIP3指標。由此可知,模塊的增益約為21.4 dB,可以滿足系統指標要求,此時的IIP3約為21.5 dBm。對于鏈路增益G=16 dB時的IIP3指標,需要將數控衰減器的衰減量調節至5.5 dB后,再次對圖3的模型進行仿真,仿真結果如圖5所示。可知,當鏈路增益約為G=16 dB時,下變頻模塊的IIP3指標為26.4 dBm,可以較好地滿足系統指標。

圖5 增益為16 dB時下變頻模塊鏈路預算仿真結果

電路中使用的放大器雖然線性度較高,但是其輸出1 dB壓縮點(P-1dB)為23 dBm。當射頻輸入信號達到3 dBm時放大器進入飽和狀態,若輸入功率繼續增大,系統的放大增益、輸出功率和雜諧波抑制則無法保證。因此,本電路中采用雙管合成的放大形式,以此在保證電路線性度指標的同時提高輸出功率。功率合成采用雙路等功率同相合成方式,設兩路的功率及相位分別為P1、P2和θ1、θ2,則合成功率為

(6)

當P1=P2、θ1-θ2=0時,Pout=2P1=2P2合成效率最大[5],而且當某一支路失效時整個模塊的輸出功率會下降到原先的四分之一,但模塊仍可工作,在一定程度上提高了系統的可靠性。

2.2.2 雜諧波抑制設計

作為一種非線性器件,混頻器在產生有用的中頻信號時還會產生諧波和交調分量。這些頻率分量一般表示為

mRF±nLO

(7)

在實際應用中,一般通過選用性能良好的中頻濾波器來抑制諧波和交調。下變頻模塊的二次諧波范圍為520~920MHz,三次諧波780~1 380MHz。本電路選用的中頻濾波器主要性能指標為中心頻率為360MHz、帶寬200MHz、220MHz以下和500~1 000MHz頻段的抑制度≥40dBc。因此,濾波器對二次諧波的抑制可以達到40dBc。在設計時將后端放大器的輸出功率回退10dB使用,遠離放大器的P-1點。電路對二次諧波的抑制可增加20dB[6],故模塊的二次諧波抑制度可以滿足≥60dBc的要求。同理,本模塊對三次諧波的抑制度也可以達到60dBc以上。通過仿真計算可得,本模塊中頻通帶內最低次交調為5RF-4LO,中頻帶外最低次交調為2RF-LO。仿真計算結果如圖6所示。

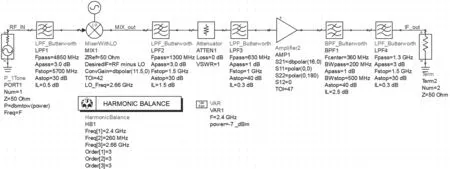

圖6 交調仿真計算結果

根據混頻器資料,混頻器對帶內5RF-4LO交調的抑制度在60dBc以上,混頻器與各級濾波器對帶外2RF-LO交調的抑制度也可達到60dBc以上。混頻器中頻輸出端對本振、射頻信號的最小抑制度分別為27、38dBc,而模塊中各級低通和帶通濾波器對本振和射頻的抑制均在40dBc以上。因此,模塊對本振和射頻信號的抑制可以滿足60dBc的指標要求。針對220MHz和500MHz中頻信號,中頻帶通濾波器對它們的抑制度均在40dBc以上,可以滿足38dBc抑制度的要求。使用ADS軟件中的諧波平衡仿真控件對下變頻模塊的雜諧波抑制情況進行仿真,仿真模型和結果如圖7、圖8所示。下變頻模塊將S波段的信號搬移至260MHz中頻,并且整個射頻前端對于各次諧波、本振和泄露的射頻信號有很好的抑制作用。

圖7 下變頻模塊雜諧波抑制仿真模型

圖8 下變頻模塊雜諧波抑制仿真結果

除了在電路設計和器件選型上消除雜諧波的影響,電路結構和布線形式也需要考慮。放大器區域使用金屬隔墻與前端小信號部分隔離,防止不同頻率的信號互相串擾。同時,為了提高接地及散熱效果,微帶板背面大面積接地并釬焊在金屬墊塊上。此外,中頻帶通濾波器在安裝時也要保證與墊塊接觸良好,以防出現因接地不良而導致濾波器響應變差。

3 電路測試結果

本電路模塊的實物如圖9所示,模塊體積緊湊、結構簡單,便于安裝和測試。模塊的各項實測指標如表1所示,增益、IIP3和雜諧波抑制度均較好地滿足技術指標。

圖9 下變頻模塊實物圖

表1 下變頻模塊測試指標

4 結束語

本文介紹了一種S波段高線性度下變頻模塊的設計方案,并對該方案做了詳細的理論與仿真分析。通過合理選擇器件和優化電路形式,較好地提高了模塊的IIP3性能,同時提高了模塊增益和雜諧波抑制度。模塊在260~460 MHz的帶寬內增益大于22 dB,IIP3達到25 dBm,雜諧波抑制度大于65 dBc,而且對帶外特定頻率信號的抑制度達到45 dBc以上,完全滿足性能指標要求。現階段該下變頻模塊已投入使用180余件,實際使用效果完全驗證了本設計的有效性。

[1] 林燕海,詹銘周,徐銳敏. Ka頻段下變頻模塊設計[J]. 微波學報,2010(S1):375-377.

[2] 林敏. CMOS射頻前端電路設計中的低噪聲、高線性度研究[D].北京:清華大學,2004.

[3] 周蘇萍.基于P和L頻段射頻前端關鍵電路研究[D].杭州:杭州電子科技大學,2011.

[4] 何俊岑,侯智鵬,周俊.基于LTCC的小型化寬帶變頻組件[J].電子信息對抗技術,2015(3):59-62.

[5] 王延恩.微波固態功率合成電路設計[D].北京:中國地質大學,2012.

[6] 李文廣,吳國安.射頻功放的非線性分析與線性化技術[J].艦船電子工程,2006(6):134-136.

Design of an S-band high-linearity down conversion module

YAN Chao, ZHAO Jia-min, YAO Wu-sheng

(No.38 Research Institute of CETC, Hefei 230088)

A high-linearity down conversion module is designed for the S-band receiving channel. The key technical specifications such as the gain, linearity as well as spurious and harmonic wave suppression are simulated and analyzed theoretically in detail with the hardware implemented. The module mainly adopts the SMD devices, including the active mixer, the high-OIP3 amplifier and the LC filter. The test results show that the gain of the module is 21dB, the spurious and harmonic wave suppression is greater than 65dBc, the suppression of the specific frequency is more than 40dBc, and the IIP3 is greater than 24dBm, indicating that the module meets the requirements, and can fully meet the application requirements of the high-performance receiving channel.

down conversion module; gain; linearity; spurious and harmonic wave suppression

2017-03-07;

2017-03-20

閆超(1988-),男,助理工程師,碩士,研究方向:雷達射頻前端;趙家敏(1985-),男,工程師,博士,研究方向:雷達射頻前端和寬帶功率放大器;姚武生(1968-),男,研究員,碩士,研究方向:雷達收發系統設計。

TN850

A

1009-0401(2017)02-0055-05