高脈沖密度雷達信號處理系統設計*

王鴻超,耿常青,王 龍,童文鋒

(1.中國人民解放軍空軍航空大學 信息對抗系,吉林 長春 130022; 2.中國人民解放軍94691部隊,福建 龍巖 366200)

高脈沖密度雷達信號處理系統設計*

王鴻超1,耿常青1,王 龍1,童文鋒2

(1.中國人民解放軍空軍航空大學 信息對抗系,吉林 長春130022;2.中國人民解放軍94691部隊,福建 龍巖366200)

隨著雷達系統的不斷升級,電磁空間當中的信號密度也在不斷增加。為了不斷適應電磁環境,滿足對高脈沖密度雷達信號處理的要求,設計了一套基于TITMS320C6678芯片和Xilinx的XC7VX485T芯片的多DSP+FPGA架構的信號處理系統。本系統的核心在于設計實現了較為合理的數據預處理流程,并通過具體的硬件電路實現。該信號處理板是一種符合VPX標準,可工作于機載、車載或其他惡劣條件下的特種設備,通過預處理設計,有效提高了系統的處理能力。

高脈沖密度;預處理;現場可編程門陣列;到達角

0 引言

隨著雷達系統的不斷升級,對信號處理系統的運算處理速度、數據帶寬和傳輸速率等要求也不斷提高[1-2]。已有的信號處理系統由多個功能模塊組合而成,集成度普遍不高,而且數據處理能力相對較弱,設備體積龐大,不能夠滿足現代信號處理的需求。而基于VPX標準的信號處理平臺能夠集高密度計算與高速數據傳輸于一體,實現強大的信號處理及數據交換能力[3],同時明顯縮小了設備體積,能夠滿足特種設備需求。

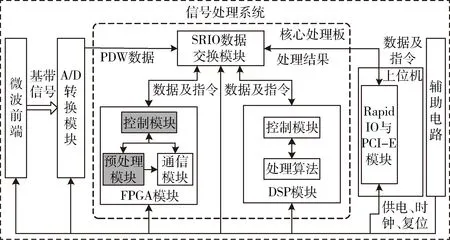

針對此,本文結合某信號處理系統科研項目,設計了符合VPX標準的信號處理系統。本系統以多核DSP芯片TMS320C6678為核心處理器,利用多核DSP與FPGA構建的串行高速數據接口(Serial Rapid Input/Output, SRIO)完成大數據量交換。在DSP芯片內完成信號處理后將計算結果經由SRIO與PCIE (Periph-eral Component Interconnect Express)轉換模塊直接上傳到上位機,在上位機端進行結果的實時顯示。上位機端通過PCIE監控各模塊運行狀態,進行健康管理以及計算資源動態調整。本系統是一個通用的數字信號處理平臺,系統集成度高,運算能力強,結構靈活。其中,預處理模塊和控制模塊的設計,進一步提升了系統的處理能力。

1 系統總體設計

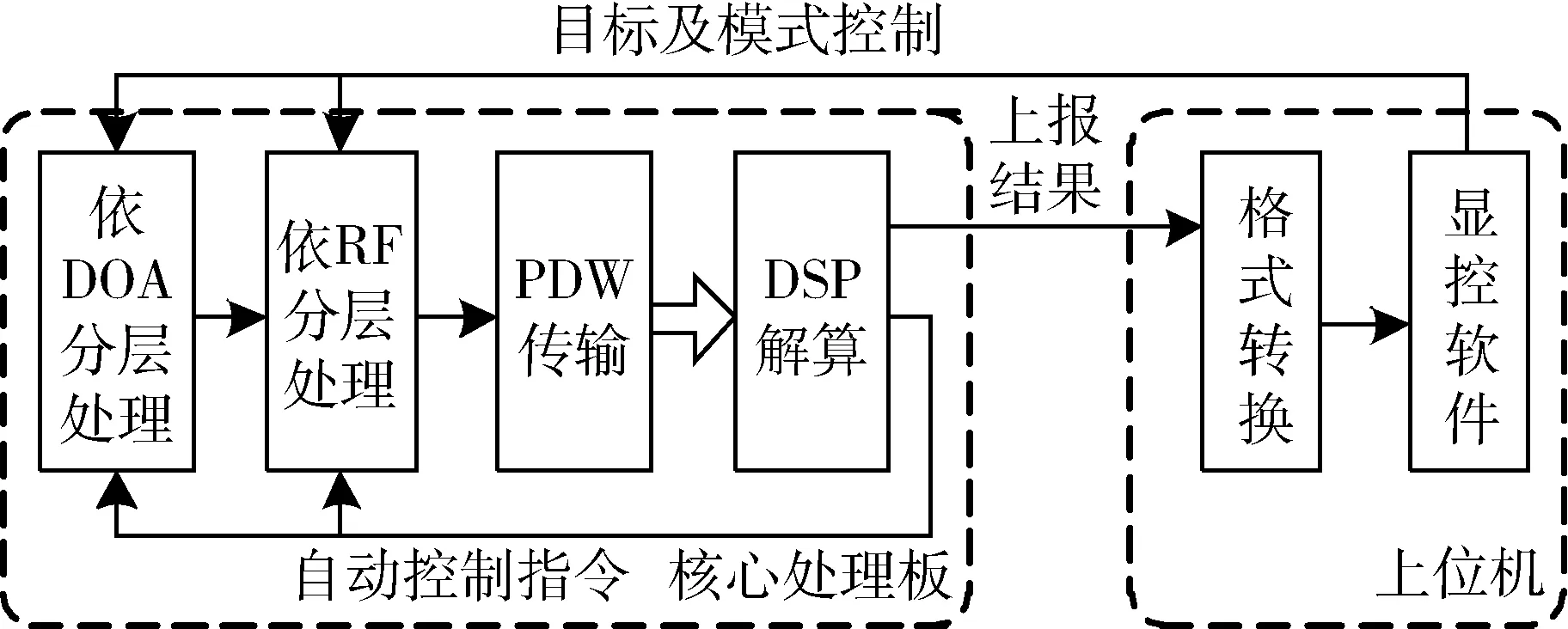

信號處理系統的電路總體設計基于多DSP+FPGA架構,系統總體設計框圖如圖1所示。從功能上看,系統可分為DSP模塊、FPGA模塊、SRIO數據交換模塊、PCIE模塊、AD轉換模塊以及包括各電平轉換模塊、電源、時鐘和控制邏輯等在內的輔助電路,在必要的驅動程序和板內控制邏輯配合下,形成一個完整的、一體化的數字系統硬件平臺。其中,DSP模塊、FPGA模塊、SRIO數據交換模塊構成了系統的核心處理板。本系統中,DSP采用主從模式工作,采用Hyperlink進行通信。DSP之間形成JTAG(Joint Test Action Group)菊花鏈,連接到J30J-31調試接口上[4]。核心處理板內部設計有大吞吐量的SRIO通信機制。通過在上位機中設計的SRIO與PCIE轉換模塊,可實現上位機對多塊核心處理板的控制以及二者的數據通信。

圖1 系統總體設計框圖

2 實現方案

2.1器件選型

圖2 預處理過程

本系統中,SRIO交換芯片選用Tsi578,其支持80 Gb/s的聚合帶寬。Tsi578系列交換機具有極強的伸縮性,使其在聯網、無線與視頻基礎架構領域得到了廣泛的應用[5-6]。Tsi578可靈活地支援多達8個4x模式或者16個1x模式的埠,交換機的埠與埠之間相互獨立,可支持多種速度、寬度配置,這也就意味著可用較低的成本開發出功能強大、性能卓越的系統。DSP選用德州儀器(TI) 最新推出的TMS320C6678[7]數字信號處理器。C66xx系列數字信號處理器是目前具有最高定/浮點運算能力的新一代數字信號處理器。TI C66xx系列多核DSP結合了之前C64xx與C67xx的優點,單核最高主頻可達1.4 GHz[8]。FPGA芯片選用Xilinx公司的Virtex-7 XC7VX485T[9]。Virtex7系列芯片是Xilinx公司2014年初推出的新一代可編程器件產品,是Xilinx在通用28 nm架構上構建的三大系列之一,與前代產品相比,能夠以低于一半的功耗實現兩倍左右的性價比,Kintex7 XC7VX485T的主要性能指標見表1。

表1 Virtex7 XC7VX485T的主要性能指標

2.2預處理設計

現有的信號處理算法對信號的樣本存在著諸如信號完整性高、信號可進行周期積累等需求,而且工程化實現難度較大。但是,復雜的戰場電磁環境又對信號處理提出了實時性、準確性的要求。基于此,本系統重點對信號處理系統的預處理過程進行了設計。預處理過程如圖2所示。

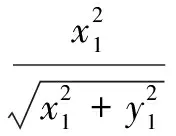

2.2.1依DOA分層處理

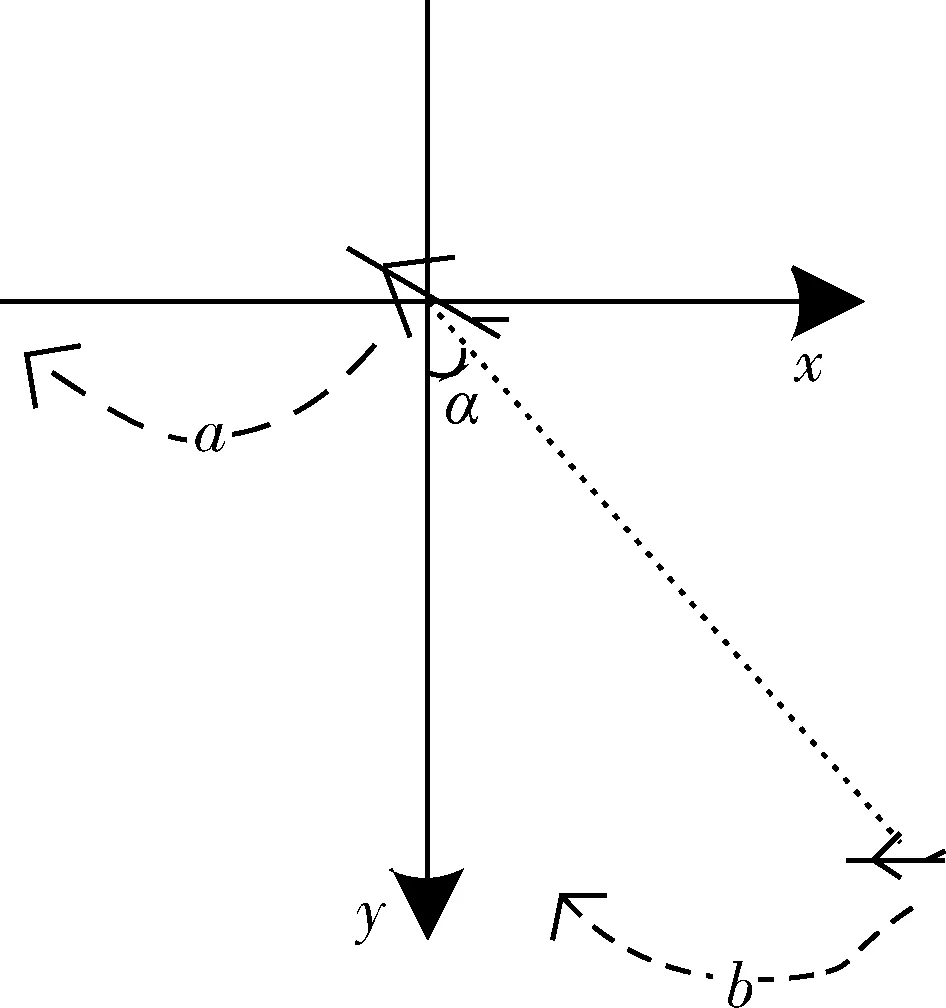

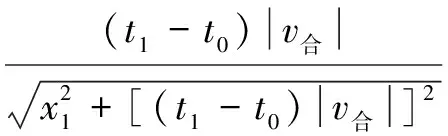

在戰場電磁環境中,敵我雙方作戰平臺一般情況下不會處于同一高度,DOA的測量是基于方位分量進行解算的,其測量示意圖如圖3所示。α即為DOA,a,b兩條曲線示意其可能的運動路徑。

考慮一種普遍情況:t0時刻,以我方偵察平臺為原點建立直角坐標系,確保敵方作戰平臺處于第一象限內,由于在第一象限內,sinα的單調性與α相一致,便于思考和討論。此時刻DOA的大小α可以用sin(α)來表示:

(1)

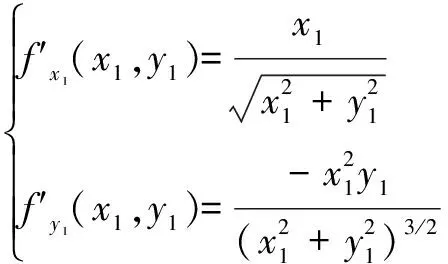

式中,(x1,y1)表示此時刻敵方作戰平臺的所在位置。考慮此時刻以我方偵察平臺建立參考系,可得在任何時刻都可以建立如式(1)的表征關系。對式(11)分別求一次偏導數可得:

圖3 DOA示意圖

(2)

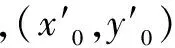

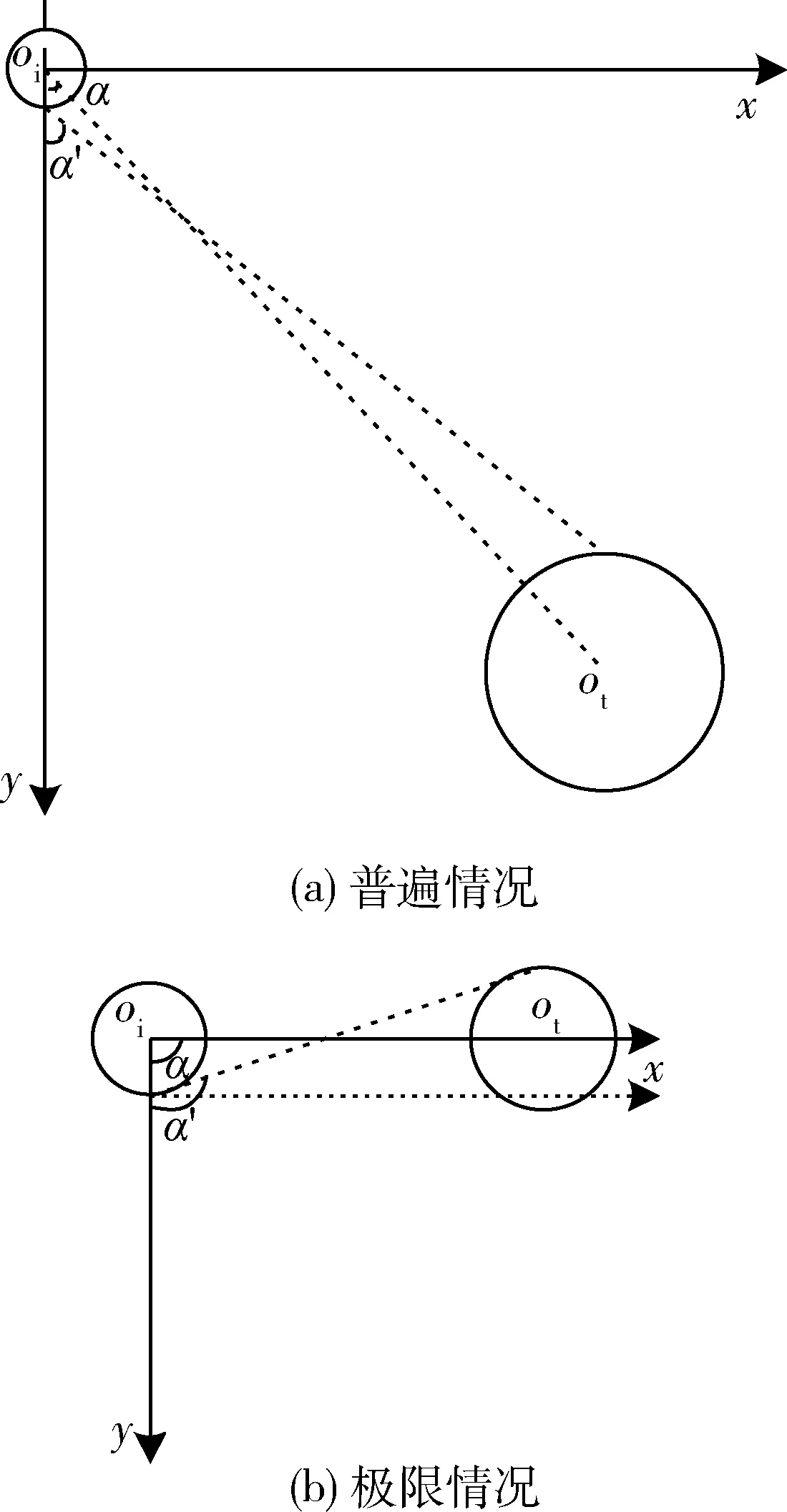

從式(2)可以得出,在(x1,y1)均為0時,兩個偏導數為0,此時,不符合其物理意義。設敵方作戰平臺再次照射的時刻為t1,此時敵我雙方的戰場態勢如圖4所示。在實際的戰場電磁空間中,我方偵察平臺會盡可能遠離敵方作戰平臺。那么t1時刻有以下方程成立:

(3)

Δαmax=α′-α=

(4)

而對反正弦函數的特性進行分析可知,反正弦函數是一個單調遞增的函數,且隨著自變量的增大,函數增長越緩慢。圖4所示的極限情況是DOA變化最大的情況。

(5)

無論是機械雷達還是電掃描雷達,其信號的重訪時間都小于1 s[10-11]。遠距離偵察平臺的防御能力差,飛行速度低,故一般情況下,偵察平臺的偵收距離應位于敵方的中遠程防空導彈射程外。以典型的中程空空導彈射程及殲擊機巡航速度為參考,此時DOA的最大變化僅約為0.77°。但考慮到偵察平臺的測角誤差δs,也為了保證盡可能覆蓋住偵測目標,同時節約系統資源消耗,在本信號處理系統設計中確定DOA的初始劃分間隔為20°。

圖4 敵我雙方戰場態勢

2.2.2依RF分層處理

在戰場電磁環境中,多種用頻設備共存,電磁信號相互交織,各種頻率成分的信號共同組成了現代戰場電磁環境。正是由于信號多樣化,才對現代信號處理系統提出了更為嚴峻的挑戰。考慮到一種作戰平臺上不止一種用頻設備或者集群編隊的情況,對DOA分層處理后的數據依照RF進行二次分層。

雷達的工作波段基本是以現行的雷達波段劃分的。為此,本級預處理的初始閾值均按照各雷達波段范圍展寬1 GHz進行設計,覆蓋了50 MHz~40 GHz的頻率范圍。預處理完成后的PDW流按照不同的閾值分配不同的邏輯通道,發送給DSP進行后續處理。

2.3控制設計

預處理過程參照了信道化的思路進行設計,雖然達到了稀釋脈沖的目的,但是由于各個邏輯通道的數據相互交疊,給后續的處理結果上報增加了一定的處理難度。為此,待信號處理完成后,需要調整各個邏輯通道的輸入數據調整,以獲取最高的運行效率。控制流程如圖5所示。

圖5 控制流程

控制模式分為人工和自動兩種。在人工模式下,可以人為地篩選關注目標,從而調整兩級分層處理閾值,優化計算資源分配,進行詳細觀察和管理,同時可以剔除部分無關頻率信號,進一步提升系統效率。在自動模式下,系統根據初步分選結果對兩級分層處理閾值進行調整,依據威脅度等級對運算資源加以調度,提高對未知信號的關注度,兼顧系統的實時性與準確性。在兩種模式下,系統都會實時監測DSP的運行狀態,協調DSP的運算資源使用。

3 測試與分析

本系統的FPGA程序在Xilinx公司提供的FPGA開發環境Vivado 2016.3下使用Verilog 語言進行編程,將關鍵的預處理模塊進行了封裝,將預處理模塊的內部工作時鐘約束到250 MHz ,進行綜合實現,布局布線的結果表明系統能夠滿足250 MHz時鐘的時序要求,但是預處理模塊需要對數據進行整理,消耗了大量的存儲資源,具體資源消耗見表2。

表2 資源消耗情況

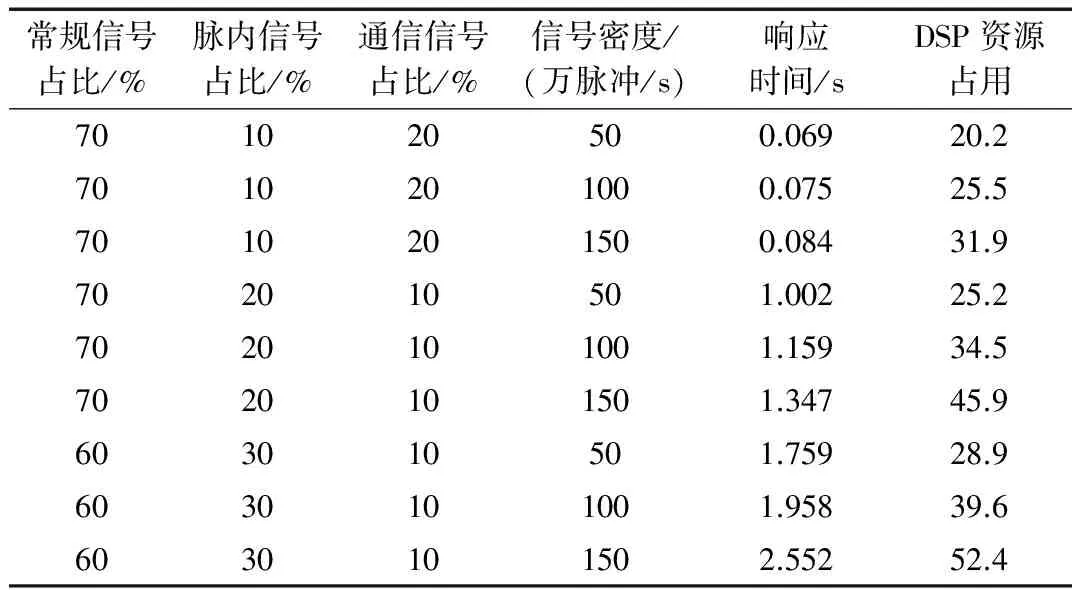

本文使用模擬雷達信號對系統進行了性能測試,測試信號包含常規信號和脈內調制信號以及通信信號。測試結果如表3所示。

表3 性能測試結果

從表2和表3可知,系統對高脈沖密度的雷達信號具有較強的處理能力,實時性較高。相對來說,脈內調制信號對系統的響應時間和DSP資源占用影響較大。

4 結論

本文提出的高脈沖密度雷達信號處理系統設計,采用多DSP+FPGA的系統架構,具有高速信號處理能力和高寬帶的內部數據通道。該信號處理模塊能夠適應高達數百萬脈沖每秒的脈沖密度,且已經成功應用于某信號處理系統中,系統運行穩定可靠,具備了高性能的數據交換和數據處理能力。

[1] GE Fanuc embedded systems,Inc. VPX: VMEbus for the 21st century[Z].2007.

[2] Mercury computer systems, Inc. Technology overview:VITA 46(VPX)[Z].2006.

[3] 鄭東衛,陳矛,羅丁利.VPX總線的技術規范及應用[J].火控雷達技術,2009,38(4): 73-77.

[4] 董選明.基于4DSP+FPGA架構數據處理板設計[J].電子技術應用,2016,42(7):29-33,37.

[5] TUNDRA Inc. Tsi578 serial rapidl0 switch user manual[EB/OL]. (2016-06-06)[2017-04-23].http://www.idt.com.

[6] Tundra Semiconductor Corporation. Tsi578 serial rapidIO Switch hardware manual[EB/OL]. (2016-04-04)[2017-04-23]. http://www .idt.com.

[7] 王韓,孫紅勝,陳昌明.基于TS201與FPGA的數字信號處理系統設計[J].現代電子技術,2016,39(5): 78-80.

[8] Texas Instruments. Data Manual:TMS320C6678 multicore fixed and floating-point digital signal processor[EB/OL]. (2014-03-06)[2017-04-23]http://www.ti.com.

[9] 王龍,楊承志,尚衛華,等.基于RF DAC的寬帶高斯聲源的設計與實現[J].微型機與應用,2016,35(17):26-27.

[10] 中航工業雷達與電子設備研究院.機載雷達手冊[M].北京:國防工業出版社,2013.

[11] 趙登平,周萬幸,鞠新春.世界海用雷達手冊[M].北京:國防工業出版社,2012.

2017-04-23)

王鴻超(1994-),男,在讀碩士研究生,主要研究方向:低截獲概率雷達信號偵察處理技術。

耿常青(1994-),男,在讀碩士研究生,主要研究方向:低截獲概率雷達信號偵察處理技術。

王龍(1992-),男,碩士,講師,主要研究方向:低截獲概率雷達信號偵察處理技術。

The radar signal processing system design of high pulse density

Wang Hongchao1, Geng Changqing1, Wang Long1, Tong Wenfeng2

(1. Faculty of Information Countermeasure, The Aviation University of Air Force, Changchun 130022, China; 2. 94691 Troops of PLA, Longyan 366200, China)

With the continuous upgrading of radar system, the signal density of electromagnetic space is also increasing.To constantly adapt to the electromagnetic environment and meet the requirement of high density of pulse radar signal processing, this paper designed a set of signal processing system of DSP+FPGA structure based on TI TMS320C6678 chips and Xilinx XC7VX485T chips.The core of this system is to design and realize the reasonable data pretreatment process, and implemen it through the concrete hardware circuit. The signal processing board is conformed to VPX standard, and can work in airborne, vehicle or other harsh conditions of special equipment. Through the pretreatment design, it effectively improved the processing power of the system.

high pulse density; pretreatment process; FPGA; DOA

TN974

A

10.19358/j.issn.1674- 7720.2017.22.012

王鴻超,耿常青,王龍,等.高脈沖密度雷達信號處理系統設計J.微型機與應用,2017,36(22):41-44.

國家自然科學基金(61571462)