基于非均勻感知策略的MLC閃存系統(tǒng)①

張 旋,燕 莎,周 樂

1(西安理工大學(xué) 高等技術(shù)學(xué)院,西安 710082)

2(西安電子科技大學(xué) 計(jì)算機(jī)學(xué)院,西安 710071)

NAND閃存是非易失性存儲(chǔ)器(Non-Volatile),由于其高容量、低成本、讀寫速度快等優(yōu)點(diǎn)被廣泛的應(yīng)用于消費(fèi)電子產(chǎn)品中,如手機(jī)、筆記本電腦等[1,2].多級(jí)單元(Multi-Level Cell,MLC)技術(shù)成為提高NAND型閃存數(shù)據(jù)容量和降低成本的有效手段.然而,目前NAND閃存芯片封裝尺寸減少,MLC閃存浮柵中可存儲(chǔ)的電子變少、相鄰電位窗口間隔變窄、相鄰MLC單元之間的寄生耦合電容效應(yīng)變大,單元間干擾(Cell-to-Cell Inference,CCI)成為影響閃存閾值電壓失真的主要原因.因此,NAND閃存的可靠性急劇下降[3].

隨著NAND閃存封裝尺寸減小和MLC技術(shù)的應(yīng)用,傳統(tǒng)的糾錯(cuò)碼已不能滿足MLC型NAND閃存的可靠性要求[4,5].LDPC碼是具有低譯碼復(fù)雜度和逼近香農(nóng)限的良好性能成為提高M(jìn)LC型NAND閃存可靠性的研究方向之一[3-6].Wang和Courtade研究利用閃存信道的統(tǒng)計(jì)信息獲得更好的LDPC碼軟判決譯碼性能[7].對(duì)于MLC閃存軟信息的準(zhǔn)確度會(huì)影響到LDPC碼譯碼器的糾錯(cuò)性能.基于均勻感知策略的MLC電壓感知方法需要提高感知精度才能獲取高精度的對(duì)數(shù)似然比(Log-Likelihood Ratio,LLR)值.但是,高感知精度會(huì)消耗更長(zhǎng)的感知時(shí)間,影響閃存的讀取速度.本文提出了一種基于非均勻感知策略的MLC閃存最小和譯碼方法,該方法是對(duì)MLC相鄰閾值電壓分布重疊區(qū)間進(jìn)行均勻劃分,而不采用均勻感知策略中將每個(gè)MLC狀態(tài)的閾值電壓區(qū)間的均勻劃分方法.在相同的感知精度下,相比于均勻感知策略,非均勻感知策略能夠提高LLR的準(zhǔn)確度,進(jìn)而能夠在LDPC碼最小和譯碼過程中傳遞更多的有效信息,提高譯碼器的譯碼性能.

1 MLC型NAND閃存

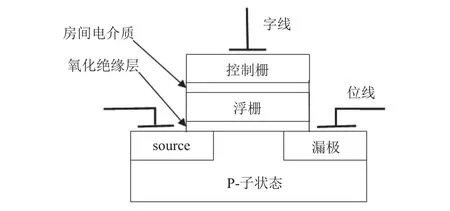

NAND閃存的最小存儲(chǔ)單元是帶浮柵(Floating Gate)的MOS晶體管.其中浮柵被氧化絕緣層隔離,電荷注入其中可以長(zhǎng)期穩(wěn)定保存(如圖1所示).浮柵中電荷數(shù)量決定閃存單元的閾值電壓,不同的閾值電壓可以映射為不同的狀態(tài),從而表示不同的數(shù)據(jù).

圖1 閃存單元基本結(jié)構(gòu)

MLC型NAND閃存通過一個(gè)浮柵單元存儲(chǔ)4個(gè)不同電位表示2比特?cái)?shù)據(jù),提高NAND閃存的數(shù)據(jù)存儲(chǔ)密度.MLC型NAND閃存使用標(biāo)準(zhǔn)的格雷碼來映射閃存單元中的四個(gè)狀態(tài)(s0=11,s1=01,s2=00,s3=10),相鄰兩個(gè)狀態(tài)僅有一位二進(jìn)制數(shù)不同,能夠降低原始誤比特率(Raw Bit Error Rate,RBER).單元中第i個(gè)比特表示為bi(i∈{0,1}),b0稱為最低有效位(Least Significant Bit,LSB),b1稱為最高有效位(Most Significant Bit,MSB),其中s0=11表示擦除狀態(tài)(Erase State),s1=01,s2=00和s3=10分別表示三個(gè)編程狀態(tài)(Program State)[3].

1.1 MLC閾值電壓模型的建立

MLC閃存芯片在擦除操作(將浮柵中的電子移除)之后閃存單元的閾值電壓可近似地使用一個(gè)高斯分布來表示.因此使用公式(1)來表示MLC閃存單元擦除狀態(tài)的閾值電壓分布[8]:

隨著閃存封裝尺寸的減小(65 nm及以下),編程操作(向浮柵充電至不同的電位)使MLC閃存單元閾值電壓增加,其數(shù)學(xué)模型pp(x)∈{ps1(x),ps2(x),ps3(x)}可近似為高斯分布,如公式(2)所示[8]:

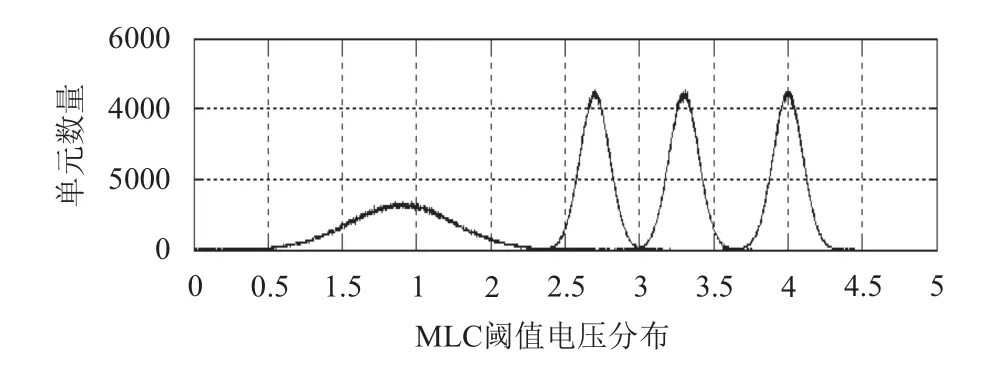

MLC閾值電壓模型參數(shù)設(shè)置為:擦除狀態(tài)閾值電壓分布概率密度函數(shù)ps0(x)的均值μe=1.4,標(biāo)準(zhǔn)差σe=0.35,三個(gè)編程狀態(tài)的閾值電壓分布概率密度函數(shù)ps1|s2|s3(x)的標(biāo)準(zhǔn)差σp=0.1,均值μs1=2.7,μs2=3.3,μs3=4.0.通過蒙特卡羅統(tǒng)計(jì)方法可得理想狀態(tài)的閾值電壓統(tǒng)計(jì)直方圖(如圖2所示)[8].

圖2 理想情況下的MLC閾值電壓統(tǒng)計(jì)直方圖

1.2 單元間干擾噪聲模型的建立

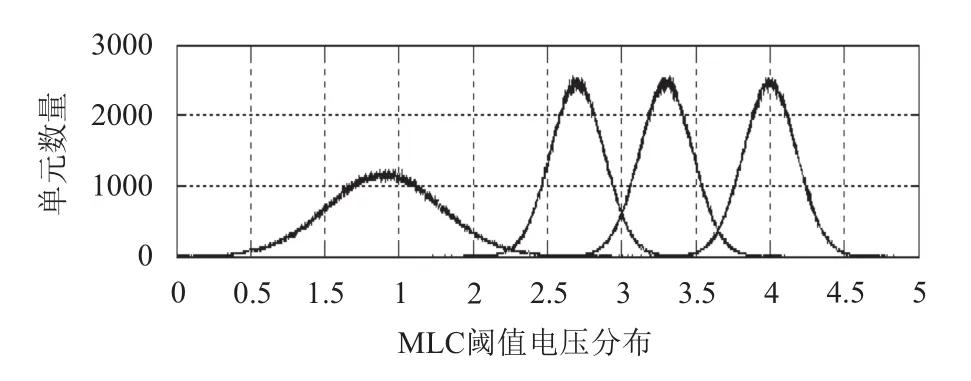

MLC閃存由于單元間存在寄生耦合電容效應(yīng),所以當(dāng)MLC單元經(jīng)過編程操作增加閾值電壓之后,這種電壓的增量會(huì)對(duì)其鄰近MLC單元的閾值電壓產(chǎn)生影響,這種影響稱之為單元間干擾[9](如圖3所示).目前,CCI噪聲已經(jīng)成為影響MLC閃存可靠性的主要噪聲源.CCI噪聲影響大小F可用公式(3)計(jì)算[3]:

圖3 CCI干擾示意圖

其中,ΔV(k)表示編程操作使MLC閾值電壓的增量,γ(k)表示電容耦合系數(shù).用耦合強(qiáng)度因子s表示單元間干擾的強(qiáng)弱.垂直方向電容耦合系數(shù)γy=0.08s,對(duì)角線方向的電容耦合系數(shù)γxy=0.006s.通過蒙特卡羅統(tǒng)計(jì)模擬方法可得CCI干擾后(s=1.5)的閾值電壓統(tǒng)計(jì)直方圖(如圖4所示).

圖4 CCI噪聲干擾后的MLC閾值電壓統(tǒng)計(jì)直方圖

由圖4分析可得,MLC閃存在加入CCI噪聲后,MLC閃存單元閾值電壓發(fā)生波動(dòng),相鄰的閾值電壓分布出現(xiàn)重疊區(qū)域,位于此區(qū)域的MLC單元在判決時(shí)出錯(cuò)概率較高,進(jìn)而導(dǎo)致錯(cuò)誤讀取存儲(chǔ)的數(shù)據(jù).

2 MLC閃存的最小和譯碼算法

2.1 MLC閾值電壓的均勻感知和非均勻感知策略

讀取MLC閃存中存儲(chǔ)的信息必須借助閾值電壓感知才能得到.感知方法是通過設(shè)定參考電壓將每個(gè)MLC狀態(tài)的閾值電壓區(qū)間進(jìn)行劃分(如圖5所示),將參考電壓從小至大加載到被感知單元的控制柵,根據(jù)控制柵的導(dǎo)通性來判斷被感知單元的閾值電壓是否落入當(dāng)前參考電壓的區(qū)間內(nèi),記為[Rl,Rr),因此,感知得到的MLC閾值電壓不是精確值而是估計(jì)值,即Vth滿足(Rl≤Vth

圖5 MLC閾值電壓均勻感知策略(p=4)

MLC閾值電壓的均勻感知策略(Uniform Sensing Strategy)是對(duì)每個(gè)狀態(tài)的閾值電壓分布區(qū)間進(jìn)均勻分割進(jìn)而得到若干個(gè)參考電壓區(qū)間,圖5為感知精度(p=4)的均勻劃分.

非均勻感知策略(Non-Uniform Sensing Strategy)動(dòng)機(jī)是若閾值電壓處于重疊區(qū)域的MLC單元由于判決時(shí)不確定性高,因而需要較高的感知精度,而處于非重疊區(qū)域只需較低感知精度就可保證感知的可靠性.非均勻感知策略的方法是在相鄰閾值電壓分布的重疊區(qū)間內(nèi),將該區(qū)間劃分為多個(gè)相等的參考區(qū)間(如圖6所示).非均勻感知策略可以在保持總體感知精度不變的同時(shí),提高感知數(shù)據(jù)的精確度.

圖6 MLC閾值電壓非均勻感知策略(p=4)

為了驗(yàn)證非均勻感知策略的有效性,在MLC閃存信道下對(duì)比均勻感知策略和非均勻感知策略的感知性能.仿真參數(shù)設(shè)置為:MLC閃存模型和CCI噪聲模型與1.1和1.2節(jié)相同,感知精度p分別使用3,4,5和6,概率比值系數(shù)R=512和單元間耦合因子s=1.2下,統(tǒng)計(jì)兩種感知策略下RBER.

由圖7可以看出,在MLC閃存單元的閾值電壓感知策略中,使用非均勻感知策略比使用均勻感知策略能夠獲得更低的RBER,感知精度為4的非均勻感知策略下的RBER基本等同于感知精度為5的均勻感知策略下的RBER,減小了感知延遲.

圖7 不同感知精度下兩種感知策略的性能對(duì)比圖

2.2 MLC閃存的最小和譯碼算法

和積譯碼算法是LDPC碼的軟判決譯碼算法,具有較好的譯碼性能,但計(jì)算復(fù)雜度高,譯碼時(shí)延較大.最小和譯碼算法通過簡(jiǎn)化和積譯碼算法中校驗(yàn)節(jié)點(diǎn)消息更新處理過程,降低譯碼算法的計(jì)算復(fù)雜度,同時(shí)又可以達(dá)到同和積譯碼算法近似的譯碼效果[10].本文采用最小和譯碼算法作為MLC閃存的糾錯(cuò)碼(算法1),既可保證糾錯(cuò)性能,又具有較低的譯碼復(fù)雜度,適用于MLC閃存系統(tǒng)的應(yīng)用.

3 仿真實(shí)驗(yàn)及分析

為了驗(yàn)證這兩種感知策略對(duì)最小和算法譯碼性能的影響,仿真實(shí)驗(yàn)使用碼率為0.95(34520,32794)QCLDPC碼,列重為4,環(huán)長(zhǎng)為6,該碼避免了迭代譯碼過程中出現(xiàn)的短環(huán),可以提高迭代譯碼的性能.設(shè)最大迭代次數(shù)為20.仿真使用的單元間干擾耦合因子s∈[0.6,2],感知精度p取值為3,4和5,在MLC閾值電壓感知過程中分別使用均勻感知策略(Uniform)和非均勻感知(Non-uniform)策略.

根據(jù)圖8的仿真結(jié)果可以得出,在MLC閃存模型及相同的CCI噪聲作用下,與均勻感知策略下的最小和譯碼算法相比,基于非均勻感知策略的最小和譯碼算法能夠?yàn)镸LC閃存模型提供更好的糾錯(cuò)性能.隨著MLC閾值電壓感知精度的提高,均勻感知策略和非均勻感知策略下的最小和碼算法譯碼性能都相應(yīng)提高,說明感知精度的增加有助于提高LLR值計(jì)算的準(zhǔn)確性,進(jìn)而提高LDPC碼的譯碼性能.

圖8 均勻與非均勻感知策略下最小和譯碼的性能圖

4 結(jié)語

在深入分析MLC閃存模型和CCI噪聲的基礎(chǔ)上,由于MLC閾值電壓均勻感知策略得到不精確的LLR值會(huì)影響LDPC碼最小和譯碼算法譯碼性能,因此本文提出一種可以提高LLR計(jì)算精度的非均勻閾值電壓感知策略,并將該策略應(yīng)用到MLC閃存模型中,通過實(shí)驗(yàn)仿真結(jié)果表明在相同的感知精度下,非均勻感知策略比均勻感知策略能夠獲得更低的原始比特錯(cuò)誤率,而且能提升最小和譯碼性能,從而為MLC閃存提供了更高的可靠性保證.

1Takeuchi K.NAND flash application and solution.IEEE Solid-State Circuits Magazine,2013,5(4):34-40.[doi:10.1109/MSSC.2013.2278087]

2Klein D.The history of semiconductor memory:From magnetic tape to NAND flash memory.IEEE Solid-State Circuits Magazine,2016,8(2):16-22.[doi:10.1109/MSSC.2016.2548422]

3Dong GQ,Xie ND,Zhang T.On the use of soft-decision error-correction codes in NAND flash memory.IEEE Transactions on Circuits and Systems I:Regular Papers,2011,58(2):429-439.[doi:10.1109/TCSI.2010.2071990]

4Sala F,Immink KAS,Dolecek L.Error control schemes for modern flash memories:Solutions for flash deficiencies.IEEE Consumer Electronics Magazine,2015,4(1):66-73.[doi:10.1109/MCE.2014.2360965]

5Micheloni R,Marelli A,Ravasio R.Error Correction Codes for Non-Volatile Memories.Springer Science &Business Media,2008:85-101.

6Dong GQ,Li S,Zhang T.Using data postcompensation and predistortion to tolerate cell-to-cell interference in MLC NAND flash memory.IEEE Transactions on Circuits and Systems I:Regular Papers,2010,57(10):2718-2728.[doi:10.1109/TCSI.2010.2046966]

7Wang JD,Dong GQ,Courtade T,et al.LDPC decoding with limited-precision soft information in flash memories.arXiv:1210.0149,2012:652-657.

8Aslam CA,Guan YL,Cai K.Detector for MLC NAND flash memory using neighbor-a-priori information.IEEE Transactions on Very Large Scale Integration (VLSI)Systems,2016,24(9):2827-2836.[doi:10.1109/TVLSI.2016.2523759]

9Park KT,Kang M,Kim D,et al.A zeroing cell-to-cell interference page architecture with temporary LSB storing and parallel MSB program scheme for MLC NAND flash memories.IEEE Journal of Solid-State Circuits,2008,43(4):919-928.[doi:10.1109/JSSC.2008.917558]

10陳正康,張會(huì)生,李立欣,等.LDPC碼最小和譯碼算法的整數(shù)量化.系統(tǒng)工程與電子技術(shù),2015,37(10):2371-2375.[doi:10.3969/j.issn.1001506X.2015.10.28]