基于FPGA的中子發生器系統集成IC的設計方法與實現*

張 偉 張 建 尹德有

(丹東東方測控技術股份有限公司)

現今隨著電子技術的不斷發展,現場編程門陣列(FPGA)的技術不斷進步,其運算速度和存儲空間都有了很大的提高,功能變得更加強大,而成本的不斷減低,也使得FPGA的應用領域越來越廣。

一般的FPGA的設計是根據外圍設備編寫不同的功能模塊,這些模塊結構設計不統一,接口設計多樣化,不適合系統級整體設計,可重構性和可移植性差,使得產品開發周期大大增加。為此,提出的多模塊化集成IC設計方法,具有通用的接口設計,方便的數據讀寫操作,能夠很大程度上提高設計的可重構性和可移植性,減少產品的設計周期。

1 設計原理

在多模塊集成IC設計原理中,最重要的是通用接口設計。如圖1所示,在通用接口設計中,通過與上位機通訊,在FPGA接口模塊中分配數據,確定上位機需要訪問的器件地址、寄存器地址、讀寫方式、數據控制等,通過譯碼器與鎖存器將數據發送給模塊,實現多個模塊的獨立控制。

圖1 設計結構框圖

2 SPI通訊接口設計

采用SPI從機總線實現與上位機通訊,8位數據傳輸,連續4個8位數據,每8位數據代表一個地址,第一個8位數據為控制器器件地址和讀寫信號,第二個8位數據為器件寄存器地址,第三、四個8位數據是16位數據值,同時第三、四個8位數據也可以為讀數據。SPI從機通訊模塊見圖2。

圖2 SPI從機通訊模塊

3 數據鎖存和地址分配

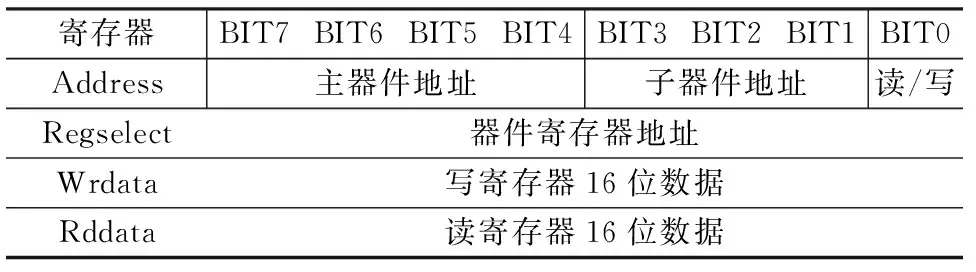

所有的數據包括地址數據Address,寄存器數據Regselect,寫數據Wrdata,讀數據Rddata都由鎖存器74373鎖存。Address地址高4位由74154譯碼器轉換成16位主器件地址片選,BIT3~BIT1由74138譯碼器轉換成8位子器件地址片選。即Address數據的地址可外接共16大類設備器件,每大類器件又可接8個相同模塊。這樣的地址設計方法也可以自行定義。接口說明見表1。

4 通用接口設計

模塊集成IC設計是仿照傳統集成芯片設計,其通用接口具有內部寄存器分配、片選接口、讀寫使能接口等。

表1 接口說明

(1)模塊IC設計具有通用的傳輸接口,見表2。

表2 模塊IC設計通用接口

(2)內部寄存器分配。內部寄存器分為控制寄存器和數據寄存器兩種,并分配有不同的地址。控制寄存器用于使能模塊和模塊內部觸發,中斷等功能實現。數據寄存器則用于實現對系統外部設備數據的讀寫。這樣設計,方便了對模塊內部數據的檢測,可以用于軟件的調試。

(3)外設時序。針對不同的應用,每個外設的時序各不相同,在實現內部數據寄存器和控制寄存器的初始化后,按照基本的外設時序編寫驅動功能。

5 FPGA軟件設計

如圖3所示4通道D/A接口模塊,其中clk、rst接口為系統時鐘和系統復位,模塊的地址位0x30,是由Address地址數據經過譯碼器得到的,MA3代表主器件地址,SA0代表子器件地址,regvalue代表寄存器地址,讀寫信號由Address[0]確定,并通過非門形成互鎖,datain[15..0]是數據輸入,DA[15..0]是數據輸出,其他是設備的接口。

圖3 4通道D/A模塊框圖

FPGA通用接口設計軟件如下:

∥寫地址[1]

always @ (address)

begin

da1_value_reg_selected <= 0;

da2_value_reg_selected <= 0;

da3_value_reg_selected <= 0;

da4_value_reg_selected <= 0;

control_reg_selected <= 0;

case(address)

0:da1_value_reg_selected <= 1; ∥通道1電壓輸出

1:da2_value_reg_selected <= 1;∥通道2電壓輸出

2:da3_value_reg_selected <= 1;∥通道3電壓輸出

3:da4_value_reg_selected <= 1;∥通道4電壓輸出

4:control_reg_selected <= 1;∥控制寄存器

default:

begin

da1_value_reg_selected <= 0;

da2_value_reg_selected <= 0;

da3_value_reg_selected <= 0;

da4_value_reg_selected <= 0;

control_reg_selected <= 0;

end

endcase

end

∥寫D/A通道電壓輸出數據

always @ (posedge clk or negedge reset_n)

begin

if(reset_n==1′b0)

begin

da1_value_reg=0;

da2_value_reg=0;

da3_value_reg=0;

da4_value_reg=0;

end

else

begin

if(write & !chipselect & da1_value_reg_selected)

begin

da1_value_reg <= writedata;

end

if(write & !chipselect & da2_value_reg_selected)

begin

da2_value_reg <= writedata;

end

if(write & !chipselect & da3_value_reg_selected)

begin

da3_value_reg <= writedata;

end

if(write & !chipselect & da4_value_reg_selected)

begin

da4_value_reg <= writedata;

end

end

end

∥寫D/A控制寄存器值

always @ (posedge clk or negedge reset_n)

begin

if(reset_n==1'b0)

begin

control_reg = 0;

end

else

begin

if(write & !chipselect & control_reg_selected)

begin

control_reg <= writedata[0];∥使能

end

end

end

∥讀數據

always @ (address or read or da1_value_reg_selected or

da2_value_reg_selected or da3_value_reg_selected or

da4_value_reg_selected or control_reg_selected)

∥always @ (posedge clk)

begin

if(read)

case(address)

0:readdata <= da1_value_reg;

1:readdata <= da2_value_reg;

2:readdata <= da3_value_reg;

3:readdata <= da4_value_reg;

4:readdata <= control_reg;

default:readdata<=16′h0000;

endcase

end

通用接口設計是所有外掛設備模塊的重要部分,其他模塊設計都可按照上述方法實現,這種設計方法高效簡單,應用性強。設備接口驅動則按照不同模塊的時序設計完成。

6 設計驗證

在上述設計原理及軟件結構的基礎上,采用Altera公司FPGA,Cyclone E系列芯片EP4CE22,其邏輯單元22,320(LEs),嵌入式存儲單元594(Kbits),本設計共8個大類,15個模塊組成,包括SPI總結模塊、LED模塊、PWM模塊、A/D模塊、D/A模塊等,約占80%的片上資源。通用接口modelsim仿真見圖4,設備接口modelsim仿真見圖5。

7 結 語

在FPGA設計中,多模塊集成IC設計方法實現了將多個不用模塊或多個相同模塊的集成設計,每個模塊具有通用的設計接口,簡化了通訊接口設計,提高了模塊的可移植性;靈活的地址分配設計,方便的多個模塊的連接,形成了總線設備多元化設計;內部寄存器的設計,可以針對模塊內部數據進行讀寫,方便調試。總之,多模塊集成IC設計簡化了模塊接口設計,增加了軟件設計的可重構性和可移植性,減少了產品設計開發周期。

圖4 通用接口modelsim仿真

圖5 設備接口modelsim仿真

[1] SANIR P.Verilog數字設計與綜合[M].2版.北京:電子工業出版社,2009.