軟件無線電的通信系統實驗平臺研制(1)

——硬件資源

戴 伏 生

(哈爾濱工業大學(威海) 信息與電氣工程學院,山東 威海 264209)

0 引 言

從系統級角度開展有實效的無線電通信實驗,是通信或者電子信息類專業的一個比較難解決問題。若采用無線電通信設備開展實驗,因受限于設備采用的技術,只能進行固定和單一的驗證性實驗,無法按意愿開展設計性和創新性實驗;若單純利用仿真軟件開展系統級無線電通信實驗,雖然可以開展設計性實驗,但是仿真環境所假設的無線電通信工作條件往往與實際情況相差甚遠,得到的仿真結果往往不夠真實。如果利用開源軟件無線電GNU Radio研制半實物半仿真的無線電通信系統教學實驗平臺裝備實驗室,不僅成本低廉,而且完全能夠滿足從系統級角度開展各種層次的具有實際效果的無線電通信實驗教學。雖然一些電子設備生產商推出了通用軟件無線電外設(Universal Software Radio Peripheral,USRP)產品如USRP N210,但是檢索國內外文獻及論壇、網站等,能夠找到的資料都是如何在電腦使用等內容[1-9],并沒有系統介紹USRP內部核心技術方面資料。若使用USRP產品卻不掌握其軟硬件工作原理,所能做的也僅限于用現有產品對信號處理功能軟件進行初級驗證,難以滿足在教學實踐中開展創新性實驗。若打算開展真正意義上的系統級無線電技術創新實驗和開發,只有全面掌握實驗設備的軟硬件工作原理才能做到,因此有必要參考USRP功能,設計一款物美價廉且核心工作原理和技術公開,以及能兼容USRP產的軟件無線電通信系統教學實驗平臺。為利于與同行經驗交流,擬對所研制的實驗平臺按所涉及的技術與功能劃分為6個專題介紹。本文為第一個專題,闡述實驗平臺的系統總體思想、硬件資源、FPGA安全配置模式下片上系統結構及工作方式。

1 實驗平臺總體設計思想

1.1 軟件無線電與研制的實驗平臺關系

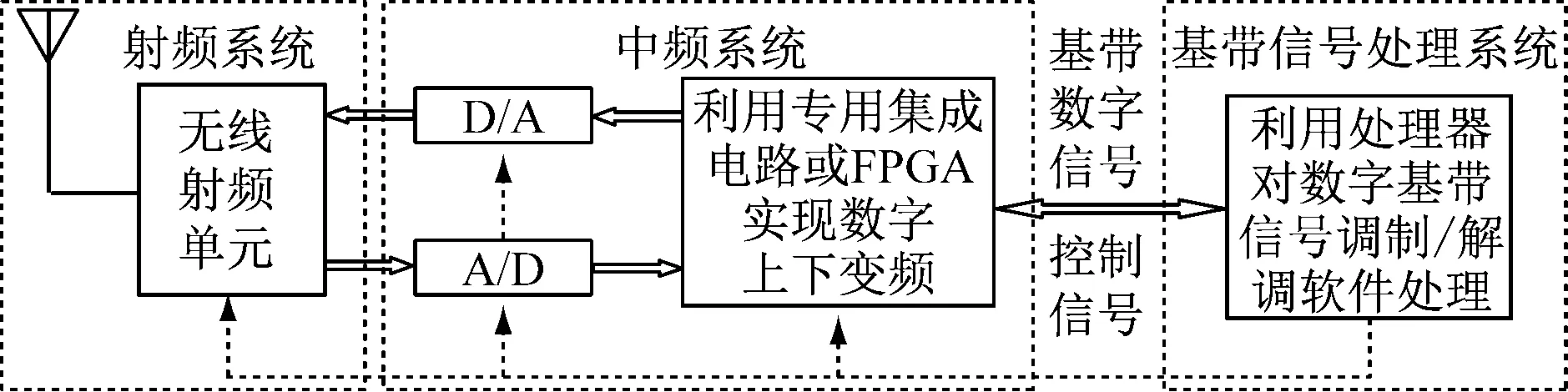

理想的軟件無線電是:希望在一個開放的公共硬件平臺上,利用不同可編程的軟件方法實現所需要的無線電系統。但是,在目前技術條件下,軟件無線電系統尚達不到全部可編程的要求,結果是產生了軟件定義的無線電(Software Defined Radio,SDR)[10]。SDR的結構如圖1所示,SDR的多模適應性要求寬帶的射頻前端,包括多頻段和寬帶天線、可配置的射頻帶通濾波器和放大器、上下變頻等。SDR期望將盡可能多的通信功能用軟件實現,這就要將ADC和DAC盡可能的靠近射頻天線端,即由現在的基帶移到中頻。ADC后的所有處理都用可編程數字處理器件,依靠軟件編程來實現。

圖1軟件定義的無線電SDR基本組成原理框圖

實驗平臺是根據SDR思想而設計的,分為主板和射頻子板。主板是指圖1中的中頻系統,主板中A/D后的所有處理都是用由FPGA可編程實現的,且A/D和D/A工作方式也是通過編程設置的。在設計上若要完成無線設備功能必須有射頻子板配合,可認為射頻子板是實驗平臺的配套附件。射頻子板對應圖1的射頻系統。射頻子板按照積木式思想配置,既可以為固定頻率的單頻點射頻子板,又有可軟件編程任意設置射頻工作頻點的寬帶射頻子板,實驗時可根據射頻應用場合和工作頻率需要選擇射頻子板。圖1中基帶信號處理系統并不是實驗平臺組成部分,但若要使實驗平臺能真正工作須有電腦才行,所以電腦充當了軟件無線電中的基帶信號處理及核心控制系統角色。

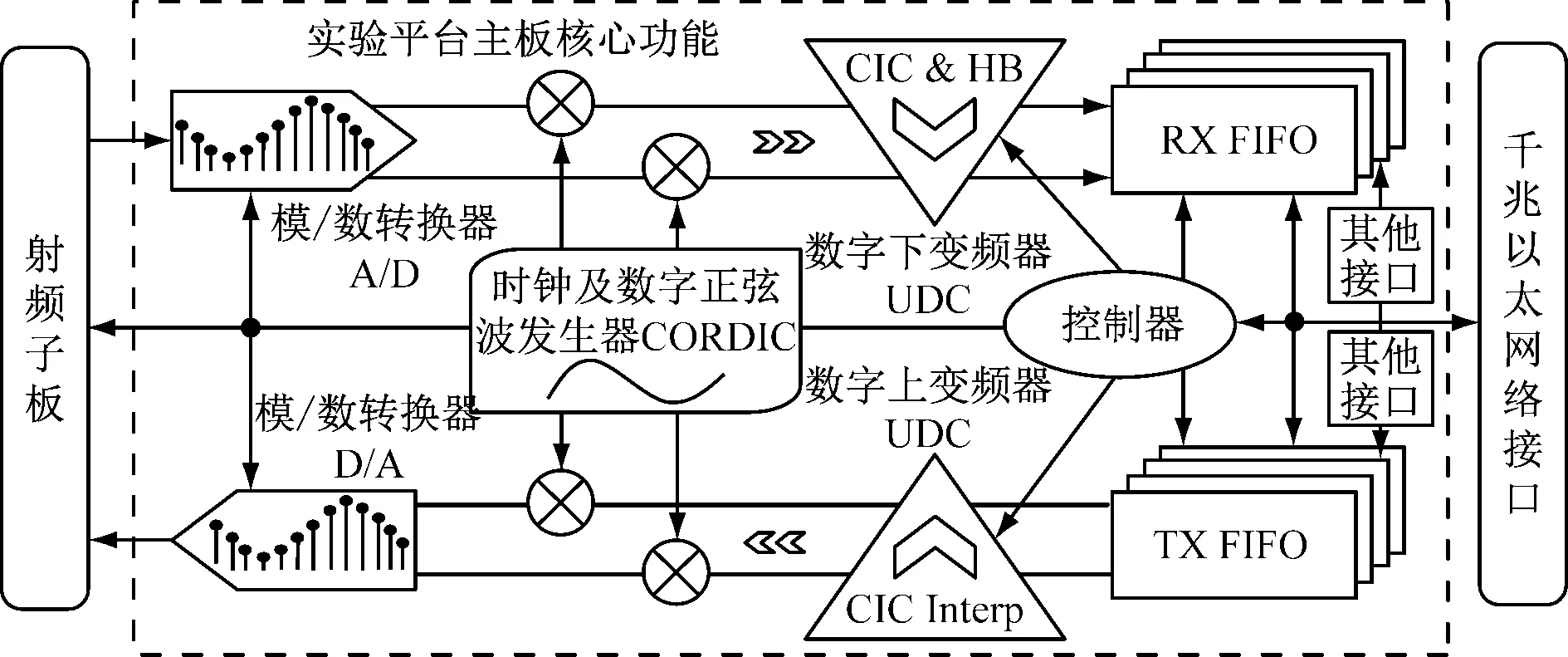

1.2 實驗平臺主板功能及承擔任務

實驗平臺主板在軟件無線電系統中擔負著承上啟下信息處理作用,它既是一個無線電通信系統的中頻部分處理系統,又是射頻信號和數字基帶信號的傳輸系統,設計理念是,在主機CPU上完成所有波形相關方面的處理,比如數字基帶調制和解調等任務。所有諸如數字上下變頻、抽樣和內插等任務都在主板上完成。射頻信號收發任務則交由射頻子板去完成,而射頻子板管理和控制由主板負責。圖2為實驗平臺主板設計理念功能框圖。

圖2實驗平臺設計理念功能框圖

為適應射頻通用性及兼容USRP N210的需要,實驗平臺采用雙通道A/D及雙通道D/A,與無線前端系統的射頻子板采用模塊化接口設計方式,可適應多種射頻子板。同時,為適應多功能和擴展性的需要,實驗平臺考慮設計了擴展端口,可以將多個設備以同步方式組成MIMO系統。為適應高速數據流傳輸的需要,實驗平臺采用千兆以太網接口就是考慮基帶信息能夠實現與主機進行高速交換,這才能使得應用程序可以通過實驗平臺同時發送或接收能夠滿足50MHz的射頻帶寬。實驗平臺須借助主機對其管理和控制。主機即上位機主要是利用運行在Linux系統上免許可的GNU Radio,開展用戶應用級別的軟件無線電建模、仿真、代碼開發、基帶信號處理、對實驗平臺的管理與控制以及實驗運行等。

2 實驗平臺主板硬件資源

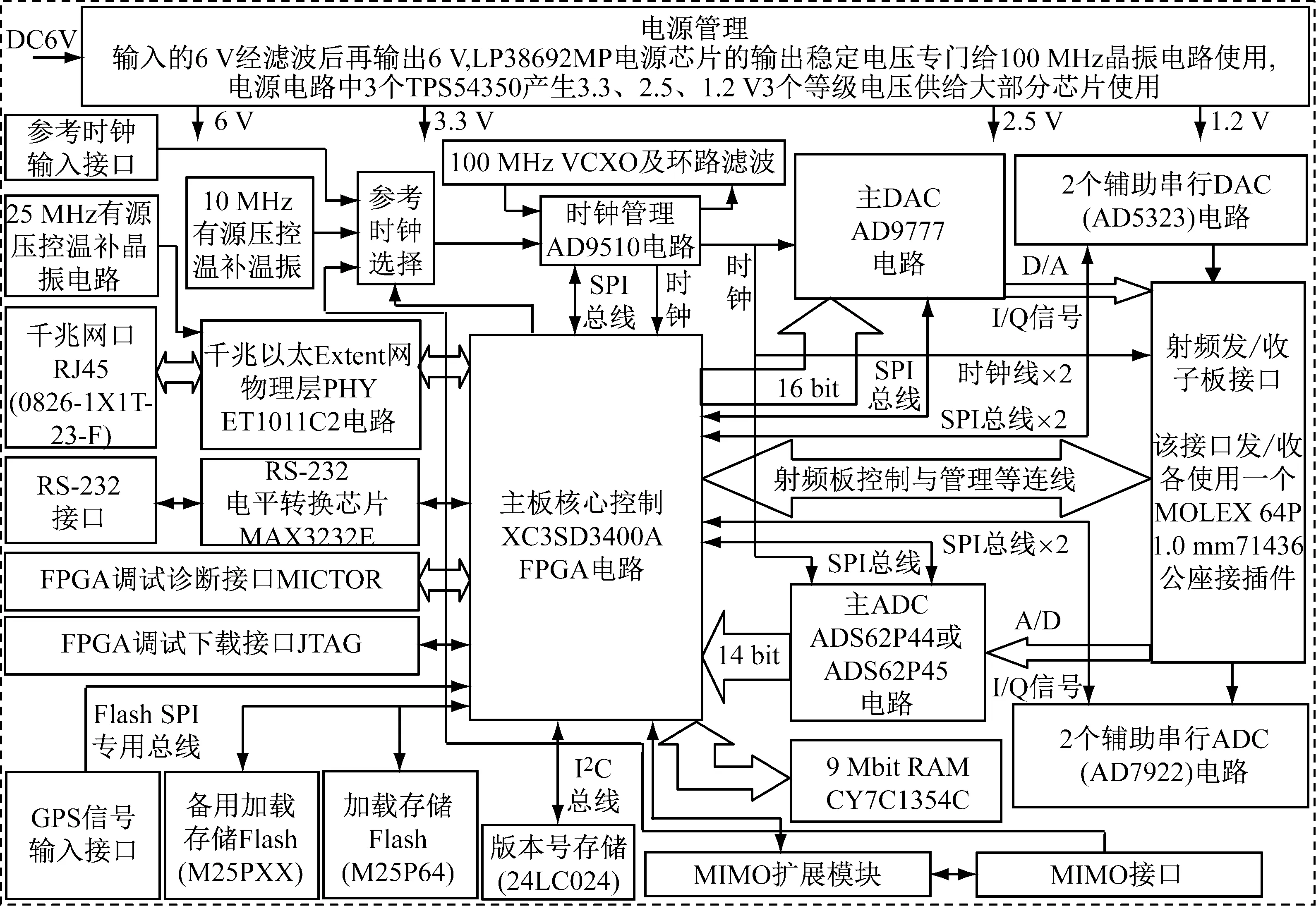

2.1 實驗平臺主板硬件組成

為兼容USRP N210所研制的實驗平臺主板組成模塊如圖3所示[11]。主板采用以XC3SD3400A為核心控制模塊的FPGA電路,處理器及控制程序固件、數字上下變頻UDC/DDC、算法實現等,都在FPGA中實現。高速D/A轉換模塊AD9777和A/D轉換模塊ADS62P45是軟件無線電系統設計中最重要的一步,其中D/A用于將數字域的離散時間信號電壓映射為連續的時間信號,A/D是將模擬域的連續時間信號轉換為數字域的離散時間信號。RAM模塊CY7C1354C用于高速采樣數據的緩存。加載存儲設置M25P64為Flash模塊,開機時通過SPI總線實現對FPGA的加載工作。再有,實驗平臺一些芯片通過調試而獲得的偏執矯正參考值,主要由串行A/D模塊AD7922和串行D/A模塊AD5623實現,也是通過SPI總線進行設置。以太網Extent物理層PHY模塊ET1011C2,用于實驗平臺主板與電腦通過網線實現信號傳輸。LP38692MP和TPS54350為電源模塊,用于給實驗平臺主板中各個芯片和模塊提供穩定電源。時鐘管理模塊AD9510,為實驗平臺主板和子板提供各種穩定的時鐘信號。射頻發/收子板接口為DIN型64針接插件,是連接實驗平臺主板和射頻子板的重要部分。串行儲模塊24LC024,通過I2C總線與FPGA的控制單元連接,主要存儲實驗平臺主板的版本信息。MIMO擴展模塊及其接口,主要是考慮多機級聯使用,進而組成MIMO系統的并行高速接口,采用高速率標準的K碼體制。

2.2 核心硬件電路的主要性能簡介

(1) 核心控制電路XC3SD3400A。XC3SD3400A是Xilinx Spartan-3A DSP系列中的FPGA芯片[12],該芯片的系統門數3400K,等效邏輯單元53712,CLB陣列共5968,差分I/O最多213對。為了具有信號處理的功能增加了最大容量2268K塊RAM和126個DSP48A模塊,塊RAM和DSP48A模塊可運行在250MHz,DSP48A核包含18位×18位乘法器、18位預加法器、48位加法器/減法器、級聯功能,能實現各種信號處理的應用。8個數字時鐘管理器DCMs,擁有自校正全數字解決方案,可以對時鐘信號進行分配、延時、倍頻、分頻和相移操作。輸入/輸出塊IOBs,支持雙向數據流和三狀態操作,支持各種信號標準,包括一些高性能差分標準,包括雙數據速率DDR寄存器等。多電平標準的引腳接口可選擇LVCMOS、LVTTL、HSTL和SSTL單端型I/O,信號可選擇3.3、2.5、1.8、1.5和1.2 V等。每個功能元素擁有相關的可編程開關矩陣,擁有功能豐富的路由功能,可任意連接所有功能模塊。配置接口符合RROMs行業標準,SPI串行Flash配置接口具備CRC校驗功能。利用XC3SD3400A作為實驗平臺主板邏輯核心控制器件,目前被使用的資源約占芯片總資源的37%,還有極大的資源給留給學生繼續深入開發或者功能升級使用。

(2) 數字/模擬和模擬/數字轉換器。實驗平臺主板的數字/模擬轉換器采用了可編程控制的AD9777,通過標準的SPI串行控制接口可實現對芯片的工作方式進行編程控制。AD9777支持最高160 MHz時鐘輸入[13],在實驗平臺主板中輸入的時鐘為100 MHz,AD9777具有內部鎖相環時鐘倍頻器,通過編程控制可使系統最高時鐘可達fs=400 MHz,進而實現400MSPS的最高采樣率。能適應復數正交調信號的I、Q方式應用的雙通道16位D/A。設計有編程可選的2×、4×、8×內插濾波器,以及編程可選的fs/2、fs/4、fs/8正交變頻調制和鏡像抑制功能。可編程多功能輸入數據接口,能適應雙端口或者采用單端口交錯輸入,輸入信號既可以用二進制補碼也可以用標準二進制碼。具有鏡像抑制功能以及可編程的通道增益和偏置調整。

實驗平臺主板的模擬/數字轉換器采用了可編程控制的ADS62P44/P45,通過標準的SPI串行控制接口可實現對芯片的工作方式進行編程控制。ADS62P4X是一個雙通道14位A/D轉換[14],使用一個內部采樣保持和低時鐘抖動緩沖區,ADC支持高信噪比、高輸入頻率下的高SFDR。帶有步進3.5 dB和0.5 dB的粗及細增益控制模塊,通過編程在0~6 dB增益可調,目的是提高SFDR性能以全面適應較低信號輸入范圍。兩個通道最大采樣率均為125×106S/s(SPS)。ADS62P4X包括一個數字處理模塊,它包含幾種有用的和常用的數字功能,例如:ADC偏移校正,每間隔0.05 dB的細調增益校正。可編程的÷2、÷4、÷8倍降采樣抽取和內置自定義濾波器,內嵌一個最大抽頭系數為24的FIR濾波器,可進行低通、帶通、高通濾波。數字輸出接口支持LVCMOS和LVDS兩種電平,通過編程選項可按照并行LVCMOS方式或者雙倍數據速率DDR LVDS輸出轉換后數字。

(3) 時鐘管理AD9510電路。AD9510輸入參考時鐘通過低壓差分多路選擇開關SY98545經過編程選擇,可選擇的參考時鐘有:外部GPS時鐘、MIMO接口時鐘、主板上通過有源壓控溫補晶振VCTCXO產生的精準時鐘。實驗平臺主板默認選擇的參考時鐘是主板VCTCXO產生的10MHz精準時鐘。AD9510具有完整的片上PLL內核[15],僅需外部環路濾波器和VCO/VCXO的配合,實驗平臺主板中AD9510利用PLL和VCO/VCXO及環路濾波器,產生100 MHz內部時鐘。AD9510提供8路獨立的時鐘輸出,其中4路輸出最高可達1.2 GHz的低壓正發射極耦合邏輯(LVPECL),另外4路輸出可選擇為LVDS(800 MHz)或CMOS(250 MHz)。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數分頻比。一路時鐘輸出相對于另一路時鐘輸出的相位可通過分頻器相位選擇功能改變,用作時序粗調。2路LVDS/CMOS輸出具有可編程延遲功能,其滿量程范圍最高為8 ns延遲,該精密調諧延遲模塊具有5位分辨率,提供25種編程延遲設置。

在實驗平臺主板中AD9510的8路獨立時鐘輸出,有2路輸出運用了延遲模塊。其中有4路通過低壓正發射極耦合LVPECL邏輯電平方式輸出100 MHz時鐘,2路分別送給A/D、D/A模塊;1路通過匹配網絡送給FPGA作為主時鐘;1路留給備用測試接口。再有,通過LVCMOS/LVDS邏輯電平方式分2路輸出的100 MHz時鐘,1路送給射頻子板的接收RX時鐘接口;另1路延遲設置2.12712 ns送給發射TX時鐘接口。最后2路輸出,1路通過低壓差分邏輯電平LVDS方式輸出100MHz時鐘后,再經過DS90LT012為3.3 V單端輸出方式后,送給與MIMO模塊有關的FPGA的I/O端口,以及MIMO模塊TLK2701,作為本機FPGA一些I/O端口和MIMO芯片TLK2701的工作時鐘;另1路延遲設置2.12712 ns的10 MHz時鐘通過低壓差分邏輯電平LVDS方式送給MIMO接口,作為實驗平臺級聯時給其他設備的參考時鐘。

再有,實驗平臺主板中XC3SD3400A FPGA內部的數字時鐘管理模塊DCM[12],用于產生FPGA內部模塊需要的各種時鐘。DCM模塊輸出3路不同的時鐘DSP_CLK、WB_CLK、CLK270。其中,DSP_CLK主要用于信號處理部分,作為FPGA中的數據分流、通用可編程I/O接口GPIO、狀態設置寄存器、VITA-49協議狀態機、數字上下變頻、A/D接收及D/A發送等數字處理模塊提供處理時鐘;WB_CLK提供的時鐘主要用于與內部Wishbone總線讀寫相關的模塊,如Wishbone總線時鐘、ZPU處理器讀寫Wishbone時鐘、數據分流模塊讀寫總線時鐘等。CLK270時鐘主要配合外部MIMO接口使用。

3 實驗平臺主板安全模式下的系統

3.1 FPGA安全配置啟動過程

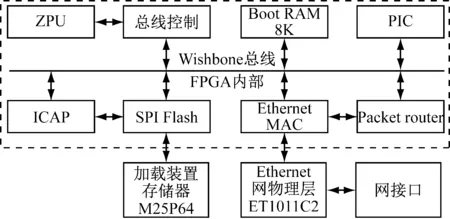

主板上XC3SD3400A的FPGA模塊為核心控制電路,XC3SD3400A擁有專用的多重啟動與動態配置Multi boot邏輯配置模塊及其接口ICAP[12,16]。通過ICAP設置配置模塊中的相關寄存器,實現在不同配置bit流文件中的切換。在啟動實驗平臺時,若沒有從上位機給M25P64Flash加載過硬件驅動(User Hardware Driver,UHD)的配置鏡像文件,或者開機配置過程中檢測安全啟動S2開關控制的引腳為低電平時,僅加載M25P64Flash中不能改動的安全配置鏡像文件,該模塊為自檢加載文件以及最基本的配置鏡像文件。考慮到兼容USRP N210,實驗平臺主板安全配置步驟為:

(1) 從M25P64 Flash的0x00000000地址開始讀Safe_fpga_image對FPGA進行邏輯電路系統的配置,為FPGA配置一個占用很少的資源和構架很小的32位處理器ZPU(Zylin CPU)軟核[17],并配置32位Wishbone總線及其總線控制器[18],以及掛接在Wishbone總線上的專用SPI接口(SPI for Flash)、雙端口哈佛型(Harvard architecture)的引導程序存儲器(Boot RAM)、內部配置訪問端口(Internal Configuration Access Port,ICAP)、可編程中斷控制器(Programmable Interrupt Controller,PIC)、數據包路由器(Packet router)、簡化的以太網數據鏈路媒體層(Ethernet MAC)等模塊。這樣就構建了一個精簡的片上系統(System on Programmable Chip,SoPC)。

(2) 利用狀態機邏輯電路控制內部配置訪問端口ICAP,從M25P64 Flash的0x003F0000地址開始讀取Safe_fw_image可執行程序代碼配置到Boot RAM中,即對ZPU進行可執行代碼的安全配置代碼。

(3) 片上系統開始工作,初始化后ZPU便能夠實現對FPGA的控制,安全配置之后形成的系統如圖4所示。

圖4FPGA安全配置之后構建出的最小工作系統

系統中總線控制器確定ZPU處理器是Wishbone總線的主控制器,其他掛接在Wishbone總線的均為從設備。ZPU有著固定8bit的操作碼,而所有操作數都是32bit,地址總線寬度為16bit。ZPU構成片上系統架構的所有部分如程序計數器PC、堆棧指針SP等,均使用一個帶有雙端口哈佛結構RAM作為數據和代碼的存儲。實驗平臺主板中ZPU總共使用了39條指令,可產生22種工作狀態。

Ethernet MAC模塊中包括Simple_gemac和Simple_gemac_wb兩個模塊[19],Simple_gemac模塊主要完成發送,接收以及流量控制的功能;Simple_gemac_wb主要處理發送和接收來自Wishbone總線以及以太網物理層PHY傳來的管理控制信息。

實驗平臺主板中MAC層之上定義的數據包路由模塊Packet router,是利用Verilog HDL邏輯描述語言進行邏輯抽象實現的,它根據數據發送上下位機的方向,主要完成跨越IP層對UDP頭部的解析或者添加,然后把數據流交給對應的模塊進行處理,所有的網絡數據包經由Packet_router發往FPGA中的目的模塊。Packet_router采用的是一種輕量級IPv4協議LWIP(Light Weight IP)[20],LWIP實現的重點是在保持IPv4協議棧主要功能基礎上減少對資源的占用,且有無操作系統的支持都可以運行,非常適合在片上系統SoPC中使用。在實驗平臺主板的ZPU中運行是LWIP中輕量級UDP/IP協議,其默認的IP地址是192.168.10.2。

3.2 安全模式下實驗平臺主板工作方式

在安全模式配置之后,ZPU將交由雙端口結構的引導程序存儲器(Boot RAM)執行程序代碼。初始化后,通過以太網MII/GMII功能模塊和接口,與上位機進行協議和速率協商和匹配,之后按照協商協議和速率通信。在安全模式工作時,與上位機的以太網通信均需要ZPU控制,且能與上位機通過UDP編號49152的端口進行通信,用來接收上位機的控制信息或實驗平臺主板傳送應答信息。

盡管在安全模式工作下可以正常啟動實驗平臺,但是還不能使用GNU Radio進行無線傳輸數據的收發,若要正常使用實驗平臺,必須將實驗平臺硬件驅動UHD配置鏡像文件裝入主板的M25P64 Flash中。UHD旨在為實驗平臺提供宿主驅動和為GNU Radio提供硬件電路的應用程序規范化訪問接口API。這樣用戶便可獨立使用UHD驅動或靈活同第三方應用軟件,如Gnuradio、Labview或Simulink相配合進行實驗平臺的使用和開發。

考慮到實驗平臺對USRP N210的兼容,上位機通過UDP編號49154的端口同實驗平臺進行通信,實現對實驗平臺的用戶硬件驅動配置UHD(User Hardware Driver)進行固件鏡像及升級。因文章篇幅限制,關于實驗平臺硬件驅動UHD的配置鏡像文件,以及硬件驅動UHD配置之后實驗平臺有關工作原理將另文介紹。

4 結 語

從實用軟件無線電技術的角度,對基于軟件無線電的通信系統實驗平臺總體設計思想,硬件系統構成及核心電路主要性能,安全模式下FPGA的配置等內容的系統介紹。通過這些介紹能夠初步體會到,基于軟件無線電的通信系統實驗平臺總體設計指導思想是:在系統結構上采用層次化和網絡化,在功能設計上采用模塊化和可控化,在信號適應性上采用高速化和寬帶化,在推廣性方面的兼容化。掌握實驗平臺的總體設計思想和系統資源,不僅有助于對實驗平臺工作過程的理解,而且為進一步掌握實驗平臺系統軟硬件工作原理奠定了必要的基礎。在安全模式下實驗平臺主要是構建了一個可編程片上系統SoPC,以及Ethernet網絡通信功能。雖然安全模式下可以正常啟動實驗平臺工作,但是并不能利用上位機的GNU Radio進行無線傳輸數據的收發。若要想充分發揮實驗平臺提供的資源,還需要進一步對其進行配置和驅動,進而構建出完備的無線電工作系統,因此還需要更深入地介紹實驗平臺工作原理。筆者將繼續撰文對如何對FPGA進行在線的重構驅動和配置,進而使實驗平臺構建出一個功能完整系統的方法及工作原理進行闡述。

參考文獻(References):

[1]楊宇紅, 袁焱, 田礫,等. 基于軟件無線電平臺的通信實驗教學[J]. 實驗室研究與探索, 2015, 34(4): 186-188.

[2]葛熠, 陳為剛. 基于嵌入式USRP的無線通信實現[J]. 電子測量技術, 2016, 35(6): 167-171.

[3]孟梅梅, 李曉輝, 劉乃安, 等. 基于NI USRP的多模式自適應無線通信實驗平臺[J]. 現代電子技術, 2016, 39(1): 24-26.

[4]趙楠, 武明虎. 基于GNU Radio和USRP的寬頻帶并行感知平臺設計[J]. 計算機應用研究, 2015, 32(12):3779-3781.

[5]錢建軍, 陳樹新. 基于USRP的GPS基帶信號源設計與實現[J]. 實驗室研究與探索, 2015, 34(10): 72-75.

[6]楊晉生, 李中品. 基于USRP的室內無線信道場強的仿真與測量[J]. 電子測量技術, 2015, 34(5): 131-134.

[7]余兵才, 姚明, 鄧曉華, 等. 基于GNU Radio和USRP新型軟件頻譜分析儀[J]. 現代雷達, 2014, 36(9): 17-21.

[8]魏以民,黃葆華,高媛媛. “通信原理”課程中載波同步的教學方法研究[J]. 電氣電子教學學報, 2013,35(5): 61-65.

[9]Truong N B, Yu C. Investigating latency in GNU software radio with USRP embedded series SDR platform[C]//IEEE International Conference on Broadband and Wireless Computing, Communication and Applications.2013:9-14.

[10]Grayver E. Implementing Software Defined Radio[M]. USA: Springer, 2013.

[11]Ettus Research LLC. USRP N210電路原理圖[EB/OL]. http://files.ettus.com/schematics/n200/n2xx.pdf.

[12]Xilinx Inc. XtremeDSP DSP48A for Spartan-3A DSP FPGAs[DB/OL]. http://www.xilinx.com/support/ documentation/ user_guides/ug431.pdf.

[13]Analog Devices, Inc. AD9777數據手冊[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD-9777.pdf.

[14]Texas Instruments, Inc. ADS62P44/P45數據手冊[EB/OL]. http://www.ti.com.cn/cn/lit/ds/symlink/ads62p44.pdf.

[15]Analog Devices, Inc. AD9510數據手冊[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD-9510.pdf.

[16]李平, 吳曉, 山壽. 基于SPI FLASH的FPGA多重配置[J]. 現代電子技術, 2013,36(22):127-130.

[17]Yvind Harboe, General Manager, Zylin AS. Zylin CPU資料[EB/OL]. http://repo.or.cz/w/zpu.git/blob/HEAD:/zpu/docs/ presentations /zpu.pdf.

[18]Richard Herveille, Open Cores Organization. Wishbone-B4資料[EB/OL]. http://opencores.org/cdn/downloads/wbspec_b4.pdf.

[19]Xilinx Inc. Ethernet MAC資料[EB/OL]. http://www.xilinx.com/support/documentation/ip_documentation/tri_mode_eth_mac/ v5_5/pg051-tri-mode-eth-mac.pdf.

[20]Adam D. Design and Implementation of the LWIP TCP/IP Stack[S]. Swedish Institute of Computer Science, 2001.