高速并行總線接口信號的完整性及設計優化

張敏

摘 要:文章主要針對高速并行總線接口信號問題進行研究,首先提出高速并行總線互連設計以及信號完整性相關概念在此基礎上提出引起信號不完整的發射、串擾、同步開關噪聲以及碼間干擾,針對這些問題提出優化策略。

關鍵詞:高度并行總線;接口信號;完整性;優化

1 高速并行總線接口信號完整性概述

1.1高速并行總線互連設計技術

當今信息技術的發展,促進了電氣性能的提高與高速發展,電氣封裝和互連對于信號而言存在“盒子效應”,不再暢通和透明。在這樣的背景下人們需要采取新的設計方法來保證電氣設計以及電氣性能的實現。在高速并行總線互連設計中也需要考慮這一因素,保證設計的科學性、合理性。

首先,在進行高速并行總線設計中應該結合工程建設中積累獲得的經驗,按照這一設計法則進行高速并行總線設計。其次,在進行高速并行總線互連設計中必須加以量化,對于其性能進行相應預測和評估。

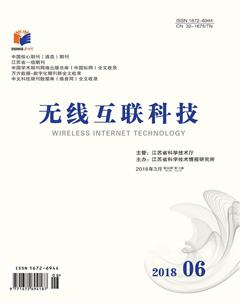

在高速并行總線互連設計中綜合利用經驗法則、解析近似以及數值仿真、實際測量4種技術[1]。高速并行總線領域總體技術布局如圖l所示。

1.2信號完整性概述

信號完整性主要在信號質量上體現,正確的信號時序以及信號電路電壓能夠保證信號響應。當信號準確時序、信號電壓幅值能夠準確地傳輸到IC芯片接收器時,電路就會表現出很好的信號完整性。不能正常將這些信號指標傳輸到接收器或者傳輸質量不佳的情況,均屬于信號完整性較差。出現信號完整性問題不僅僅是由單一因素引起的,一般是眾多因素共同作用的結果。導致信號完整性問題的產生因素包括:元器件布局不合理、芯片開關速度過快、高速信號布線存在問題等,在這些單一因素或綜合因素的作用下,系統數據傳輸不正確,導致整個電路出現問題甚至不能工作。

信號完整性的本質在于保證信源信號能夠被接受方正確識別,即使信號傳輸過程中信道比較復雜。當前電磁環境越來越復雜,傳輸線效應顯著,信號在傳輸中由于復雜的電磁環境會受到衰減,串擾等因素而出現振鈴、過沖等問題,導致接收端信號不能完整接收識別,雙方通信難以正常進行。

對于高速并行總線接口信號完整性而言,就是要通過合理手段來規避信號傳輸過程中存在的問題從而正確地傳送到接收端,保證信號參量容限的合理性[2]。

2 反射噪聲分析與端接技術

2.1反射噪聲原因

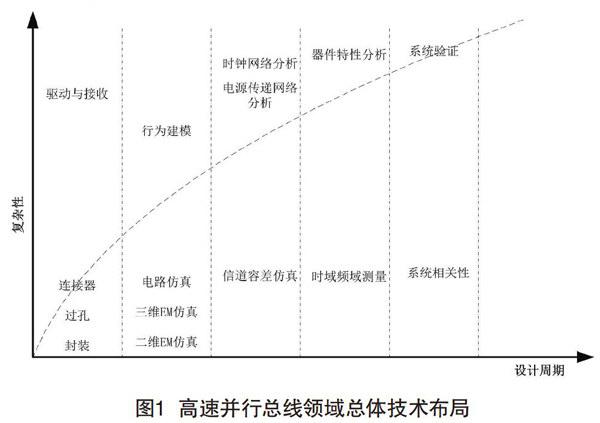

信號在傳輸線中進行傳輸中,信號幅度主要受到阻抗的影響,阻抗還會受到緩沖器電壓、源電阻和傳輸線的影響。如圖2所示,傳輸線終端會接一個和傳輸線特征阻抗精確匹配的阻抗。端接到地的信號幅度為V,在傳輸線上進行傳輸的過程中電壓能夠保持V值,這種情況下V值叫作直流穩態值。當傳輸線終端所接的阻抗和傳輸線上的特征阻抗不匹配的時候,信號中會存在端接到地的部分,剩余的其他信號部分能夠反射回傳輸線,反射方向沿著朝信號源的方向。反射的衡量指標是反射系數,給定接點出反射電壓和入射電壓的比值。在電路以及信號傳輸過程中,反射問題顯著。

2.2消除反射的匹配方案

對于數字系統而言,其性能會受到傳輸線發射的嚴重負面影響,一般可以通過合理的方法規避或減弱反射導致的不良影響。

(1)降低系統頻率。通過對系統的頻率進行降低,能夠保證信號在傳輸到傳輸線之前達到穩態。這種消除反射的方法必須以降低系統工作頻率、犧牲系統運行速度為前提,在高性能要求的系統中不適用。

(2)通過印制電路板(Printed Circuit Board,PCB)走線的縮短,實現發射穩態所需時間的減少。這一消除反射的方法的設計中必須增加PCB板層數,這樣導致工程建設的成本增加,在實際的生活生產中不常用,而且在理論上也存在局限性。

(3)針對傳輸線兩端的阻抗而言,可以在分別端另外添加一個阻抗,添加的阻抗和傳輸線特征阻抗相同,通過阻抗的添加來消除發射[3]。

3 串擾噪聲及其優化

3.1串擾噪聲

串擾主要是針對信號傳輸過程中電磁耦合而言,一般容性、耦合感性、耦合與輻射、耦合均會引起傳輸線中產生不期望電壓噪聲干擾,電流和電壓是串擾形成的直接原因。

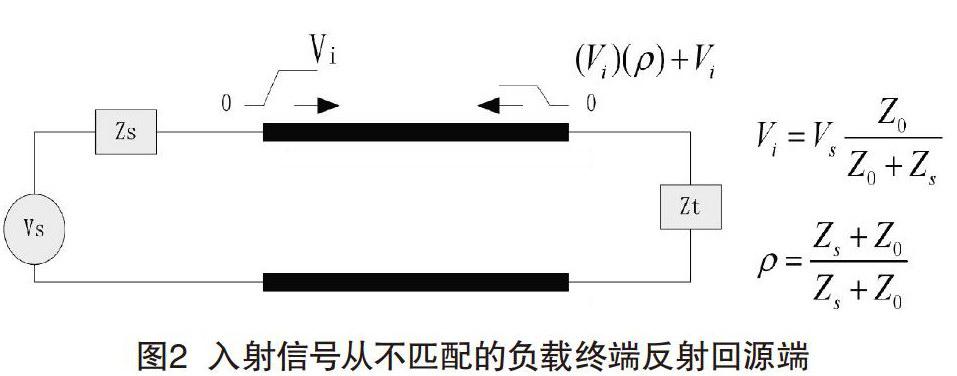

串擾會對線路信號傳輸造成危害:(l)串擾會對傳輸過程中有效特征阻抗和傳播速度產生直接的影響,從而影響系統的時序,進而對信號完整性產生不良影響,對于高速并行總線中的傳輸線性能而言也有所改變。(2)對于其他傳輸線而言,也會因為串擾引起感應噪聲,最終影響信號完整性,主要是對噪聲容限的影響。串擾干擾源與被干擾對象分析如圖3所示。

3.2串擾優化設計

在高速并行走線互連設計中必須考慮串擾噪聲影響,一般可以通過以下手段進行優化設計,盡可能減小串擾。

(l)首先在電路元器件的選型方面,盡可能選擇邊沿速率較慢的元器件,從而最大限度地減少串擾的影晌。(2)可以通過增大線間距來減小平行走線長度來降低串擾干擾。(3)在進行目標阻抗的設計過程中,應該減小介質層的厚度,這樣能夠讓導體靠近地平面,更好、更緊密地和地平面耦合,最大限度地減小對臨近信號線的串擾。(4)采取正確的端接,可以很好地減小反射甚至能夠消除反射,這樣能夠減小串擾[4]。

4 同步開關噪聲及其優化

4.1同步開關噪聲形成及其危害

同步開關噪聲( Simultaneous Switching Noise,SSN)主要是由于多個輸出緩沖器發生轉換的過程中會產生電流以及電壓的突然變化,正是由于這個變化最終導致線路噪聲。當電流發生快速變化的時候,電源和地引腳上的電壓會發生較大變化,最終引起電源完整性的變化,對電源完整性也會發生變化。

4.2同步開關噪聲優化設計

同步開關噪聲是高速并行總線運行中必不可少的串擾影響因素,因此必須進行優化設計:(l)采取差分輸出驅動器來作為接收器進行信號處理,尤其是對于選通信號以及時鐘信號等至關重要的信號而言。(2)對于電容選擇而言,可以選用旁路電容等去耦電容來減小同步開關噪聲影響。(3)減慢電路中邊沿變化率。(4)在電路設計中可以選用比較寬的電源線,對于焊絲盡可能比鉸短,這樣能夠最大限度地減小通路中的電感。

5 碼間干擾及其消除

5.1碼間干擾概述

在信號進行傳輸的過程中,復雜的電磁環境以及信號環境必然導致反射、串擾以及其他相關的噪聲影響。這些影響會以信號的形式顯示在傳輸線上,對于時序容限以及信號完整性容限造成直接的影響,這些影響統稱為碼間干擾。

5.2消除碼間干擾設計

消除碼間干擾可以從以下幾個方面入手:(l)針對阻抗不連續問題,進行消除,可以通過源自封裝以及插槽等方式增加走線分支長度,而且可以使得寄生效應最小化,最終在高速并行總線上反射也會最小。(2)對于互連通路而言,要使其盡可能短。(3)在電路設計以及規劃中,應該盡可能地規避彎曲走線,避免耦合。(4)在選擇線長的過程中要合理、科學,在保證信號正常傳輸的前提下,保證信號完整性網。

6結語

在高速并行總線發展的過程中,時鐘頻率也越來越高,這樣導致互連鏈路中的各個參數對于線路的信號完整性產生直接影響,對于高速并行總線接口以及相關設計造成極大阻礙。在這樣的背景下,必須要采用新的設計方法以及新的設計理念,對于影響信號完整性的反射、碼間干擾、串擾以及同步開關噪聲等因素進行優化設計,保證信號完整性。

[參考文獻]

[1]緱祈科,王妮兒,任崇玉.PCB參數對USB3.0信號完整性的影響[J]蘭州理工大學學報,2017 (6):1-5

[2]孔繁,盛衛星,馬曉峰,等.高速背板互連的信號完整性仿真方法[J]系統工程與電子技術,2014 (10):2082-2088

[3]高曉宇,楊龍劍.高速串行通道的信號完整性問題分析[J]通信技術,2013 (6):44-47

[4]張超,余綜.基于DDR3系統互聯的信號完整性設計[J]計算機工程與設計,2013 (2):616-622

[5]周路,賈寶富.信號上升或下降時間對高速電路信號完整性影響的研究[J]現代電子技術,2011(6):69-73,77