一種NMOS管體區(qū)漏電特性的研究*

李 路,喬 明

(電子科技大學(xué),成都 610054)

1 引言

在高壓柵驅(qū)動集成電路中,通常需要10~25 V的CMOS器件結(jié)構(gòu)[1-5],電路中高壓器件及高壓隔離島占據(jù)整個芯片面積較少,中等電壓的邏輯控制部分占據(jù)了較大面積。隨著超大規(guī)模集成電路特征尺寸的縮小,將更小的線寬用于高壓電路中成為趨勢,同時給工藝要求帶來更大的挑戰(zhàn)[6]。

本文基于0.35μm BCD工藝,制備了用于高壓柵驅(qū)動集成電路的25 V的CMOS結(jié)構(gòu),流片結(jié)果顯示NMOS管反向有較大漏電流產(chǎn)生。針對失效結(jié)果進行了仿真分析,找到失效原因,并提出了改進方案,結(jié)合方案中新的工藝改進,最終流片結(jié)果符合電路應(yīng)用要求。

2 NMOS的測試仿真分析

2.1 NMOS測試分析

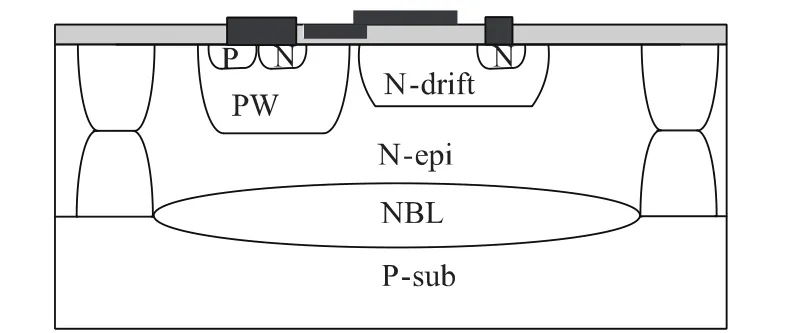

如圖1為NMOS結(jié)構(gòu)圖,其主要工藝為:(1)P型襯底上注入并高溫推結(jié)形成N型埋層NBL;(2)生長N型外延層N-epi;(3)注入P型材料推結(jié)形成PW;(4)注入N型材料推結(jié)形成N-drift;橫向隔離采用結(jié)隔離技術(shù)。

圖1 NMOS結(jié)構(gòu)圖

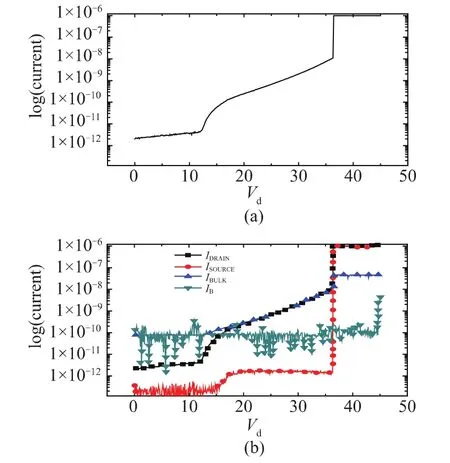

圖2 (a)為NMOS反向耐壓測試曲線,流片測試結(jié)果顯示,低壓NMOS管關(guān)態(tài)靜態(tài)電流出現(xiàn)過大的問題,在漏壓為20 V時漏電已達1 nA量級。為了明確找出漏電路徑,對每個端口的電流進行監(jiān)測,如圖2(b)所示。可以看出,當漏極電壓大于10 V時,隨著漏壓增加,漏電流和體區(qū)電流Ibulk也逐漸增加,兩者幾乎相等。此時源級IS和Vb端電流很小,可以忽略。直到漏壓等于36 V左右,器件發(fā)生擊穿,源級電流劇烈增加,和漏極電流幾乎保持相等。結(jié)果可初步判定漏電主要來自bulk端體區(qū)。

圖2 NMOS漏電監(jiān)測曲線圖

2.2 NMOS仿真分析

本文采用Tsuprem4工藝仿真,為了方便監(jiān)測電流,將源電極和體區(qū)電極分開。……