一種針對(duì)時(shí)變干擾信號(hào)的空時(shí)抗干擾算法研究*

劉東輝,喬瑞萍

(西安交通大學(xué)電子與信息工程學(xué)院,陜西 西安710049)

0 引言

目前車(chē)載導(dǎo)航定位系統(tǒng)大多采用北斗導(dǎo)航接收機(jī)進(jìn)行定位。由于導(dǎo)航信號(hào)的功率小,并且存在噪聲干擾以及來(lái)自無(wú)線(xiàn)廣播、惡劣天氣等其他形式的干擾。脈沖干擾可用帶通濾波器加以濾除,而對(duì)于帶內(nèi)干擾需要使用軟件無(wú)線(xiàn)電技術(shù)進(jìn)行處理以及自適應(yīng)抗干擾處理[1]。在自適應(yīng)抗干擾處理技術(shù)中有空域抗干擾,時(shí)域抗干擾以及頻域抗干擾技術(shù)。目前的應(yīng)用實(shí)例中,空時(shí)抗干擾技術(shù)已成為導(dǎo)航接收機(jī)主要的發(fā)展方向。本文分析了空時(shí)抗干擾技術(shù)架構(gòu),對(duì)基于空時(shí)抗干擾技術(shù)的高斯賽德?tīng)査惴ǎ嗉?jí)維納濾波算法進(jìn)行了研究和仿真[2]。高斯賽德?tīng)柕惴ㄓ?jì)算量小,利用序列數(shù)據(jù)對(duì)權(quán)值不斷的迭代更新,完成對(duì)干擾信號(hào)進(jìn)行處理,然而當(dāng)干擾信號(hào)動(dòng)態(tài)變化時(shí),高斯賽德?tīng)査惴ǖ鷷r(shí)間較長(zhǎng),無(wú)法實(shí)時(shí)處理時(shí)變干擾信號(hào)。多級(jí)維納濾波算法復(fù)雜度較高,利用等長(zhǎng)度的數(shù)據(jù)塊計(jì)算權(quán)值,然而當(dāng)干擾信號(hào)改變時(shí),多級(jí)維納濾波無(wú)法對(duì)干擾信號(hào)狀態(tài)(干擾功率、干擾方向、頻率)轉(zhuǎn)換處的信號(hào)進(jìn)行處理。因此本文提出了高斯賽德?tīng)査惴ê投嗉?jí)維納濾波算法相結(jié)合的方法,實(shí)現(xiàn)了對(duì)時(shí)變干擾信號(hào)處理,并可以滿(mǎn)足實(shí)時(shí)性的要求,更適應(yīng)復(fù)雜多變的干擾環(huán)境。

1 空時(shí)抗干擾技術(shù)

1.1 空時(shí)濾波架構(gòu)

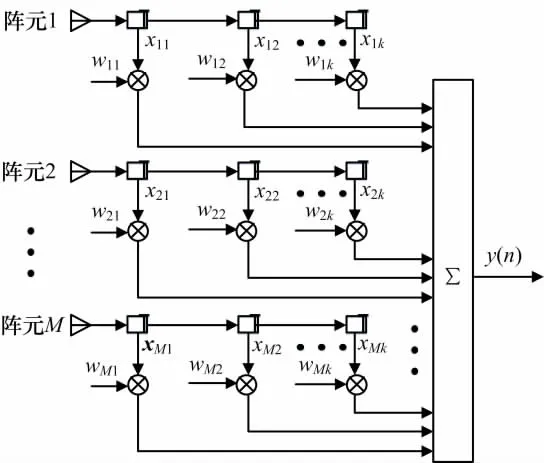

空時(shí)濾波技術(shù)的核心思想是天線(xiàn)陣列對(duì)衛(wèi)星信號(hào)進(jìn)行空域采樣,構(gòu)成了空時(shí)抗干擾的空域部分。每個(gè)天線(xiàn)通道的橫向延時(shí)構(gòu)成了空時(shí)抗干擾的時(shí)域部分[2]。空時(shí)抗干擾首先根據(jù)天線(xiàn)陣列的各個(gè)陣元之間的相位差進(jìn)行空域?yàn)V波,使某個(gè)方向的干擾信號(hào)得到衰減,然后對(duì)每個(gè)陣元接收的時(shí)域信號(hào)進(jìn)行時(shí)域?yàn)V波處理,使某些頻率的干擾信號(hào)得到衰減,從而達(dá)到了空時(shí)二維處理。空時(shí)濾波架構(gòu)如圖1所示。

圖1 空時(shí)濾波架構(gòu)

在圖1中,導(dǎo)航信號(hào)以及干擾信號(hào)經(jīng)過(guò)M 個(gè)天線(xiàn)陣元采集,并經(jīng)過(guò)延時(shí)單元,輸入到抗干擾信號(hào)處理板中,信 號(hào) 為 X = [x11,x12,…,x1k,…,xM1,xM2,…,xMk]。每個(gè)輸入信號(hào)的權(quán)系數(shù),即權(quán)值為W=[w11,w12,…,w1k,…,wM1,wM2,…,wMk]T。因 此 輸 出 信號(hào)為y=WHX,通過(guò)權(quán)值W 完成了對(duì)導(dǎo)航信號(hào)的處理。

1.2 高斯賽德?tīng)柕惴?/h3>

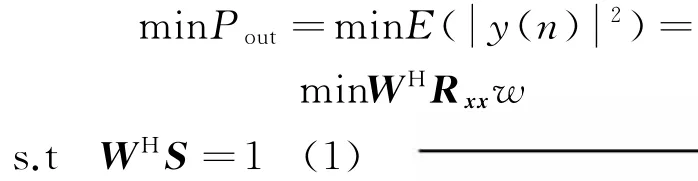

在一般情況下,GPS導(dǎo)航信號(hào)采用擴(kuò)頻形式進(jìn)行傳輸。在傳輸過(guò)程中,噪聲加干擾信號(hào)的功率比導(dǎo)航信號(hào)的功率強(qiáng)的多,衛(wèi)星信號(hào)會(huì)淹沒(méi)在噪聲信號(hào)和干擾信號(hào)中,因此需要約束導(dǎo)航信號(hào)方向上wHS=1,調(diào)制其他權(quán)值使輸出信號(hào)的功率最小,達(dá)到了干擾信號(hào)的抑制目的[3],即:

式中,Rxx為陣列接收信號(hào)(有用信號(hào)、干擾信號(hào)、噪聲)的自相關(guān)矩陣,S=[1,0,…,0]T為約束矩陣,即約束第一個(gè)陣元的權(quán)值為1,由拉格朗日乘子法可得,權(quán)值:

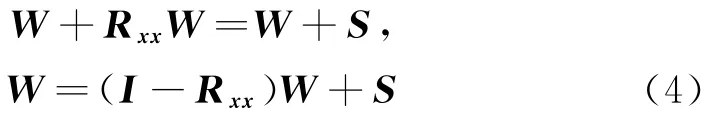

當(dāng)干擾信號(hào)為平穩(wěn)干擾信號(hào)時(shí),1/(SHS)為定值,可假設(shè)權(quán)值為W=S,將公式左右同時(shí)乘以Rxx可得到權(quán)值求解式:

將公式兩邊都加上W可得:

可得權(quán)值迭代公式:

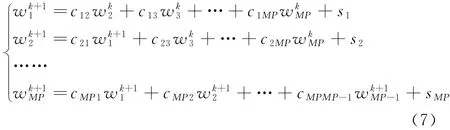

式中,C迭代算法的系數(shù)矩陣,I為單位矩陣。利用Guass-Seidel迭代法可表示為:

可得如下所示迭代格式:

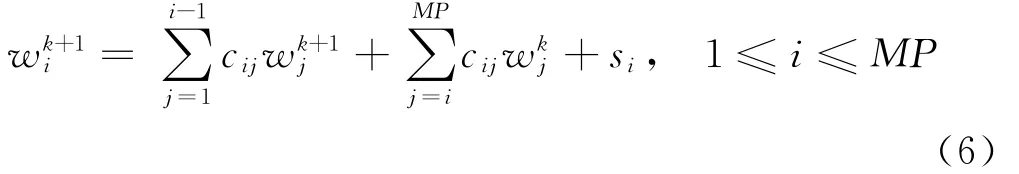

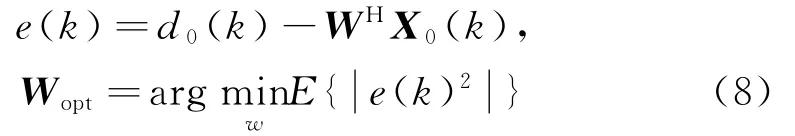

1.3 多級(jí)維納濾波降維算法

在導(dǎo)航信號(hào)的方向未知的情況下,假設(shè)天線(xiàn)陣列第一個(gè)陣元收到的信號(hào)為期望信號(hào)d0(k),設(shè)存在權(quán)值W使輸出信號(hào)WHX0(k)與期望信號(hào)d0(k)的誤差e(k)最小,即:

通過(guò)最陡下降法,根據(jù)E(e(k)2)/W =0,可得到空時(shí)自適應(yīng)濾波權(quán)值為:

對(duì)式(9)需要進(jìn)行矩陣求逆運(yùn)算,計(jì)算量較大,在實(shí)際工程應(yīng)用中會(huì)造成設(shè)備成本較高,因此考慮使用多級(jí)維納濾波器進(jìn)行實(shí)現(xiàn)[4]。多級(jí)維納濾波器分為前向遞推與后向解析過(guò)程,其結(jié)構(gòu)如圖2所示。

圖2 多級(jí)維納濾波器

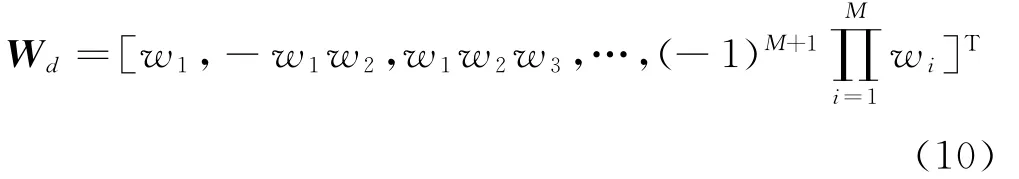

前向遞推過(guò)程利用選通矩陣hk和阻塞矩陣Bk將輸入信號(hào)分解為期望信號(hào)d(k)和不含期望信號(hào)的信號(hào)x(k),通過(guò)前向遞推的多級(jí)分解將輸入信號(hào)分解不含干擾信號(hào)的導(dǎo)航信號(hào),此時(shí)前向遞推濾波器完成了信號(hào)的前向分解作用[4]。在后向解析濾波器中,通過(guò)對(duì)每一級(jí)的分解的誤差向量與上一級(jí)期望向量的運(yùn)算得到了每一級(jí)分解的權(quán)值Wd:

并通過(guò)與選通矩陣與阻塞矩陣進(jìn)行運(yùn)算得到了多級(jí)維納濾波權(quán)值:

多級(jí)維納濾波器等效權(quán)值:

1.4 結(jié)合算法

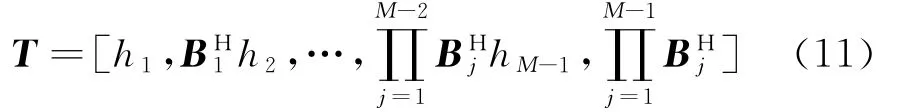

在動(dòng)態(tài)干擾環(huán)境中,由于干擾信號(hào)的參數(shù)發(fā)送變化,高斯賽德?tīng)査惴ㄊ諗枯^慢,不能有效地處理實(shí)時(shí)信號(hào)。多級(jí)維納濾波算法求解權(quán)值需要計(jì)算一定長(zhǎng)度的數(shù)據(jù)塊,在干擾信號(hào)狀態(tài)(功率、干擾方向、頻率)轉(zhuǎn)換的時(shí)間段里,多級(jí)維納濾波算法不能對(duì)干擾信號(hào)有效處理。本文針對(duì)時(shí)變干擾信號(hào)的特點(diǎn),結(jié)合高斯賽德?tīng)柕投嗉?jí)維納濾波算法,提出了高斯賽德?tīng)柕惴ê投嗉?jí)維納濾波算法相結(jié)合計(jì)算權(quán)值的的方法。結(jié)合算法流程圖如圖3所示。

圖3 結(jié)合算法流程圖

結(jié)合算法計(jì)算權(quán)值步驟為:

1)將接收信號(hào)分為三個(gè)支路傳輸?shù)娇垢蓴_算法處理模塊。其中一個(gè)支路是將接收信號(hào)以數(shù)據(jù)塊的形式傳輸?shù)紻SP里。在DSP里利用數(shù)據(jù)塊計(jì)算多級(jí)維納濾波算法權(quán)值;

2)同時(shí)另一支路數(shù)據(jù)實(shí)時(shí)的傳輸?shù)皆贔PGA里,并在FPGA里利用高斯賽德?tīng)柕惴ㄖ瘘c(diǎn)計(jì)算權(quán)值WGS,使用權(quán)值WGS進(jìn)行波束合成,得到空時(shí)抗干擾輸出信號(hào)y=X;

3)在DSP支路計(jì)算出多級(jí)維納濾波算法權(quán)值Wmwf后,將該權(quán)傳輸?shù)紽PGA里。在FPGA里將更新并在權(quán)值Wmwf的基礎(chǔ)上繼續(xù)進(jìn)行迭代更新,利用多級(jí)維納濾波算法權(quán)值提高了高斯賽德?tīng)査惴ǖ俣龋箼?quán)值WGS快速達(dá)到局部最優(yōu)解,并進(jìn)行波束合成,得到輸出信號(hào)Y=X;

4)不斷循環(huán)上述3個(gè)步驟。

2 算法仿真

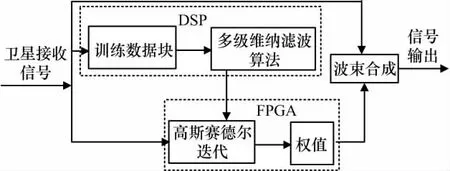

在對(duì)空時(shí)抗干擾算法理論分析后,需要對(duì)每種算法進(jìn)行性能驗(yàn)證。首先給出本文的仿真環(huán)境;假設(shè)采用均勻圓陣進(jìn)行仿真,陣元數(shù)M 為4,抽頭數(shù)P為5,陣元延時(shí)為3,陣元中心距為0.5λ。干擾信號(hào)為三段多音干擾信號(hào),每段干擾信號(hào)由3個(gè)不同干擾方向的多音信號(hào)組成。每段干擾信號(hào)的干噪比,干擾方向,干擾頻率隨時(shí)間變化,具體參數(shù)如下表1所示。

表1 時(shí)變干擾信號(hào)參數(shù)

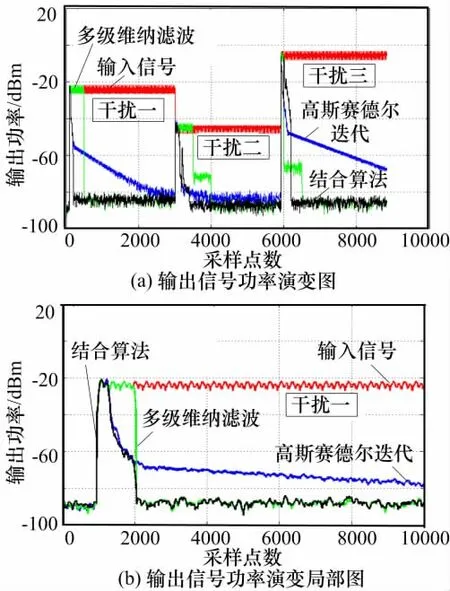

在表1的時(shí)變干擾信號(hào)仿真環(huán)境下,高斯賽德?tīng)柕惴ǎ嗉?jí)維納濾波算法以及結(jié)合算法仿真結(jié)果如圖4所示。

觀察圖4(a)輸出信號(hào)功率圖,當(dāng)干擾信號(hào)動(dòng)態(tài)變化時(shí),高斯賽德?tīng)査惴ㄊ諗枯^慢,最優(yōu)權(quán)值的迭代過(guò)程較長(zhǎng),不能有效地對(duì)干擾信號(hào)進(jìn)行處理。在干擾信號(hào)狀態(tài)(干擾方向、干擾功率)轉(zhuǎn)變的時(shí)間段里,即在每段干擾信號(hào)前端部分,多級(jí)維納濾波算法不能有效地對(duì)該段干擾信號(hào)進(jìn)行處理。

通過(guò)圖4(b)的局部輸出信號(hào)功率圖,在干擾信號(hào)狀態(tài)轉(zhuǎn)換的時(shí)間段里,結(jié)合算法利用高斯賽德?tīng)柕惴▽?duì)該段干擾信號(hào)進(jìn)行處理。對(duì)于該段時(shí)間里的干擾信號(hào),可以進(jìn)行一定程度的抑制,仿真效果與高斯賽德?tīng)査惴ǚ抡嫘Ч嗤M瑫r(shí)當(dāng)多級(jí)維納濾波算法計(jì)算出權(quán)值后,該權(quán)值會(huì)被更新為高斯賽德?tīng)査惴?quán)值,并在該權(quán)值的基礎(chǔ)上進(jìn)行迭代,提高了高斯賽德?tīng)査惴ㄊ諗克俣取?duì)于后續(xù)的干擾信號(hào),可通過(guò)最優(yōu)權(quán)值進(jìn)行處理。通過(guò)仿真和分析可得:本文提出的結(jié)合算法能夠結(jié)合高斯賽德?tīng)柕惴ê投嗉?jí)維納濾波算法優(yōu)勢(shì),有效地對(duì)時(shí)變干擾信號(hào)進(jìn)行抑制。

圖4 算法仿真結(jié)果

3 硬件仿真

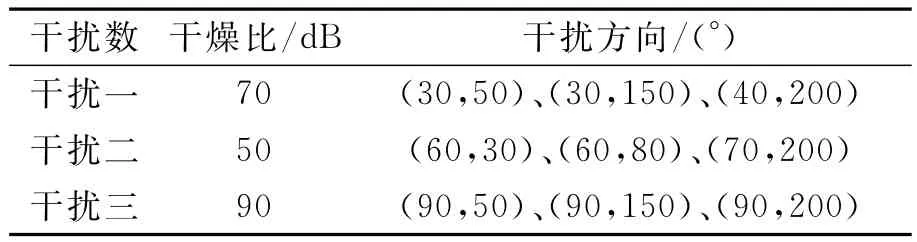

3.1 OMAPL138雙核協(xié)同仿真

本文采用基于OMAPL138芯片的雙核協(xié)同仿真架構(gòu)進(jìn)行算法移植,其中ARM芯片為主處理器,DSP為32位浮點(diǎn)型協(xié)處理器,在實(shí)際應(yīng)用中ARM大多作為系統(tǒng)的調(diào)度和設(shè)備管理,DSP負(fù)責(zé)算法處理和數(shù)據(jù)處理[5]。

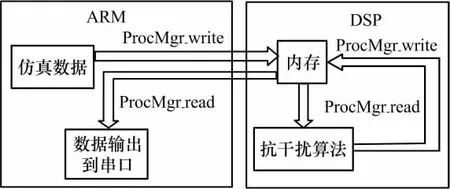

雙核協(xié)作工作過(guò)程為ARM使用ProcMgr_Write組件[6]將仿真數(shù)據(jù)寫(xiě)進(jìn)DSP內(nèi)存中,并使用Notify函數(shù)通知DSP進(jìn)行算法處理。DSP接收到Notify通知后從內(nèi)存中讀出仿真數(shù)據(jù)并進(jìn)行數(shù)據(jù)的重組,并調(diào)用抗干擾算法計(jì)算權(quán)值,算法執(zhí)行結(jié)束后,DSP給ARM發(fā)送Notify算法完成通知。ARM端接收到DSP的算法完成Notify通知后,使用ProcMgr_read組件從DSP內(nèi)存中讀出權(quán)值并通過(guò)RS232串口將數(shù)據(jù)傳輸?shù)街鳈C(jī)上,在主機(jī)上利用Matlab繪制出DSP硬件仿真輸出信號(hào)功率演變圖。綜上所述雙核協(xié)同仿真架構(gòu)如圖5所示.

3.2 實(shí)現(xiàn)結(jié)果

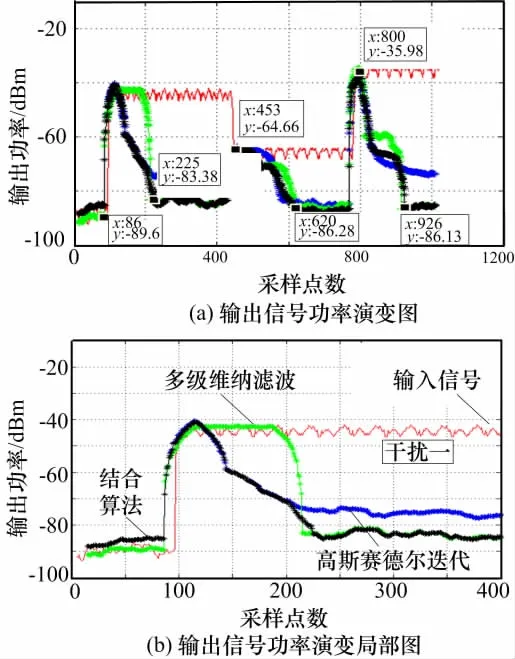

硬件仿真環(huán)境采用第2節(jié)的仿真環(huán)境,仿真數(shù)據(jù)為MATLAB仿真時(shí)變干擾信號(hào)數(shù)據(jù)。分別對(duì)三種算法進(jìn)行DSP移植,并繪制出輸出信號(hào)功率圖如圖6所示。

圖5 雙核協(xié)作仿真架構(gòu)

圖6 DSP仿真功率輸出圖

仿真分析:一般車(chē)載導(dǎo)航系統(tǒng)對(duì)于接收機(jī)抗干擾算法的最大反應(yīng)時(shí)間為100ms。根據(jù)抗干擾算法對(duì)干擾信號(hào)的反應(yīng)時(shí)間t的計(jì)算公式t=(xlastxfirst)/fs,式中xfirst表示輸出信號(hào)中存在干擾信號(hào)的第一個(gè)采樣點(diǎn),xlast表示輸出信號(hào)中干擾信號(hào)完全被抑制的第一個(gè)采樣點(diǎn)。fs表示輸出信號(hào)的采樣頻率(62MHz),由圖6(a)的輸出信號(hào)功率演變圖可得,結(jié)合算法的對(duì)干擾信號(hào)的反應(yīng)時(shí)間為2.323ms,能夠滿(mǎn)足車(chē)載導(dǎo)航系統(tǒng)對(duì)抗干擾算法的實(shí)時(shí)性指標(biāo)。同時(shí)結(jié)合圖6(b)的輸出信號(hào)功率局部演變圖,可得結(jié)合算法能夠?qū)r(shí)變干擾信號(hào)的硬件仿真效果相對(duì)高斯賽德?tīng)柕惴ā⒍嗉?jí)維納濾波算法性能較好。

4 結(jié)束語(yǔ)

本文針對(duì)空時(shí)抗干擾技術(shù)進(jìn)行了闡述,并對(duì)高斯賽德?tīng)柕惴ǎ嗉?jí)維納濾波算法進(jìn)行了理論分析和仿真驗(yàn)證。提出了針對(duì)時(shí)變干擾信號(hào)可利用多級(jí)維納濾波算法與高斯賽德?tīng)査惴ㄏ嘟Y(jié)合的算法。通過(guò)時(shí)變干擾信號(hào)仿真驗(yàn)證,結(jié)合算法能夠有效的對(duì)時(shí)變干擾信號(hào)的進(jìn)行處理,且具有實(shí)時(shí)性好,干擾抑制能力強(qiáng)的特點(diǎn)。同時(shí)本文對(duì)三種算法進(jìn)行了DSP硬件仿真,驗(yàn)證了結(jié)合算法的硬件移植效果,完成了算法的硬件實(shí)現(xiàn),為實(shí)際工程應(yīng)用奠定基礎(chǔ)。■