基于MAX9259/MAX9260的CameraLink圖像數據光纖傳輸技術

陳洋君,吳志勇,崔 明,張維達,范日召

(1.中國科學院 長春光學精密機械與物理研究所,吉林 長春 130033; 2.中國科學院大學,北京 100049)

1 引 言

隨著數字圖像[1]數據量的急劇增加,傳輸速率的不斷提高[2],以及為了滿足數據處理相關性高,長距離傳輸等需求,對傳輸系統的要求越來越高。本文采用一種基于SerDes芯片組MAX9259/9260的串行/解串行技術,并將其應用到base型Cameralink光纖傳輸系統的串并轉換模塊中。即CameraLink接口作為相機和圖像采集卡間的通信接口,以FPGA為核心實現了數據的采集和預處理,以MAX9259/9260作為系統的串行收發器,經光纖傳輸后,最終實現了圖像數據的遠程無失真傳輸。

作為工業數字相機的主要圖像輸出接口之一的Cameralink接口,采用并串結合的方式實現大數據量的傳輸,該接口具有實時性好和抗干擾能力強的優點。同時光纖通信[3]具有抗噪聲干擾性強、抗電磁干擾、通信容量大、保密性強,適于遠距離傳輸等優點,可以提高圖像傳輸的速率和可靠性。傳統系統中,串并轉換模塊大多采用TLK2711[4]等,由于不能提供足夠的并行總線,需要通過內部實現時分復用/解復用以及圖像重組,同時還存在圖像數據時鐘域的匹配問題等,大大增加了開發難度。與傳統的光纖傳輸系統相比,本系統選取了功能強大,應用廣泛的SerDes芯片組MAX9259/X9260作為串行收發器,其與傳統的串行收發器TLK2711等相比,省去了時分復用/解復用和時鐘域匹配操作,大大降低了CameraLink光纖通信的開發難度,同時提高了系統的適應性。

2 基于CameraLink接口的光纖傳輸技術

2.1 關于CameraLink接口

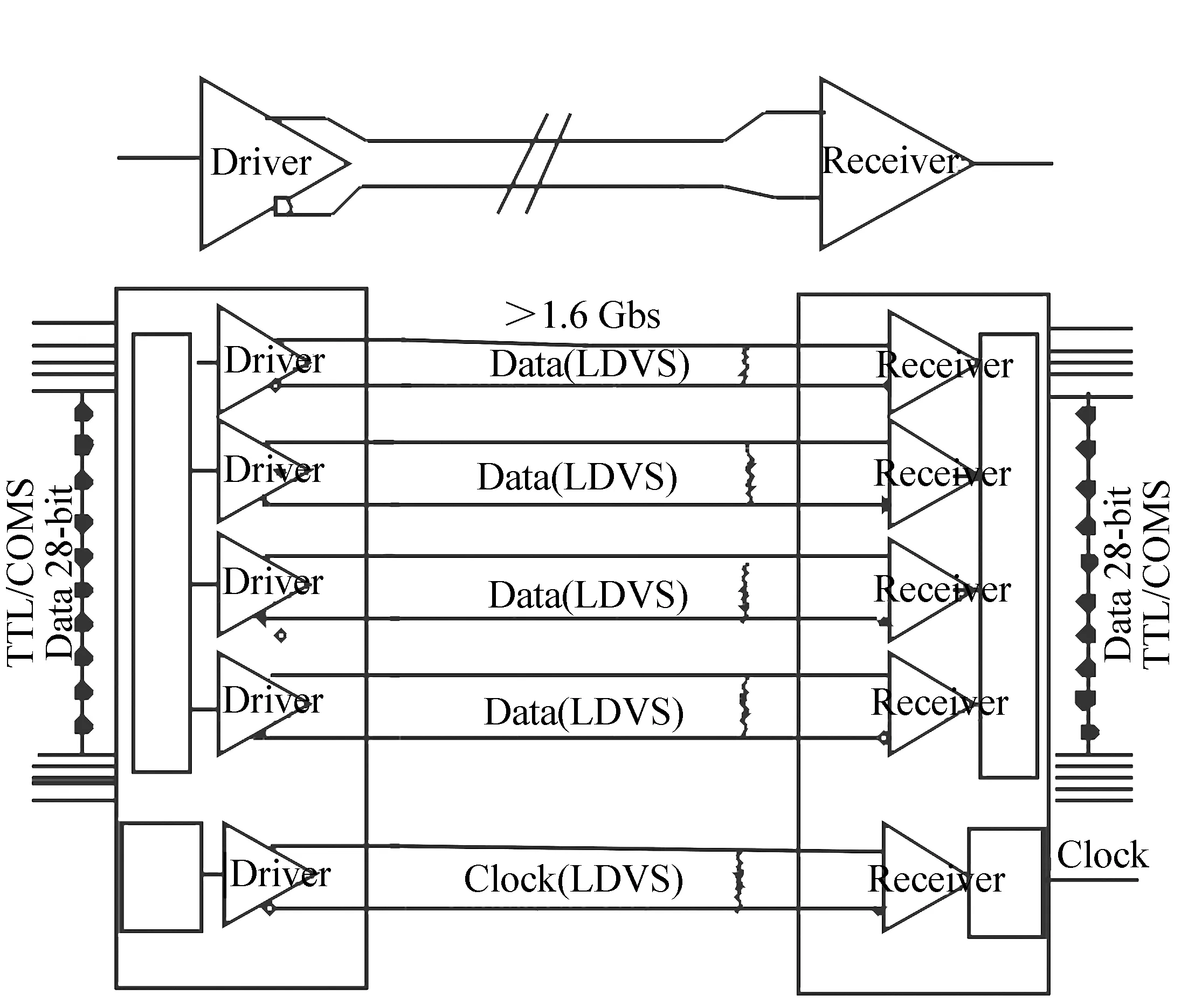

CameraLink接口是一種視頻應用的通用接口,是ChannelLink技術的擴展[5],它為相機和圖像采集卡提供了一種標準連接。CameraLink接口采用了多路低電壓差分信號(Low Voltage Differential Signal,LVDS)進行通信,其傳輸速率可達到2.38 Gb/s。CameraLink接口由一個驅動器和一個接收器組成,驅動器接收一路clock信號以及28路并行數據信號[6-8]。數據信號以7∶ 1形式分成4對數據流,加上clock信號流,一共有5對低電壓差分信號。接收端用于接收這5對信號。轉換原理如圖1所示。

圖1 CameraLink轉換原理圖 Fig.1 Block diagram of cameraLink conversion

CameraLink接口相機定義3種輸出信號:相機控制信號、相機配置串行通信信號和視頻傳輸信號。核心部分是視頻傳輸信號,其中包括了X0-~X0+、X1-~X1+、X2-~X2+、X3-~X3+、Xclk-~Xclk+這5對低壓差分信號;相機控制包括4對差分信號,即CCl-~CCl+、CC2-~CC2+、CC3-~CC3+、CC4-~CC4+;串行通信部分包括2對差分信號,即SerTC-~SerTC+和SerTFG-~SerTFG+。

CameraLink接口相機具有Base型、Medium型和Full型3種模式[9-10]。本系統是在Base模式下進行研究的,數據信號共有28位,其中包括A、B、C三個8位的數據端口,以及FVAL(幀有效)、LVAL(行有效)、DVAL(數據有效)、SPARE(空)4個視頻控制信號。

在整個過程中相機的驅動信號、全部的數據信號、以及控制信號都與經CameraLink轉換后的時鐘信號同步。

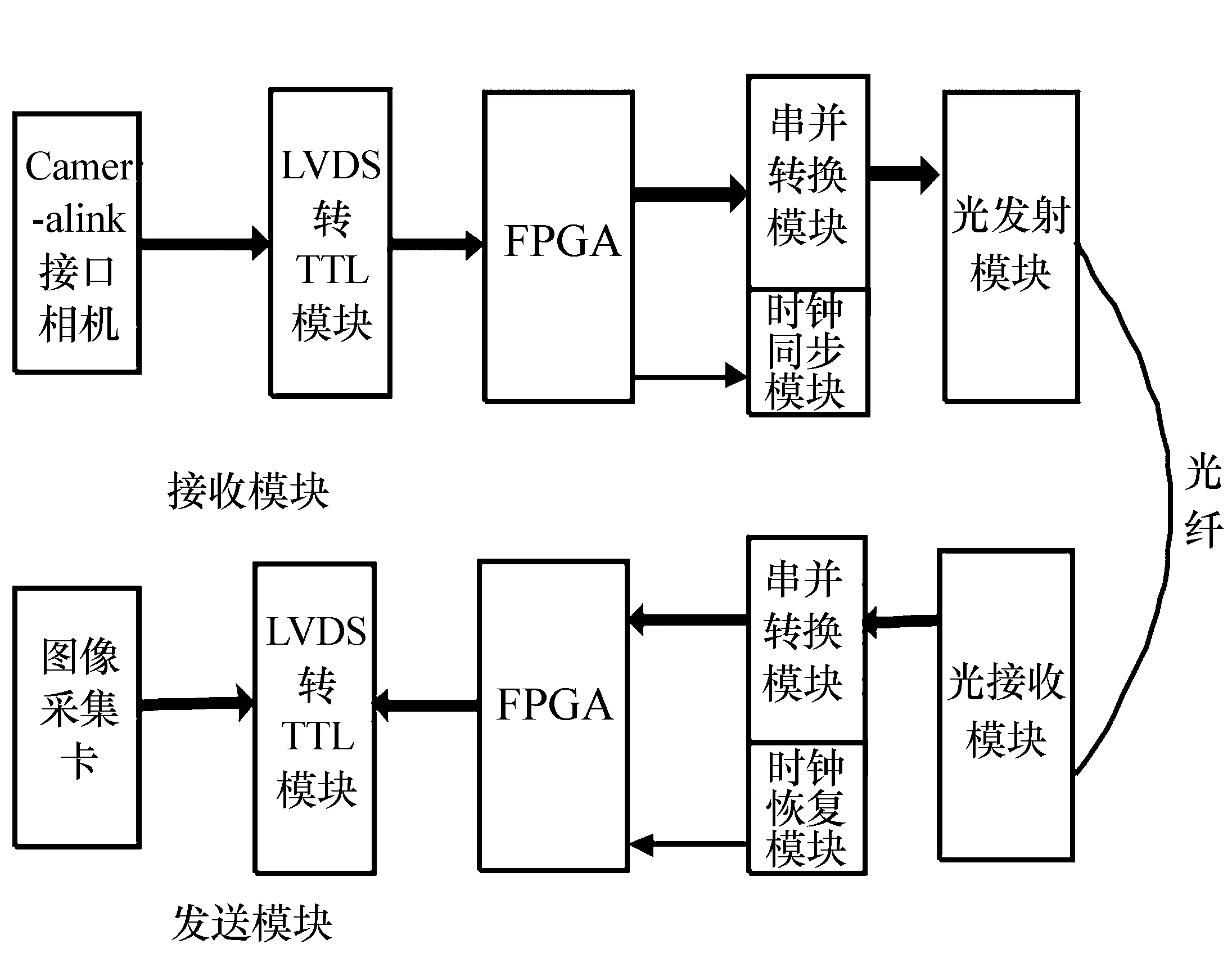

2.2 基于CameraLink接口的光纖傳輸系統

圖2為基于CameraLink接口的光纖傳輸系統[11]的結構框圖,整個系統的工作流程如下:首先由LVDS轉TTL模塊將相機輸出的LVDS信號轉換成TTL信號并直接送入FPGA[12],在相機同步信號的控制下,由FPGA完成對數據的采集以及預處理;然后,經串并轉換模塊處理后,為光發射模塊傳輸提供所有信號。光接收部分同理。整個系統主要由以下幾個單元模塊組成,即:CameraLink接口模塊、FPGA圖像采集和預處理模塊、串并轉換模塊、時鐘同步模塊、光電轉換模塊。

圖2 系統硬件結構框圖 Fig.2 Block diagram of system hardware

3 基于SerDes芯片組MAX9259/MAX9260具體方案設計

SerDes(Serializer/Deserializer)是目前主流的一種點對點(P2P),時分多路復用(TDM)的串行通信技術,即在發送端多路低速并行信號被轉換成高速串行信號,經過傳輸媒體(光纜或銅線)后,在接收端高速串行信號重新轉換成低速并行信號。

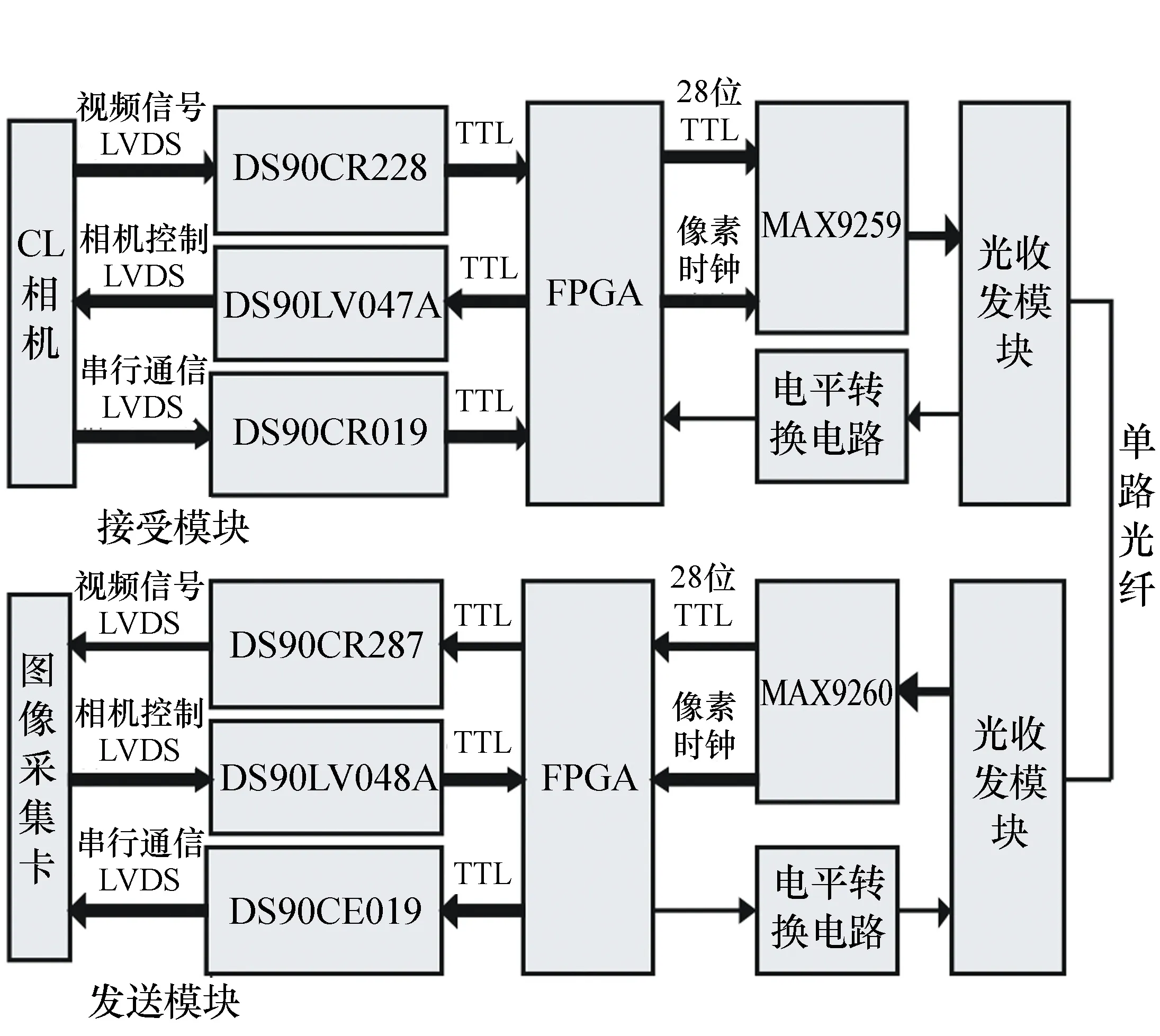

圖3為本文設計的光纖傳輸系統設計方案。具體工作過程如下:在接收模塊,像素時鐘作為同步時鐘,經DS90CR288解碼以及FPGA預處理后,直接把1路異步串行通信數據以及28位并行數據輸出到串并轉換收模塊。在發送模塊,像素時鐘及時恢復到同步狀態,同時又作為 FPGA 的系統時鐘,此時串并轉換發模塊從輸入的高速串行數據中提取幀信號后被FPGA送到DS90CR287中進行編碼。其中,電平轉換電路用于對FPGA與光收發模塊之間進行電平轉換,完成了相機與圖像采集卡兩者間的通信。

圖3 系統實現框圖 Fig.3 Specific system implementation block

3.1 串并轉換收發模塊

串并轉換模塊用于對信號進行串并轉換,使光模塊高速傳輸所有信號。目前,在Cameralink光纖傳輸領域,應用最廣泛的是基于TLK2711,DS90UR241的串并轉換模塊。鑒于TLK2711和DS90UR241分別只能提供16位和24位并行數據,給任務實現帶來了一定的難度,具體體現在以下兩個方面:數據時鐘的匹配性問題,即像素時鐘與光纖通信同步時鐘的匹配問題。它需要通過采用FIFO技術進行數據緩存調整;數據的位數問題,CameraLink接收模塊輸出的是30位并行TTL信號,這時候需要在核心芯片FPGA中采取分時復用/解復用的方法進行重組圖像信號[15]。雖然這些問題都可以通過相應辦法解決,但是它對系統硬件提出了更高的要求,同時加大了FPGA的開發難度。

針對串行/解串行芯片TLK2711[16]和DS90UR241傳輸方式存在的問題,本系統采用SerDes芯片組MAX9259/MAX9260[15]作為串并轉換模塊的核心芯片。該芯片組基于吉比特(千兆 )多媒體串行鏈路(GMSL)的原理,由串化器芯片MAX9259配合解串器MAX9260組成數字串行鏈,共同傳輸高速數據。其最大串行數據速率達到了2.5 Gb/s,同時具有兩種模式,即24/32位并行總線模式。其中32位模式下的最大總線時鐘達78 MHz;24位模式下的總線時鐘則可高104 MHz。

本系統的串行/解串行芯片設置為32位模式,當像素時鐘要求小于78 MHz,可直接完成29位數據(28位TTL并行數據和1路異步通信數據)的串行數據轉換。

在這一過程中,縱使相機像素時鐘發生了改變,串并轉換發模塊的時鐘也能實時改變,同時在整個傳輸過程中,光纖通信的同步時鐘以及FPGA的系統時鐘也都是由像素時鐘決定的,從而保證了整個系統圖像數據傳輸的同步性。

3.2 接口模塊

接口電路主要用于完成數字圖像信號的傳輸以及相機與采集卡之間的串行通信與控制等。以發送部分為例:系統采用應用較廣的DS90CR288作為CameraLink接收芯片,它的主要功能是將4路LVDS數據信號和一路LVDS時鐘信號轉換成TTL電平標準的圖像信號和時鐘信號,并輸入到FPGA中。

在控制信號的電平轉換電路設計上,根據CameraLink協議要求,采用DS90LV047芯片對相機的控制信號進行電平轉換,相機控制信號包括CC1、CC2、CC3、CC4。具體工作過程為:FPGA發出控制相機的命令(為TTL電平信號),經過DS90LV047將FPGA發出的TTL電平信號轉換為LVDS信號再傳給相機,從而實現對相機的控制。

在相機串行通信信號電平轉換電路設計上,選用具有差分發送和差分接收功能的DS90LV019芯片完成串行通信(其中包括2對差分信號SerTFG、SerTC),即通過將兩對LVDS差分信號與TTL信號之間的相互轉換,實現相機端和數據處理端的通信。

3.3 光模塊

光模塊[14]也稱為光收發一體模塊。它的組成部分包括光電子器件、功能電路和光接口等,光電子器件又由發射和接收兩部分構成。

發射部分的工作原理是:輸入的電信號經過驅動芯片后,由發光二極管或半導體激光發射相應的調制光信號。同時利用光功率控制電路自動穩定輸出光信號功率。接收部分的工作原理是:輸入的光信號經過光探測二極管后,轉換成相應的電信號,相應的電信號由前置放大器輸出。10G光模塊主要包括光/電轉換、時鐘提取和同步、復用/解復用、64B/66B編解碼、WIS、8B/10B編解碼等子功能模塊[17],有300pin、Xenpak、Xpak、X2和XFP等封裝形式。

本文采用的是收發一體、單模雙向的XFP封裝形式,來完成光電信號之間的轉換。采用波分復用技術實現兩種光信號共用一個信道,從而完成雙向通信功能。在發送端的發送單元光波長為1 310 nm,接收端的光發射單元光波長為1 550 nm,該光模塊結構小巧,價格相對廉價,使用方便靈活。

4 實驗結果分析

實驗首先采用模擬相機數據源[18]測試了系統設計的正確性,以及傳輸通路中存在的問題。采用Verilog HDL硬件描述語言進行時序設計,完成了分辨率為320 pixel×256 pixel,像素時鐘為40 MHZ,幀頻為100 Hz,像素深度為14位的相機模擬源,然后將程序下載到FPGA進行驗證。

當FVAL、LVAL、DVAL時為高電平時,才能輸出數據,每14 bit為一個數據,從0開始,每一行的各像素點數值相同,行與行之間數據值加64。采集卡采集到的漸變條圖像如圖4所示。從采集到的漸變條圖像中截取了有代表部分(圖4虛線框部分所示)的像素值,如圖5所示。像素值的變化符合模擬圖像源的設計要求,驗證了系統的正確性。

圖4 數據合成采集卡漸變條顯示圖 Fig.4 Gradient bar graph for data synthesis acquisition card

接著,實現了型號為MC1362(像素時鐘最高工作在80 MHz)的MIKROTRON可見相機的CameraLink數字圖像的光纖傳輸驗證實驗。相機工作模式設置為2×8 bit,相機的幀頻為100 Hz,分辨率為1 024 pixel×1 024 pixel,將相機輸出的Base接口連接到系統的圖像發送端,圖像采集卡采集到的數字圖像如圖6所示。

與其他同類技術相比較,整個系統的優勢在于:通過采用相機的像素時鐘,避免了多個時鐘域匹配帶來的麻煩。另外,由于SerDes芯片組MAX9259/MAX9260,其本身就提供了足夠位數的并行總線,因此FPGA不需要進行時分復用等工作,只需要執行簡單的數據分配即可。從而使其設計簡單,效率更高。

5 結 論

本文提出一種系統,其采用了一種新的串行/解串行技術,基于Base型CameraLink標準信號的遠距離傳輸,實現了數字圖像的光纖傳輸。本文設計的核心為利用SerDes芯片組MAX9259/MAX9260串行收發器代替光纖傳輸系統常用的串并轉換模塊(基于TLK2711和DS90UR241等)。該方法省去了數據通道的時分復用、異步FIFO數據緩存的繁瑣開發過程,大大簡化了設計的復雜度。實驗結果表明,圖像數據光纖傳輸系統工作性能穩定,傳輸圖像效果較好,傳輸帶寬達到2.5 Gb/s(相機時鐘要求小于78 MHz)。接下來將致力于如何提高傳輸信息正確性的研究,以及解決噪聲干擾等問題。