GNSS多頻通用射頻模塊設計與實現

, , ,

(1.桂林電子科技大學信息與通信學院, 廣西桂林 541004;2.桂林電子科技大學廣西精密導航技術與應用重點實驗室, 廣西桂林 541004)

0 引言

衛星導航技術普遍運用于民用與軍事領域,在各行業、各領域中具有舉足輕重的作用[1-3]。隨著各類衛星導航系統的依次出現,產生對多系統多頻點的通用射頻模塊的需求[4-8]。

為此,文中提出采用AD8347與SI4133為核心的多頻點射頻模塊的設計方案。該方案可以對現有多系統中的多個頻點信號進行下變頻;通過合理設計濾波器相關參數和接收機基帶跟蹤環路結構,實現單通道對L1,B1信號的同時處理、定位。文中主要闡述了通用射頻模塊的設計方案、微帶線電感等設計經驗,實現了多頻點通用射頻模塊,最終通過測試驗證結果。

1 系統總體框架

此次設計的射頻模塊從天線獲得射頻信號,通過變頻產生模擬中頻信號,并帶有獨立供電電路的射頻模塊[9-13]。

系統總體框圖如圖1所示。天線輸出的信號被第一級低噪放大器(Low Noise Amplifier,LNA)與第二級LNA放大后,經二等分功分器分別輸入兩個射頻通道。射頻通道采用本振搭配混頻器的方式實現。混頻器輸出波形濾波后經輸出接口輸出給后級電路。

2 射頻模塊硬件設計

2.1 低噪放電路設計

根據多級系統噪聲系數公式:

(1)

低噪放電路作為多級系統第一級電路應盡可能選擇高增益、低噪聲系數的器件[14-18]。由于單個放大器若具有過高的增益可能會增加放大器自激的概率,同時為了滿足高增益需求,因此采用級聯的方法,保證系統噪聲系數不受后級電路的影響。

低噪聲放大器選用飛利浦的BGA2001,它是一款可應用于低電壓情況的單片微波集成放大器,最大電源電壓為4.5 V;在1~1.6 GHz頻段內,即包含衛星導航信號的工作頻段內,增益高達20 dB,噪聲系數低至1.3 dB。圖2是設計的低噪放電路。

2.2 參考時鐘電路設計

參考時鐘的頻偏會引入額外的載波多普勒,使得初始搜索在錯誤的多普勒單元,延長搜索時間;同時還會導致下變頻時引起較大頻差,導致中心頻率兩邊帶內有用信號成分被濾波器濾除,引起載噪比的損失。因此必須保證參考時鐘穩定度[19-20]。

圖3為參考時鐘電路。參考時鐘電路采用0.5 PPM的溫補晶體振蕩器作為板載時鐘源。參考時鐘電路除板載時鐘外,預留了從系統外部輸入時鐘的MMCX接口作為備用時鐘源。參考時鐘電路通過圖3中電容C80與電容C90是否焊接作為時鐘源的選擇開關;當電容C80焊接、電容C90不焊接時,則時鐘源選擇板載時鐘;當電容C80不焊接、電容C90焊接時,則時鐘源選用外部時鐘。時鐘源時鐘輸入兩個AD8012放大器進行放大。其中一個運算放大器的輸出時鐘作為系統時鐘,另一個運算放大器的輸出時鐘通過MMCX接口被輸出到系統外部。

2.3 下變頻電路設計

下變頻電路通過SI4133得到本振時鐘;本振時鐘與前級輸入的衛星導航信號通過AD8347混頻器進行混頻。下變頻電路設計的關鍵是SI4133外部電感的計算與布線,AD8347混頻器混頻輸出后外部中頻濾波器電路設計。

2.3.1 外部電感設計

SI4133芯片擁有射頻鎖相環1(RF1)、射頻鎖相環2(RF2)、中頻鎖相環(IF)。芯片內部各鎖相環輸出頻率變化幅度是壓控振蕩器(Voltage Control Oscillator,VCO)中心頻率的±5%。VCO中心頻率由外部電感決定。設置輸出頻率與中心頻率的電感值誤差,可由芯片內部的自調諧算法來補償,但電感值的最大誤差不能超過 ±10%。當上電或輸出頻率被修改時,該算法即被使能[21-22]。

下變頻電路設計中只使用兩個射頻鎖相環,設置RF1鎖相環與RF2鎖相環的VCO中心頻率分別為1 580 MHz與1 220 MHz,則鎖相環可輸出頻率范圍分別為1 501~1 659 MHz,1 159~1 281 MHz。兩個鎖相環的輸出采用復用輸出管腳,所以最終本振頻率的輸出范圍就是這兩個頻率范圍的組合。

鎖相環VCO的外部電感的連接示意圖如圖4所示,每個鎖相環內部有一個封裝電容和封裝電感,為滿足固定頻率的頻率設置要求,需要接外部電感使得總電感數值滿足要求。

根據外部電感計算公式(2)可以推算出外部公式(3):

(2)

(3)

式中,fCENTER為VCO中心頻率,LPKG為內部封裝電感,CNOM為內部封裝電容。通過查找數據手冊獲得RF1的LPKG與CNOM分別為2.0 nH,4.3 pF;RF2的LPKG與CNOM分別為2.3 nH,4.3 pF。

通過式(3)可以計算獲得外部電感的數值。經計算獲得1 580 MHz與1 220 MHz中心頻率對應的外部電感分別為0.359 7 nH和1.245 5 nH。由于該電感的數值較小,需要采用如圖5所示的微帶線模型計算微帶線長度來替代管腳間的電感。表1為計算所得的微帶線各項參數。

表1 微帶線參數mm

2.3.2 AD8347外圍電路及中頻濾波器設計

AD8347是一種具有射頻和基帶信號自動增益控制功能的寬帶直接正交解調芯片,可用于多種類型的接收機;其工作帶寬為800 MHz~ 2.7 GHz,可覆蓋所有導航射頻信號;其輸入三階交調截為11.5 dBm。AD8347作為接收通道的最后一級電路,其三階截點在系統三階截點中起主要作用;較大的三階截點使得接收通道具有良好的動態范圍[23-26]。射頻通道1的AD8347外圍電路設計如圖6所示。

AD8347外圍電路設計較為簡單,只需要連接一些必要的無源器件。電源使能管腳(ENBL)接電源,使AD8347混頻器芯片一直處于使能狀態。SI4133輸出的本振時鐘信號為單端信號,使用偽差分電路將本振時鐘轉換為差分時鐘,輸入AD8347芯片的本證差分輸入管腳(LOIP,LOIN)。功分器輸出的射頻信號亦通過偽差分電路被轉換為差分信號輸入AD8347芯片的射頻信號差分輸入管腳(RFIP,RFIN)。AD8347芯片的射頻部分放大通過增益控制管腳(VGAIN)控制放大倍數,其管腳電壓與放大倍數成負相關。為了獲得更適合的射頻信號,圖6中將增益控制管腳與自動增益輸出管腳(VAGC)相連接,由芯片根據輸入的射頻信號強度產生控制電壓從自動增益輸出管腳輸出,進而控制射頻放大倍數。

射頻通道1與射頻通道2具有相同的拓撲結構,不同之處在于AD8347外圍的中頻濾波器設計參數不同。射頻通道1的中頻低通濾波器用于對小帶寬衛星導航信號進行濾波,例如GPS L1、北斗B1,以及實現GPS L1與北斗B1信號單通道同時接收。由于GPS L1的有用信號范圍為1 574.397~1 576.443 MHz,北斗B1的有用信號范圍為1 559.052 ~1 563.144 MHz,故其有用信號的最大頻率差為17.391 MHz。當低通濾波器截止頻率大于8.695 5 MHz,并且本振頻率設置為GPS L1有用信號頻率最大值與北斗有用信號頻率最小值的中點時,則經過低通濾波器后的中頻信號包含了GPS L1與北斗B1的有用信號。射頻通道2的中頻低通濾波器用于對較大帶寬的衛星導航信號進行濾波,例如北斗B3、GLONASS L1。根據分析,射頻通道1采用截止頻率為10 MHz的5階橢圓低通濾波器,射頻通道2采用截止頻率為22 MHz的5階橢圓低通濾波器。中頻低通濾波器的設計采用歸一化濾波器設計方法,然后使用計算機輔助設計驗證,最后根據實際器件參數進行調整[28-30]。圖7展示了實際參數情況下的低通濾波器電路。

將接收機通道按最大增益100 dB設計,經前級低噪聲放大器40 dB放大以及功分插損-3 dB后, 射頻通道需要最大63 dB最大增益。根據芯片手冊的介紹,AD8347芯片最大增益為69.5 dB,因此接收通道留有6.5 dB增益裕量;該裕量可用于補償濾波器插損以及通道失配造成的增益損失。

2.4 射頻電源設計

射頻模塊采用5 V 外部供電,其主要供電需求為3.3 V和5 V,可分為控制部分和下變頻變頻部分。控制部分僅僅是STC15W408S控制器的電源,采用通用的LM1117-3.3穩壓到3.3 V。下變頻變頻部分電源涉及到低噪聲放大器、鎖相環、混頻器等噪聲敏感器件的供電,需要選擇高文波抑制比的低壓差穩壓器[31]。MIC5245系列與MIC5205系列專為射頻器件穩壓而設計,采用該兩個系列作為射頻部分的穩壓器件。圖8展示了系統部分電源網絡。

2.5 PCB設計

在PCB設計時,需要使用接地器件實現“0”參考點。用于射頻接地的器件有3種,分別是“0”電容、微帶線和射頻電纜。射頻模塊采用“0”電容接地;通過“0”電容與“無窮大”電感相互配合,盡可能降低電路干擾[32]。

由于系統處理的是射頻信號,故需要注意布線時的阻抗問題,本設計采用T-G-G-B(頂層-地-地-底層)的層疊結構,通過調整線寬及層間距達到阻抗匹配。對于高速信號走線,由于趨膚效應造成走線周圍具有電磁場,容易造成相鄰線材的耦合干擾。為使走線間耦合干擾達到可以忽略,布線時需要滿足3W原則(走線中心間隔滿足3倍線寬)。

3 射頻模塊的驅動軟件設計

本振芯片SI4133選用STC15W408S控制器進行控制。STC15W408S具有內部RC振蕩器與復位電路,只需要正常供電就能讀取程序代碼,正常工作。

3.1 驅動軟件總體流程

驅動軟件總體控制流程如圖9所示,首先進行控制器內相關外設的初始化,然后對射頻通道1上本振芯片進行配置。直等到確認射頻通道1的本振頻率鎖定后,則對射頻通道2上本振芯片進行配置。當射頻通道2上的本振頻率鎖定后,控制器進入休眠狀態。假如有外部中斷將控制器喚醒,則根據如圖9所示流程再次依次配置射頻通道1與射頻通道2上的本振頻率。

3.2 三線串行接口時序

SI4133芯片可以通過三線串行總線配置各分頻系數。三線串行總線的時鐘不能大于25 MHz,因此控制器通過通用IO模擬三線串行總線,設置三線串行總線的時鐘為80 kHz,非工作狀態電平為高電平,時鐘線在上升邊沿進行采樣。SI4133芯片每次被選中,可以配置一個配置寄存器;其可配置空間為9個寄存器。三線串行總線發送的數據結構如圖10所示,發送數據為22 bit,由18 bit數據域與4 bit地址域組成,地址域存放配置數據,地址域存放配置空間的地址。發送配置信息時,數據采用大端模式發送。

3.3 本振參數數值設置分析

SI4133輸出的本振頻率由式(4)確定:

(4)

式中,N為VCO分頻系數,R為參考時鐘分頻系數。然而,鎖相環的可以輸出頻率已經由VCO的中心頻率限制,因此在設置的分頻系數R,N必須使得鎖相環輸出頻率限定在2.3.1節中所述的頻率范圍內,即本振的頻率范圍為1 501~ 1 659 MHz,以及1 159~1 281 MHz。

SI4133芯片內每個鎖相環都有各自的鑒相器增益Kp、分頻系數N、分配系數R。不同的相位鑒別器增益Kp的設置,會導致分頻系數R與分頻系數N有不同的取值限制范圍。表2展示了不同相位鑒別器增益設置對應的系數N的取值范圍。表3展示了不同相位鑒別器增益設置對應的系數R的取值范圍[33]。

表2 鑒別器增益系數對應系數N的取值

表3 鑒別器增益系數對應的系數R的取值

根據表2與表3,當驅動程序將所有射頻鎖相環參數R設置為10時,可以保證由所有衛星導航射頻信號的頻率計算所得的分頻系數N的取值小于2 048,因此可以使用默認的Kp1,Kp2數值(默認數值為0)而不需要再次配置,此刻,本振頻率可以按照1 MHz的步長進行設置。

3.4 本振頻率輸出流程

設置射頻通道的本振頻率前,先設置多功能管腳為鎖相環鎖定檢測管腳,將鑒相器增益還原為默認值;由于未使用到芯片內 IF鎖相環,則關閉IF鎖相環電源;開啟RF鎖相環電源。

接著判斷設置的輸出頻率的范圍。當設置的頻率范圍落在RF1鎖相環的可輸出范圍內,則設置RF1鎖相環參考時鐘分頻系數R為10,然后根據式(4)計算獲得RF1鎖相環的VCO分頻系數N,最后通過設置RF1鎖相環輸出連接到芯片RF輸出管腳,將設置的本振時鐘輸出。當設置的頻率范圍落在RF2鎖相環的可輸出范圍內,則設置RF2鎖相環參考時鐘分頻系數R為10,然后根據式(4)計算獲得RF2鎖相環的VCO分頻系數N,最后通過設置RF2鎖相環輸出連接到芯片RF輸出管腳,將設置的本振時鐘輸出。本振芯片的設置流程如圖11所示。

4 功能測試與結果分析

4.1 模塊功能測試

功能測試的目的是確保模塊的設置數值與預期數值相符,確保各個芯片能夠正常工作,實現基本功能。表4展示了電源電壓測試結果。測試得到的電壓與實際電壓差值保證在0.3%以內,系統可以被正常供電。

表4 各電源網絡電源電壓測試 V

4.2 三線串行接口時序邏輯測試

本測試使用夢源科技公司的邏輯測試儀器測試信號的電平邏輯。圖12~圖15中,0號線為三線串行接口的時鐘SCLK,1號線為三線串行接口的數據線SDATA,2號線為射頻通道2的片選信號,3號線為射頻通道1的片選。

從圖12中可知,此時SCLK的高電平持續時間為500 ns,時鐘周期為12.4 μs,時鐘頻率為80.65 kHz,符合三線串行接口的時序要求。

圖13展示了一個字段的配置過程,該圖設置射頻通道1本振芯片的寄存器0,設置的數值為0x03000,即設置輔助管腳的功能是作為鎖相環鎖定探測引腳。

圖14與圖15分別是射頻通道1本振與射頻通道2本振的設置過程,只需要設置5個寄存器數值即可完成一個本振的設置。其中圖14設置本振頻率為1 568 MHz,圖15設置本振頻率為1 259 MHz。

4.3 下變頻測試

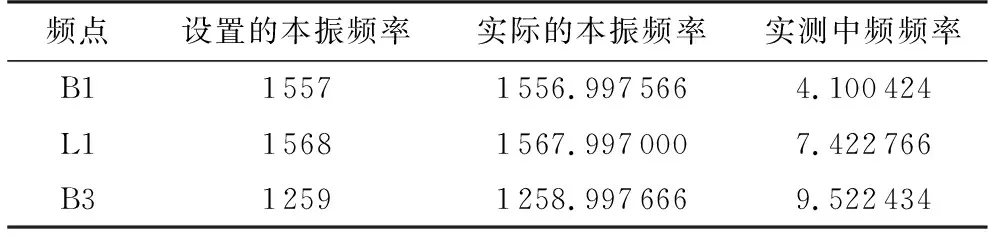

下變頻測試采用安捷倫E4438C矢量信號發生器產生相關導航頻點的信號,使用頻譜儀對模塊輸出進行頻率測試。圖16展示的是模塊設置本振頻率為1 568 MHz的情況。圖17是利用圖16的本振頻率,利用矢量信號發生器產生頻率為1 575.42 MHz的信號下變頻之后的結果。表5展示了相關頻點下變頻測試的結果,表明模塊的下變頻結果的誤差符合衛星導航信號定位應用的要求。

表5 相關頻點下變頻測試結果MHz

4.4 定位應用測試

在射頻模塊下變頻測試后,對其進行定位應用測試。射頻模塊輸入端接樓頂天線,模擬中頻輸出接接收機數字基帶處理板,將定位結果與天線位置進行比較,并確定誤差。圖18~圖20為B1頻點單點定位在3個維度上的誤差;表6是其他相關頻點的測試結果。

表6 定位應用測試結果

將射頻模塊與導航信號基帶處理板連接后,作為RTK接收機進行差分定位測試,圖21為某次模塊應用于RTK接收機的差分結果,表明了該模塊可以應用于厘米級的應用,誤差在6 cm以下。

5 結束語

本文提出了一種可應用于衛星導航接收機的多頻點通用射頻模塊的設計,利用AD8347與SI4133芯片,搭建了射頻模塊電路。經過多次試驗,該多頻點通用射頻前端模塊與實驗室現有數字基帶板搭配,能供應準確的定位服務,達到預期的功能;并可以實現單個射頻通道對L1,B1頻點的同時定位處理,應用于RTK接收機可以實現厘米級定位。