10~15 GHz寬帶捷變源設計

劉瑜現,薄淑華,任 程

(航天科工集團303所,北京 100074)

0 引言

頻率合成器是產生1個或多個穩定頻率的信號源。頻率合成技術于20世紀30年代提出,它作為現代無線通信系統、雷達系統、電子對抗和精密測量儀器等領域的核心器件,發揮著十分重要的作用[1]。頻率合成技術在國外發展較早。目前,國外的頻率合成技術發展的比較成熟,在頻率合成器的產品種類和技術指標上比國內技術好得多,相比之下,我國對頻率合成技術的研究比較晚,技術較為落后。超寬帶、快速鎖定、低相位噪聲、低雜散、小型化、全集成的頻率合成器的設計始終是對現代電子系統的一個挑戰[2]。

本文將通過研究鎖相環原理,尋找提高鎖相環頻率源頻率捷變時間的方法[3],設計一種輸出頻率在10~15 GHz的頻帶捷變頻的鎖相頻率源。其主要方法是直接數字頻率合成器(DDS)產生參考信號,固定相頻比,利用DDS參考信號的跳頻實現整個捷變源的跳頻,由于DDS的快速跳頻,捷變源的跳頻時間主要取決于鎖相環的鎖定時間,因此減小鎖相環路的頻率鎖定時間是重點研究內容。

1 提高鎖相環鎖定時間方法

鎖相環由鑒相器、環路濾波器和壓控振蕩器組成。鑒相器是相位比較裝置,用來比較輸入信號ui(t)與壓控振蕩器輸出信號uo(t)的相位,它的輸出電壓ud(t)是對應這2個信號相位差的函數;環路濾波器的作用是濾除ud(t)中的高頻分量及噪聲,以保證環路所要求的性能;壓控振蕩器指輸出頻率與輸入控制電壓有對應關系的振蕩電路,頻率是輸入信號電壓的函數的振蕩器VCO,壓控振蕩器受環路濾波器輸出電壓uc(t)的控制,使振蕩頻率向輸入信號的頻率靠攏,直至二者的頻率相同,使得VCO輸出信號的相位和輸入信號的相位保持某種特定的關系,達到相位鎖定的目的[4]。

以采用二階環路濾波器的三階鎖相環為例,其頻率鎖定的時間為:

(1)

式中,ωn為環路自然諧振角諧振頻率;ξ為阻尼因子;Δftol為最終鎖定頻差;f1為初始頻率;f2為進入鎖定帶頻率。

由式(1)可知,頻率鎖定的時間與環路帶寬、起始頻率差有關系。鎖相環路的帶寬直接決定了鎖定時間:環路帶寬越大,鎖定時間越短;環路帶寬越小,鎖定時間越長[5]。頻率跳變的大小也決定環路的鎖定時間:頻率跳變越大,鎖定時間越長;頻率跳變越小,鎖定時間越短。

減小鎖相環鎖定時間的主要方法有:

① 增加環路的帶寬,可以減小頻率鎖定時間。但是增加環路帶寬,減小雜散信號的衰減,增加相位噪聲,當環路帶寬增加到1/5的鑒相頻率時,環路可能變得不穩定,環路失鎖。

② 增加鑒相頻率,鑒相頻率決定了反饋信號和參考信號的比較速度,增加電荷泵的鑒相頻率,加速電荷泵向環路濾波器的充放電,有效降低鎖定時間。

③ 減小跳頻的頻率,跳頻越小,環路頻率鎖定的時間越短,如果頻率跳變在鎖相環路的快捕帶內,頻率鎖定的時間將會很短[6]。

預置電壓法是減小頻率跳變的起始頻率差以達到快速捕獲的目的。跳頻的大小由系統決定,不能改變,但前饋補償方法可以用來降低初始頻率差,從而加快鎖定速度,這就是預置電壓法。

預置電壓法有2種[7]:人工電調法和自動掃描法。人工電調法是直接向壓控振蕩器提供一個控制電壓,改變壓控振蕩器的頻率,從而減小起始頻差,當起始頻差減小到直接進入快捕帶時,在環路本身的牽引作用下鎖定頻率;自動掃描法是當環路尚未鎖定時,給壓控振蕩器加—個周期性掃描電壓.使它的頻率在足夠寬的范圍內擺動。當頻率掃到環路快捕帶時,環路通過自身捕獲進入鎖定,此時加在壓控振蕩器控制端的掃描電壓自動去掉[8]。

通過在頻率鎖定的頻點[9],對壓控振蕩器的電壓進行測量;通過數模轉換,將對應的頻點的電壓值存儲到單片機,當頻率開始跳變時,根據目標頻點將此頻點對應的電壓讀出;通過數模轉換,經過加法器與原來環路中環路濾波器輸出的模擬控制電壓相加得到下一個頻率所需的控制電壓值,然后將此電壓輸入到壓控振蕩器的控制端,使壓控振蕩器的頻率發生改變,接近要跳變的頻點值,將環路直接拉入快捕帶,實現頻率的快速跳變[10]。電壓預置方法的難度在于數模轉換電壓的精確度,并且提供的電壓信號具有較高的純度,紋波信號對環路的鎖定有影響。精確的電壓對數模轉換要求較高,電路更加復雜[11]。

2 總體設計

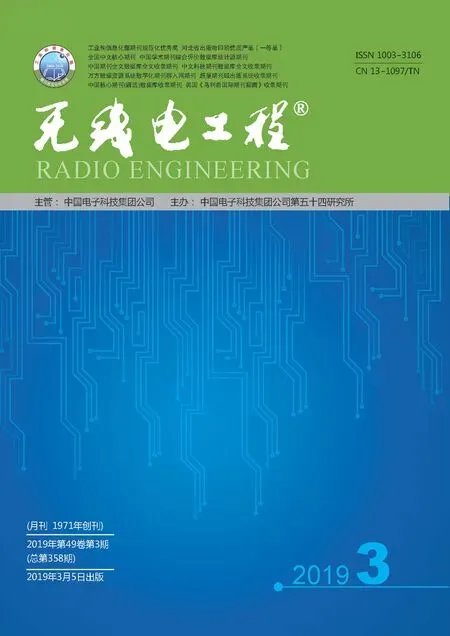

頻率合成的方法有多種[12-13],但各有優缺點,通過取長補短使頻率合成器達到理想的技術指標。通過對PLL和DDS的研究,采用DDS直接激勵PLL,即用DDS的輸出作為PLL的參考輸入,來解決頻率分辨率和相位噪聲的矛盾[14],其原理框圖如圖1所示。當DDS的輸出作為PLL的輸入參考信號時,射頻信號分頻比固定不變,頻率的步進由DDS改變實現,PLL相當于帶有跟蹤濾波功能的倍頻器,PLL將有效抑制DDS的輸出雜散,提高信號輸出頻譜質量[15],而且參考頻率較高,可以通過增加PLL的環路帶寬提高跳頻時間[16]。

圖1 寬帶捷變源原理

DDS激勵PLL的頻率合成方式中,由于DDS的響應時間在ns級,因此頻率跳變的時間主要取決于PLL的時間,PLL的頻率跳變時間在μs級,甚至ms級。為了縮短PLL的頻率響應時間,在DDS激勵PLL的基礎上,增加壓控振蕩器的電壓預置快鎖技術,將鎖相環的起始頻差迅速拉入鑒頻鑒相器的鎖定帶內,減小環路鎖定時間,以實現頻率的快速跳變。當小步進時調整DDS的輸出改變鎖相環路的頻率輸出,當頻率跳變步進大時,控制部分直接提供給壓控振蕩器一個控制電壓,將其拉入快鎖帶進行頻率鎖定,減小鎖定時間。

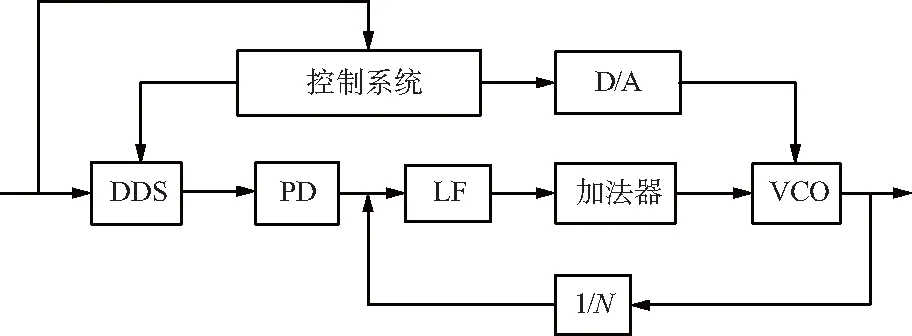

本文采用100 MHz晶振作為參考頻率,分別提供給控制系統和DDS,由于VCO的輸出頻率為10~15 GHz,經過8分頻后,輸出頻率為1.25~1.875 MHz,再經過鑒頻鑒相器內部集成的分頻器進行20分頻,最終以62.5~93.75 MHz的頻率進行鑒相比較,即DDS的輸入到鑒相器的頻率為62.5~93.75 MHz,經過環路濾波器后輸出控制電壓提供給VCO,當頻率進行跳變時,由控制系統控制D/A變換器給出預置電壓輸出,同時改變DDS的輸出頻率,D/A控制器輸出的預置電壓通過加法器與鎖相環路中環路濾波器的輸出電壓相加后輸出給VCO,實現VCO輸出頻率的跳變,VCO輸出頻率經過分頻反饋回路與DDS的輸出頻率進行鑒相比較,實現目標頻率的再次鎖定,如圖2所示。

圖2 方案原理

3 電路參數設計及仿真結果

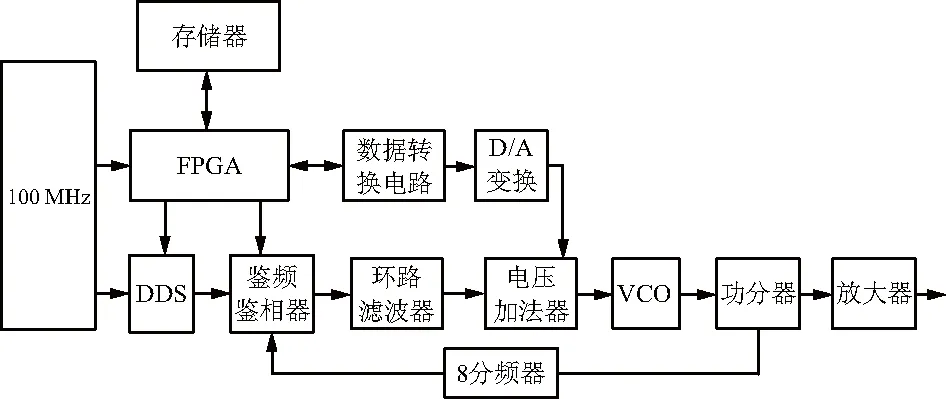

環路帶寬作為PLL的重要參數,通過設置環路濾波器的電阻電容值來改變環路的帶寬和相位裕度參數。本文采用的是三階低通濾波器,如圖3所示。

圖3 三階低通濾波器

環路已確定參數設置如下:環路帶寬(Closed-loop Bandwidth)為2 MHz;鑒相器輸出峰值(Vp)為5 V;射頻輸出頻率為10 000 MHz;鑒相頻率為62.5 MHz;分頻比(N)為160;相位裕度為60。

計算環路濾波器未知參數。經計算,Cc,C2,R2的值分別為232 pF,941 pF,316 Ω。

經過ADS仿真可知,環路的低通濾波器的環路帶寬為2 MHz,相位裕度為54。

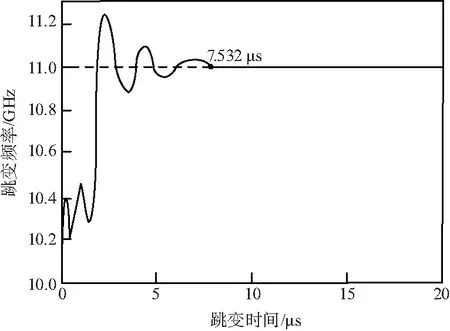

對未加電壓預置時的頻率鎖定時間進行仿真分析。用ADS仿真,環路帶寬為2 MHz,分別設定不同的跳變頻率。鎖相環最終鎖定頻率由10 GHz跳變到11 GHz時需要時間如圖4所示。

圖4 跳變頻率與時間關系仿真結果

經過仿真,頻率由10 GHz跳變到11 GHz的時間是7.532 μs,由10 GHz跳變到15 GHz的時間是11.96 μs,由仿真結果可知,當鎖相環路的帶寬固定時,鎖定頻率的范圍越大,環路鎖定需要的時間也就越長。

用ADS仿真,環路帶寬為2 MHz,增加電壓預置,以研究加入電壓預置后對頻率鎖定時間的影響,如表1所示。

表1 電壓預置對頻率跳變時間影響

鎖定頻率/GHz未加電壓預置頻率鎖定時間/μs加電壓預置頻率鎖定時間 /μs117.5326.4701511.966.636

由表1可知,加入電壓預置后頻率鎖定時間將減小,且鎖定頻率跳變帶寬越大頻率鎖定時間減小的效果越明顯。

經過仿真分析,頻率在10~15 GHz進行跳變,可以實現跳變時間為10 μs以內。

4 試驗結果

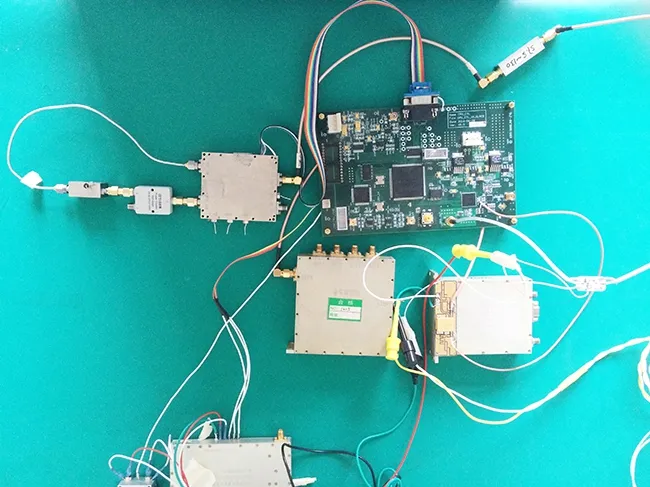

樣機實物圖如圖5所示。相位噪聲和輸出功率測試結果如表2所示。

圖5 樣機實物

表2 相位噪聲測試結果

頻率/GHz相位噪聲/(dBc/Hz@10 kHz)輸出功率/dBm10-904.511-876.812-885.513-884.514-904.415-954.9

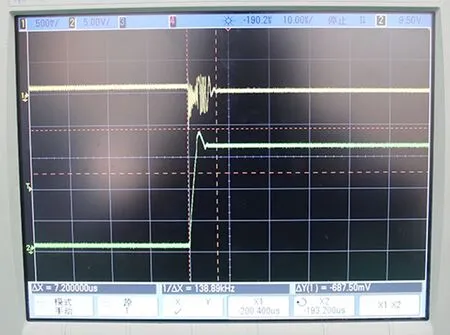

加電壓預置后,通過示波器進行頻率捷變時間的測試測試結果如圖6所示,測量的頻率捷變時間為7.2 μs。

圖6 頻率捷變時間測試結果

5 結束語

鎖相環應用范圍廣泛,但是由于響應時間較慢,限制了它的應用。頻率跳變起始頻差影響鎖相頻率源頻率跳變時間,通過電壓預置的方法減小頻率跳變時的起始頻率差,可以有效提高頻率鎖定的時間,并且通過選用具較高鑒相頻率的鑒相器,提高環路帶寬,最終可以實現在5 GHz的寬帶下,頻率跳變時間在10 μs內的技術指標。