基于Zynq的皮下指紋OCT數(shù)據(jù)采集系統(tǒng)設(shè)計

(浙江工業(yè)大學(xué) 信息工程學(xué)院,浙江 杭州 310023)

光學(xué)相干斷層掃描技術(shù)(Optical coherence tomography,OCT)由美國麻省理工學(xué)院的研究小組于1991年首次提出,OCT是基于低相干干涉原理,通過測量從樣品反射回來的后向散射光的強度對樣品進(jìn)行斷層成像的技術(shù)[1]。OCT技術(shù)具有非侵入、高分辨和活體檢測等優(yōu)勢,能夠?qū)ι锝M織在毫米深度范圍內(nèi)提供微米級分辨率的圖像,在生物組織活體檢測和成像方面具有廣泛前景[2]。傳統(tǒng)指紋識別會遭遇指紋破損、手指潮濕和人工指膜偽造等問題[3-4]。人體皮膚由表皮、真皮和皮下組織3 部分構(gòu)成,并含有附屬器官(汗腺、皮脂腺等)以及血管、淋巴管、神經(jīng)和肌肉等[5]。手指表皮層與真皮層間的分界處叫做乳頭層,表皮指紋來源于乳頭層,因此可以用乳頭層結(jié)構(gòu)來替代表皮指紋,且真皮層指紋不會因為手指表面皮膚的破損而損壞[6-7]。同時通過OCT采集到的指部生物信息還包括皮下汗腺信息,能更好地進(jìn)行生物識別和區(qū)分虛假指紋。在二十多年的發(fā)展過程中,OCT信號的探測方式從時域OCT(Time domain OCT, TD-OCT)成像過渡到了頻域OCT(Fourier domain OCT, FD-OCT)快速成像的階段[8-10]。頻域OCT的原理基于邁克爾遜干涉儀,通過參考臂和樣品臂反光鏡的反射回來的光會在耦合器相遇,并發(fā)生疊加和干涉,干涉的信號會被感光元器件接收,之后進(jìn)行快速傅里葉變換后,就能夠得到所測樣品的深度信息[11-12]。

OCT系統(tǒng)中一般會使用CCD(Charge coupled devices)作為感光元器件接受干涉光譜信號[13]。但使用CCD作為感光元器件,需要對CCD提供外部驅(qū)動,一般使用FPGA(Field programmable gate array)驅(qū)動。FPGA是可編程邏輯器件,針對CCD圖像傳感器不同的應(yīng)用場景,可以修改FPGA的內(nèi)部邏輯完成環(huán)境適配,具有很高的靈活性,與一般DSP(Digital signal process)處理器相比,F(xiàn)PGA具有更強的復(fù)雜時序輸出能力[14]。筆者 提出的系統(tǒng)是在頻域OCT的基礎(chǔ)上,使用Xilinx公司的Zynq芯片來進(jìn)行信號采集、傳輸及預(yù)處理。芯片由PS(Process system)與PL (Programmable logic)兩部分組成,PS部分以ARM Cortex-A9處理器為核心,內(nèi)部集成DDR存儲器控制器和大量的I/O口外設(shè)[15]。PL層具有FPGA的功能,是在Xilinx 7系列的FPGA基礎(chǔ)上嵌入了Block-RAM、DSP Slice和MMCM等功能單元[16]。利用FPGA的高并行性,可以進(jìn)行高速的數(shù)據(jù)采集及數(shù)據(jù)處理[17]。本系統(tǒng)通過在PL部分進(jìn)行硬件驅(qū)動、數(shù)據(jù)緩存以及預(yù)處理算法的設(shè)計,完成皮下指紋信息數(shù)據(jù)的獲取和預(yù)處理,在PS部分完成數(shù)據(jù)與PL端間交互和運行移植的Linux操作系統(tǒng),最終將處理后的數(shù)據(jù)通過千兆網(wǎng)口傳輸給上位機進(jìn)行顯示。

1 系統(tǒng)總體架構(gòu)

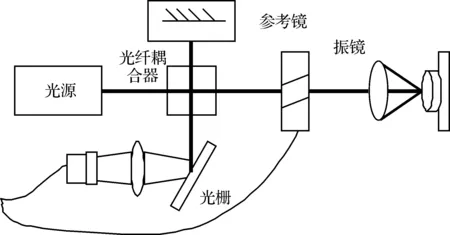

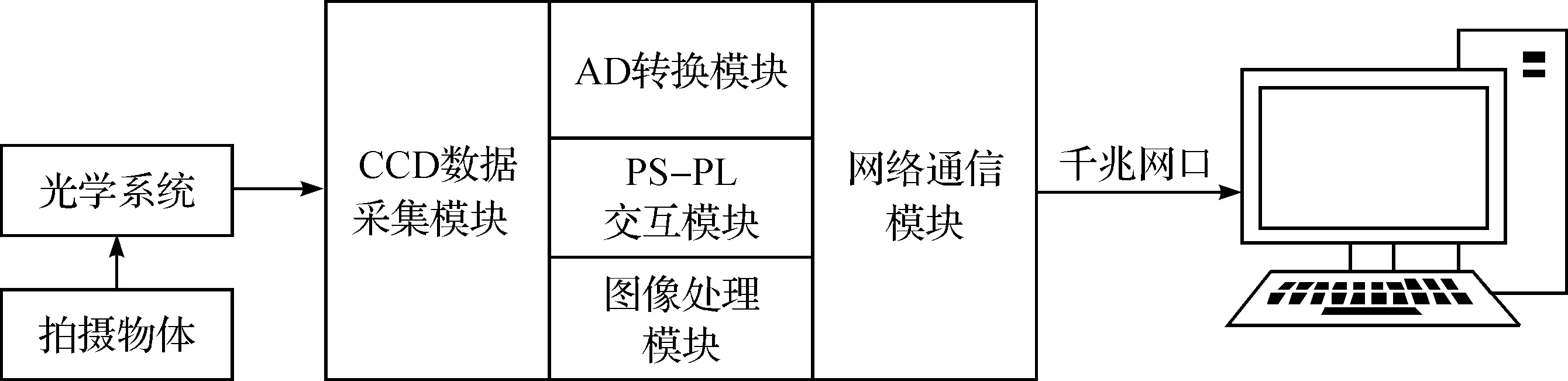

OCT數(shù)據(jù)采集系統(tǒng)由一個自主設(shè)計的線陣CCD相機、光學(xué)設(shè)備以及PC機3 部分組成。系統(tǒng)的結(jié)構(gòu)圖如圖1所示,功能框圖如圖2所示,光源發(fā)出的光經(jīng)過耦合器分光后,以50︰50的比例均勻分成兩束光分別射入?yún)⒖急酆蜆悠繁邸1粎⒖急壑衅矫骁R反射回來的光,與樣品臂中通過掃描振鏡系統(tǒng)對樣品進(jìn)行掃描后反射的光在光纖耦合器中發(fā)生疊加和干涉,包含樣品深度信息的干涉信號經(jīng)過光譜儀解調(diào),被線陣CCD采集。線陣CCD可以將接收到的像,也就是光信號,轉(zhuǎn)換為模擬電信號后通過放大器輸出[18]。模數(shù)轉(zhuǎn)換模塊(Analog digital converter, ADC)將經(jīng)過放大的模擬電信號按照一定的頻率進(jìn)行采集和轉(zhuǎn)換,輸出一系列離散的數(shù)字電信號。Zynq芯片負(fù)責(zé)給線陣CCD和ADC提供相應(yīng)的時序驅(qū)動,保證上述兩個模塊的正常運行。PS-PL模塊和數(shù)據(jù)預(yù)處理模塊負(fù)責(zé)對經(jīng)AD采集后的數(shù)據(jù)的存儲、傳輸及圖像預(yù)處理。經(jīng)過處理的數(shù)據(jù)通過千兆網(wǎng)口,上傳給上位機進(jìn)行顯示。

圖1 基于光譜儀的頻域OCT結(jié)構(gòu)圖Fig.1 Structure of the frequency domain OCT spectral-based

圖2 OCT數(shù)據(jù)采集系統(tǒng)功能框圖Fig.2 The functional block diagram of the system

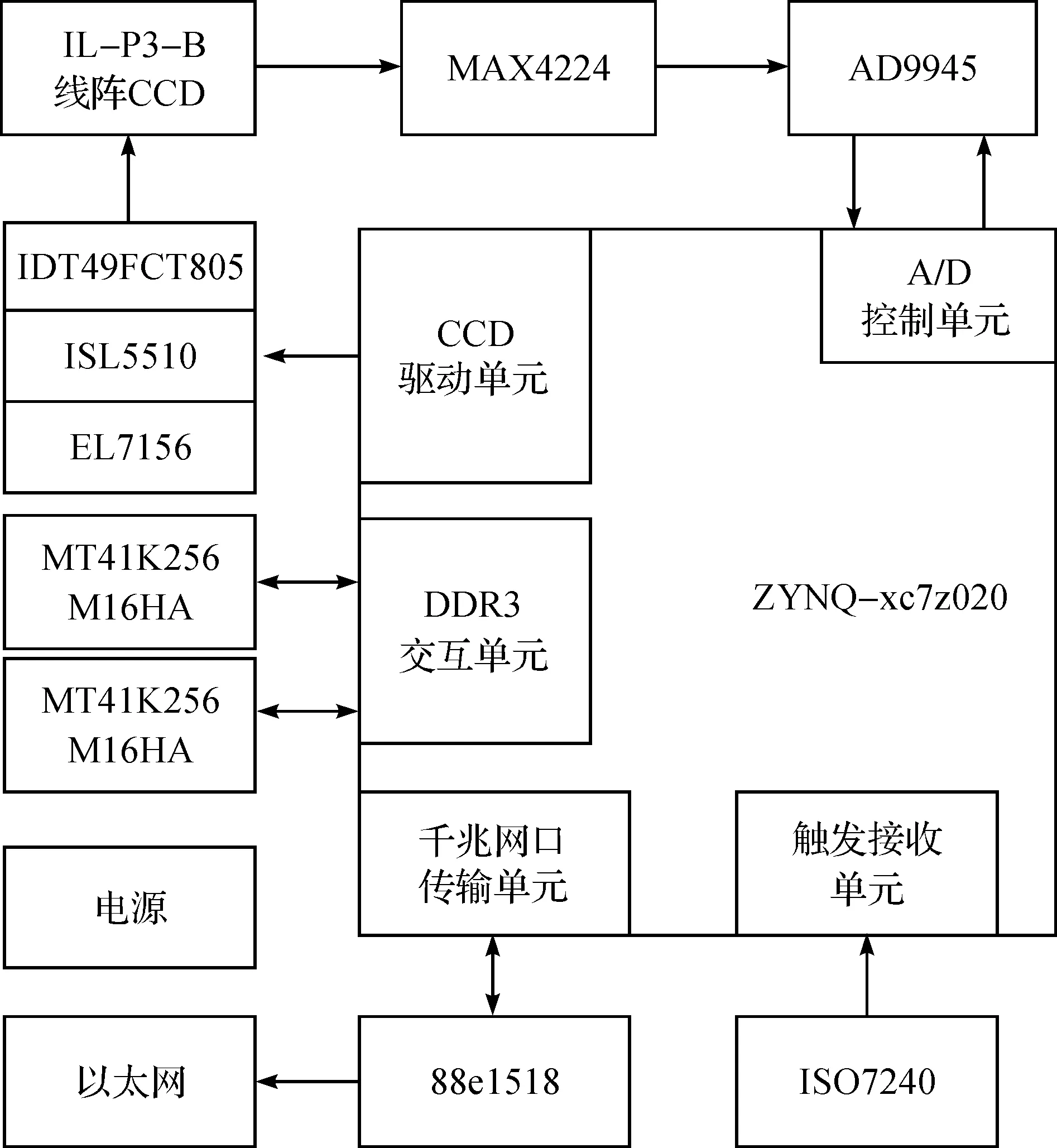

系統(tǒng)硬件架構(gòu)如圖3所示,系統(tǒng)主要由線陣CCD傳感器模塊、放大模塊、A/D轉(zhuǎn)換模塊、Zynq處理器控制模塊、DDR3數(shù)據(jù)緩存模塊、千兆網(wǎng)口模塊、同步觸發(fā)模塊以及電源模塊組成。本系統(tǒng)中,處理器控制芯片是Xilinx公司Zynq系列下的XC7Z020,芯片內(nèi)部具有豐富的邏輯資源。CCD傳感器模塊采用IDT49FCT805,ISL5510,EL7156型芯片作為CCD驅(qū)動電路,驅(qū)動Teledyne DALSA公司的IL-P3-B型線陣CCD采集圖像。A/D轉(zhuǎn)換模塊采用的是ADI公司的一款具用40 MSPS處理速度,12 bits精度以及CDS相關(guān)雙采樣功能的前端模擬采集芯片AD9945。放大模塊采用MAX4224電流反饋型運放,具有超高速性能、低失真及低功耗的優(yōu)點,特別在視頻應(yīng)用中有突出表現(xiàn)。DDR3數(shù)據(jù)緩存模塊使用兩片MT41K256M16HA型號DDR3,存儲容量為8 Gb。千兆網(wǎng)口模塊選用Marvell公司的一款能夠自適應(yīng)10 MB/100 MB/1 000 MB工作方式的PHY芯片88e1518型號,與Zynq處理器控制模塊連接,將數(shù)據(jù)從DDR3數(shù)據(jù)緩存模塊通過千兆網(wǎng)口模塊搬至與PC機。同步觸發(fā)模塊使用了具有多通道的隔離輸入與輸出功能的ISO7240C型號芯片。電源模塊采用直流12 V輸入,通過DC/DC產(chǎn)生5,3.3 V電壓,再由電源芯片產(chǎn)生各模塊需要的12.5,14,2,1.2,1,1.8,-5,-2 V電壓。

圖3 系統(tǒng)硬件架構(gòu)Fig.3 Structure of the system hardware

2 系統(tǒng)硬件驅(qū)動模塊設(shè)計

2.1 CCD模塊驅(qū)動設(shè)計

本系統(tǒng)采用IL-P3-2048B作為感光元器件,它是一款高靈敏度、高信噪比以及光積分時間可調(diào)的線陣CCD器件。IL-P3-2048B的像元尺寸為14 μm×14 μm,它的像元輸出頻率最高能達(dá)到40 MHz,在有效像素為2 048 個像素的情況下其最高掃描行頻為19 kHz[19]。

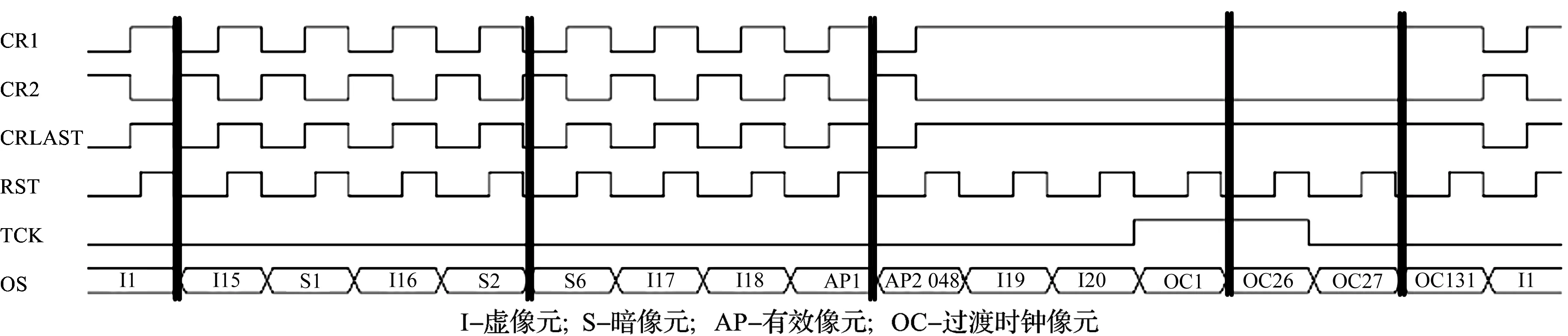

筆者設(shè)計的系統(tǒng)中,一次線掃描的像元數(shù)為2 205 個,其中有效像元數(shù)為2 048 個,在輸出有效像元前有18 個虛像元和6 個暗像元,在第2 048 個有效像元后還有2 個虛像元和131 個過渡時鐘像元。在2 048 個有效像元結(jié)束后產(chǎn)生一個轉(zhuǎn)移脈沖TCK,脈沖寬度為500 ns。FPGA需要輸出5 路驅(qū)動信號,線陣CCD才能正常工作。驅(qū)動信號分別是兩相時鐘信號CR1和CR2,寄存器末端讀出鉗位信號CRLAST、復(fù)位信號RST以及轉(zhuǎn)移信號TCK。驅(qū)動信號的時序相位關(guān)系如圖4所示。為了最大化采集速度,系統(tǒng)工作時鐘為40 MHz。本系統(tǒng)外部晶振頻率為80 MHz,通過MMCM核倍頻能夠得到320 MHz的全局時鐘,對該全局時鐘進(jìn)行計數(shù),以計數(shù)器的值作為參考,通過對計數(shù)器值的判定來決定信號脈沖的時刻與寬度。其中,CR1是占空比50%的40 MHz時鐘信號,CR2與CR1同頻反相,CRLAST通過硬件芯片分出,RST是占空比25%的40 MHz的時鐘,TCK是在有效像元結(jié)束后拉高。

圖4 IL-P3驅(qū)動時序圖Fig.4 Timing design of the IL-P3 driving

2.2 AD模數(shù)轉(zhuǎn)換模塊

本設(shè)計中CCD工作時鐘為40 MHz,由于AD采樣時鐘應(yīng)與CCD的工作時鐘相同,因此需要選用一款工作頻率能達(dá)到40 MHz的AD采樣芯片。ADI公司推出了一款專門針對CCD信號采樣的AD9945型號芯片,最大采樣頻率能達(dá)到40 MHz,支持快速12 位40 MSPS模數(shù)轉(zhuǎn)換,擁有低噪聲的暗電平鉗位電路,消除CCD暗電流影響,同時其內(nèi)部還集成了6~40 dB的可變增益放大器[20]。

正確配置AD的內(nèi)部寄存器及提供匹配的外部驅(qū)動時序,AD9945才能正常工作。Zynq芯片提供SCK,SDATA,SL信號驅(qū)動時序來進(jìn)行寄存器配置。在SL信號為0時,持續(xù)寫入寄存器值,當(dāng)連續(xù)寫入寄存器值時,只需要給出第1 個寄存器的地址位,如果寄存器數(shù)據(jù)位小于12 位時,需要將其補足。SCK信號頻率需要小于10 MHz,本設(shè)計中全局時鐘分頻產(chǎn)生頻率為1 MHz占空比為50%的 SCK信號,根據(jù)SCK信號設(shè)計一個52 位計數(shù)器,在計數(shù)器計數(shù)時SL信號拉低為0,其余時間拉高為1,在SCK每個上升沿對SDATA進(jìn)行數(shù)據(jù)寫入。

串行控制線連續(xù)寫入數(shù)據(jù)完成AD9945內(nèi)部寄存器配置后,還需要產(chǎn)生三路采樣時序完成AD9945的相關(guān)雙采樣功能。采樣時序由數(shù)據(jù)同步時鐘DATACLK、高電平采樣時鐘SHP和參考電平采樣時鐘SHD組成。設(shè)計時序如圖4所示,分別在SHP和SHD上升沿對CCD信號進(jìn)行采樣,10 個時鐘后,輸出兩次采樣差值得到的數(shù)字信號。DATACLK是一個占空比50%的40 MHz時鐘,SHP和SHD為占空比75%的40 MHz時鐘,且SHP和SHD相位差180°。根據(jù)320 MHz的全局時鐘信號設(shè)計1 個8 位計數(shù)器,以計數(shù)器的值作為參考,通過對計數(shù)器值的判定來決定信號脈沖的時刻和脈沖寬度,產(chǎn)生芯片要求的DATACLK,SHP,SHD信號,如圖5所示。

圖5 AD9945相關(guān)雙采樣時序圖Fig.5 Correlated double sampling timing of the AD9945

3 基于DDR的數(shù)據(jù)搬運模塊設(shè)計

3.1 PS-PL交互模塊

Zynq平臺內(nèi)部PS與PL之間互聯(lián)都是基于AMBA (Advanced microcontroller bus architecture)總線完成的。AMBA4.0總線包括3 種總線標(biāo)準(zhǔn),分別是AXI4協(xié)議標(biāo)準(zhǔn)、AXI4-Stream協(xié)議標(biāo)準(zhǔn)和AXI4-Lite[21]。其中,AXI接口共有AXI_ACP接口(加速器一致端口)、AXI_GP接口(AXI通用接口)和AXI_HP接口(AXI高性能接口)等3 種類型[21]AXI_HP接口是64 位的數(shù)據(jù)接口,可以為Zynq平臺提供最大的總帶寬,更適用于高性能或者高帶寬的任務(wù)。設(shè)計需要完成從PL端將數(shù)據(jù)寫入DDR的功能,所以自主設(shè)計了PS-PL交互模塊。為了最大化系統(tǒng)的采集性能和傳輸效率,本模塊采用的是AXI4總線協(xié)議與AXI-HP接口。

為了最大化系統(tǒng)間的傳輸效率,本系統(tǒng)使用數(shù)據(jù)位寬64 位的AXI_HP接口,突發(fā)長度256,一次突發(fā)傳輸可以傳送2 kB的數(shù)據(jù)。

PS-PL交互模塊由讀突發(fā)傳輸模塊和寫突發(fā)傳輸模塊組成。在寫突發(fā)傳輸模塊中,設(shè)計了一個數(shù)據(jù)位寬64位,深度4 096的DDR前級FIFO,其功能是將待寫入AXI4總線的數(shù)據(jù)緩存進(jìn)FIFO中,同時完成寫入時鐘到Zynq工作時鐘的時鐘域變換。為了保證寫入AXI4總線數(shù)據(jù)不為空,對進(jìn)入FIFO中的數(shù)據(jù)進(jìn)行計數(shù),當(dāng)進(jìn)入FIFO的數(shù)據(jù)個數(shù)大于2 048時,將DDR寫使能信號拉高。在接收到DDR寫使能有效信號后,拉高寫突發(fā)使能信號W_FLAG及寫數(shù)據(jù)有效信號WVALID。根據(jù)寫突發(fā)使能信號與寫地址準(zhǔn)備信號AWREADY,生成寫地址有效信號AWVALID。當(dāng)AWVALID信號與AWREADY信號同時為高時,生成寫地址信號AWADDR。檢測寫數(shù)據(jù)準(zhǔn)備信號WREADY,當(dāng)WVALID信號與WREADY信號同時為高時,進(jìn)行寫數(shù)據(jù)操作。通過對寫數(shù)據(jù)進(jìn)行計數(shù),當(dāng)一次突發(fā)傳輸完成最后一個數(shù)據(jù)的傳輸時,拉高WLAST信號。檢測WLAST信號,當(dāng)WLAST信號為高時拉低寫突發(fā)使能信號W_FLAG及寫數(shù)據(jù)有效信號WVALID。寫響應(yīng)準(zhǔn)備信號BREADY一直拉高。當(dāng)完成一次寫突發(fā)傳輸后,拉高DDR讀使能信號。當(dāng)DDR讀使能信號有效時,拉高讀突發(fā)使能信號R_FLAG及讀地址有效信號ARVALID。檢測讀地址準(zhǔn)備信號ARREADY,當(dāng)ARREADY與ARVALID都為高時生成讀地址信號ARADDR。通過檢測讀數(shù)據(jù)準(zhǔn)備信號RREADY與讀數(shù)據(jù)有效信號RVALID,當(dāng)RREADY信號與RVALID都拉高時,進(jìn)行讀突發(fā)傳輸。檢測RLAST信號,當(dāng)RLAST信號拉高時,RREADY信號拉低。當(dāng)數(shù)據(jù)從DDR讀出后,寫入深度為4 096的異步FIFO中,完成AXI4總線讀突發(fā)傳輸。

3.2 數(shù)據(jù)預(yù)處理模塊

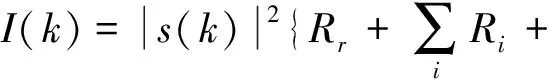

(1)

式中:k為波數(shù);s(k)為電場強度的振幅;Rr為參考臂的功率反射率;Ri為i點的背向功率散射率;hi為距離樣品表面di位置的對應(yīng)光程差,hi=2(l+nidi),其中l(wèi)是參考鏡的虛像和樣品表面之間的距離,ni是i點的折射率,di是樣品散射點i的深度。第1 項、第2 項為直流項,第3 項為色散噪聲。通過對手指表皮的1 次B-scan(橫向掃描),共有500 組B-scan(軸向掃描)的數(shù)據(jù),對一個B-scan中所有光譜進(jìn)行求平均,并將每個B-scan信號都減去光譜平均值,就可以去除直流項。通過對光學(xué)平臺的硬件補償來去除色散噪聲,那么

(2)

對其進(jìn)行傅里葉變換,那么FD-OCT的圖像函數(shù)i(h)為

(3)

忽略第一項鏡像噪聲

(4)

CCD采樣數(shù)據(jù)是以波長為變量的,將其轉(zhuǎn)為以波數(shù)為變量的數(shù)據(jù),就需要對CCD數(shù)據(jù)進(jìn)行插值操作。本模塊中通過求平均的方式去除數(shù)據(jù)的直流噪聲,對減直流后的數(shù)據(jù)進(jìn)行插值操作,最后通過傅里葉變換獲得樣品深度信息。算法流程如圖6所示。

圖6 算法流程圖Fig.6 Flow chart of the algorithm

1 條A-line中共含2 048 個像素點,單個像素點占用12 位的內(nèi)存空間,在實際使用中用16 位的內(nèi)存空間的數(shù)據(jù)類型來對每個像素點信息進(jìn)行存儲。算法在FPGA中的實現(xiàn)流程如圖7所示,OCT數(shù)據(jù)緩存寫入DDR中,以1 次B-scan數(shù)據(jù)作為數(shù)據(jù)處理單位。將500 組A-line數(shù)據(jù)累加依次存入深度為2 048的RAM1中,調(diào)用除法器獲得光譜平均值,并依次存入深度為2 048的RAM2中,之后再次從DDR中讀取此次B-scan數(shù)據(jù),將每次A-line的數(shù)據(jù)存入深度為2 048的RAM3中,與RAM2中的光譜平均值作減直流。將減直流后的數(shù)據(jù)存入深度為2 048的RAM4和RAM5中,將插值系數(shù)存入深度為4 096的ROM1中,其中寫入RAM4和RAM5的信號相差1 個地址。當(dāng)ROM1中插值系數(shù)大于RAM4的讀地址時,RAM4與RAM5的讀地址增加。調(diào)用FPGA中DSP資源完成乘法操作,加上RAM5中的數(shù)據(jù)完成插值操作。插值后的數(shù)據(jù)通過調(diào)用FFT IP核完成最終的傅里葉變換操作。

圖7 算法在FPGA實現(xiàn)流程圖Fig.7 The process of achieving algorithm in FPGA

3.3 網(wǎng)絡(luò)通信模塊

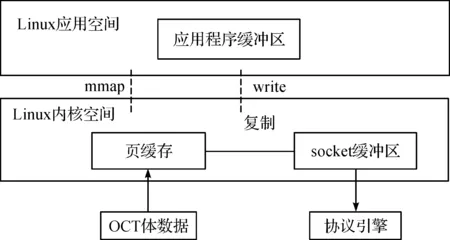

網(wǎng)絡(luò)通信模塊主要利用內(nèi)存映射機制及TCP/IP協(xié)議搬運已經(jīng)預(yù)處理的數(shù)據(jù)到上位機中。數(shù)據(jù)拷貝到內(nèi)核緩沖區(qū)之后,接著拷貝到socket緩沖區(qū),之后從socket緩沖區(qū)拷貝到協(xié)議引擎,最后通過千兆網(wǎng)線將數(shù)據(jù)上傳到上位機進(jìn)行存儲與處理。應(yīng)用程序主要分為兩部分:一是運行在下位機的客戶端程序,作用為搬運PL端DDR中體數(shù)據(jù)到socket套接字;二是運行在上位機Linux系統(tǒng)下的服務(wù)器程序,作用為接收下位機發(fā)送的數(shù)據(jù),兩者進(jìn)行通訊利用TCP/IP協(xié)議建立連接。

網(wǎng)絡(luò)通信模塊如圖8所示,Linux應(yīng)用程序訪問PL端DDR時,會先利用系統(tǒng)調(diào)用mmap()進(jìn)行內(nèi)存映射,映射成功之后,Linux系統(tǒng)便可訪問PL端內(nèi)存。系統(tǒng)應(yīng)用程序通過不斷檢測觸發(fā)信號變化的方法判斷PL端DDR緩沖區(qū)的狀態(tài),若檢測到觸發(fā)信號便進(jìn)入緩沖區(qū)搬運數(shù)據(jù)。

映射之后應(yīng)用程序利用系統(tǒng)調(diào)用write()搬運PL端緩沖區(qū)體數(shù)據(jù)到Linux下socket套接字中,過程中會先將數(shù)據(jù)拷貝到Linux內(nèi)核緩沖區(qū),用戶空間應(yīng)用程序會和操作系統(tǒng)共享這個緩沖區(qū),這樣系統(tǒng)內(nèi)核和用戶空間就不需要進(jìn)行任何的數(shù)據(jù)拷貝操作。

圖8 網(wǎng)絡(luò)通信模塊程序示意圖Fig.8 Schematic diagram of network communication module

4 實驗結(jié)果

系統(tǒng)的掃描工作流程如下所述:裝置上電之后,初始化Zynq處理器控制模塊,然后判斷裝置是否與PC機連接,如未連接則裝置空閑(休眠),否則進(jìn)一步判斷同步觸發(fā)模塊是否有觸發(fā)信號輸入,如沒有觸發(fā)信號則裝置空閑(休眠),否則Zynq處理器控制模塊執(zhí)行驅(qū)動時序,其他各模塊比如CCD傳感器模塊、A/D轉(zhuǎn)換模塊、PS-PL交互模塊和數(shù)據(jù)預(yù)處理模塊等互相配合完成數(shù)據(jù)快速采集及預(yù)處理,之后對裝置的傳輸進(jìn)行確認(rèn),將緩存在DDR3的數(shù)據(jù)通過千兆網(wǎng)口模塊,將數(shù)據(jù)傳輸至上位機。數(shù)據(jù)傳輸結(jié)束之后,裝置返回判斷是否有觸發(fā)信號,為下一次采集做準(zhǔn)備。系統(tǒng)最終采集手指數(shù)據(jù)線速率能到18 kHz,軸線分辨率為7 μm,橫向分別率11 μm,探測深度達(dá)到1 mm。

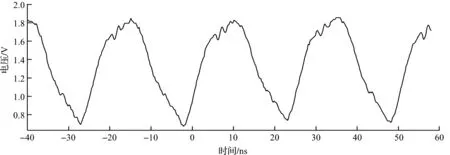

系統(tǒng)實際工作中,由于TCK驅(qū)動電路帶反向功能,所以FPGA端TCK原始輸出信號反向輸出。圖9為使用邏輯分析儀抓取FPGA輸出的CCD信號。在確保線陣CCD的信號時序與偏置電壓都正確后,將線陣CCD連在電路板上,上電測試輸出信號OS是否正常。測試使用較強的500~900 nm波長的光線照射線陣CCD的感光面,使其不斷積累電荷信號,通過示波器觀察輸出波形。圖10為示波器測出的CCD輸出的OS信號。

圖9 FPGA輸出的CCD信號時序圖Fig.9 The timing of CCD from FPGA

圖10 輸出信號OS實測波形Fig.10 The measured waveform of output signal OS

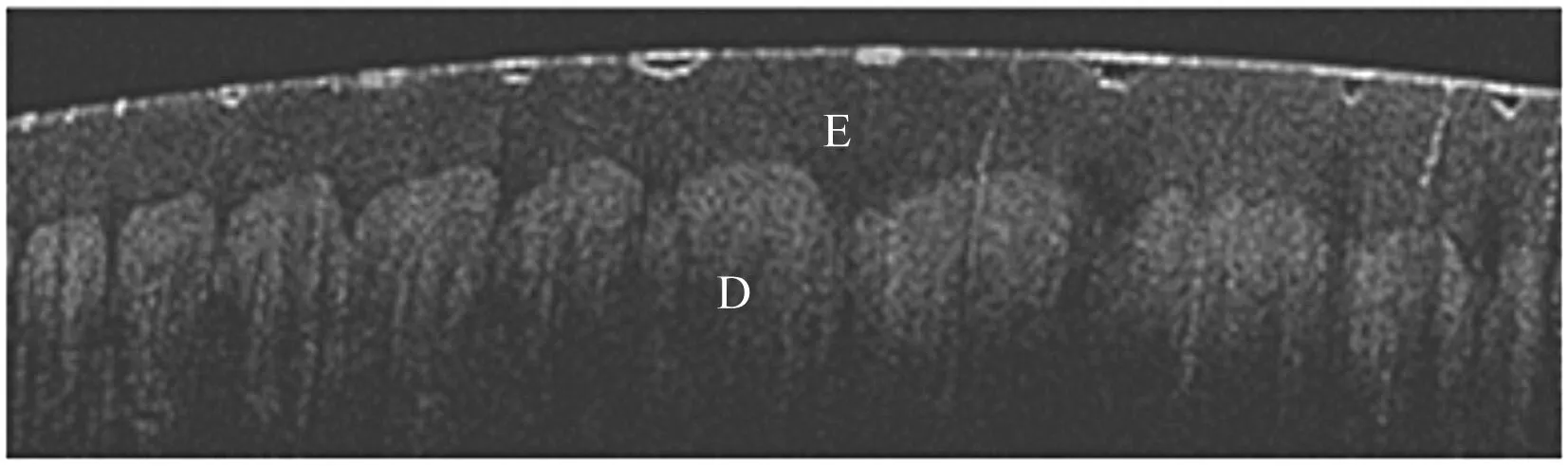

在完成AD9945的寄存器配置后,為AD9945提供相應(yīng)的驅(qū)動信號,AD9945開始正常工作。圖11為使用邏輯分析儀抓取FPGA輸出的AD9945驅(qū)動信號,其中DATACLK信號上升沿需要在SHP上升沿和SHD下降沿之間,滿足芯片正常工作要求。最終處理過后的數(shù)據(jù)通過千兆網(wǎng)口傳給上位機,處理后的數(shù)據(jù)是一幅幅2D剖面圖像數(shù)據(jù)的集合,可以獲取手指皮下指紋。圖12為手指OCT二維剖面圖,其中E代表表皮,D代表真皮層。

圖11 AD9945的相關(guān)雙采樣時序圖Fig.11 The simulation of correlated double sampling timing

圖12 手指OCT二維剖面圖Fig.12 Two-dimensional cross-section of the finger OCT

5 結(jié) 論

在分析頻域OCT原理的基礎(chǔ)上,設(shè)計了基于Zynq芯片的手指OCT數(shù)據(jù)采集系統(tǒng),以解決傳統(tǒng)識別系統(tǒng)體積大、功耗大和擴展性差的問題。在分析Zynq芯片優(yōu)勢的基礎(chǔ)上,提出了OCT數(shù)據(jù)采集系統(tǒng)的總體架構(gòu)。在分析CCD及模數(shù)轉(zhuǎn)換器驅(qū)動時序的基礎(chǔ)上,提出了IL-P3和AD9945的驅(qū)動電路設(shè)計。邏輯分析儀抓取FPGA輸出信號和信號OS的測量結(jié)果表明,筆者設(shè)計的時序發(fā)生器滿足硬件驅(qū)動信號的要求。在分析Zynq芯片中PS與PL間內(nèi)部交互的基礎(chǔ)上,設(shè)計了基于AXI4總線的數(shù)據(jù)交互模塊。基于對系統(tǒng)干涉光譜信號的分析,設(shè)計了基于FPGA的算法預(yù)處理模塊。最后,實現(xiàn)了基于內(nèi)存映射機制及TCP/IP協(xié)議網(wǎng)絡(luò)的通信模塊。筆者提出的設(shè)計方案減少了采集系統(tǒng)的電子器件數(shù)目,提高集成度的同時,簡化了設(shè)計復(fù)雜度。