多功能直接數(shù)字頻率合成器設(shè)計

馬子軒

摘? ?要:本文使用QuartusII9軟件對SmartSOPC試驗箱中的FPGA進行編程,使FPGA實現(xiàn)直接數(shù)字頻率合成器(DDS)的核心功能。DDS的核心器件包括分頻器、頻率調(diào)節(jié)預(yù)置電路、累加器、波形儲存器等模塊。在后期的擴展功能設(shè)計中加入了開關(guān)按鍵、LED數(shù)碼管、測頻電路、顯示控制電路、波形選擇電路等模塊,實現(xiàn)了輸出頻率與相位可控和可視化、輸出多種波形、頻率可測等功能的多功能直接數(shù)字頻率合成器。

關(guān)鍵詞:直接頻率合成器? FPGA

中圖分類號:TN 74? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?文獻標(biāo)識碼:A? ? ? ? ? ? ? ? ? ? ? ?文章編號:1674-098X(2019)05(b)-0006-02

1? 設(shè)計原理

1.1 DDS系統(tǒng)組成

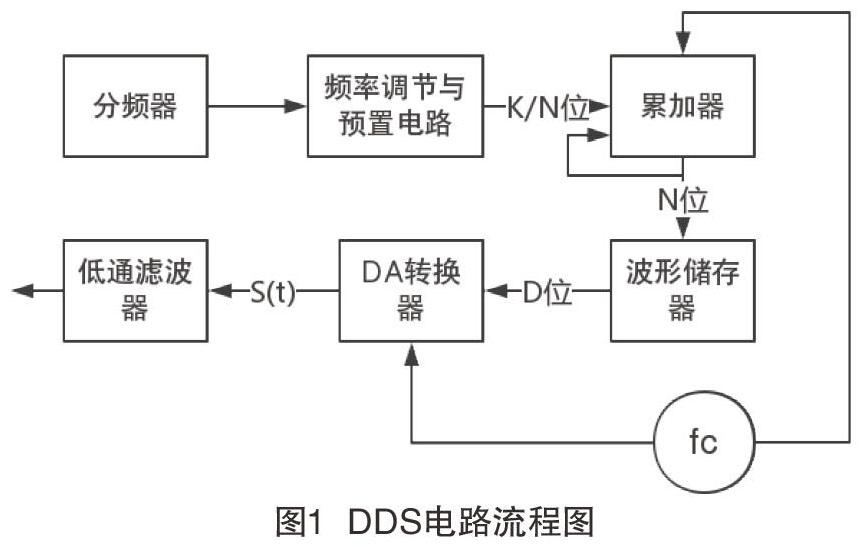

DDS系統(tǒng)核心由分頻器、頻率調(diào)節(jié)與預(yù)置電路、累加器、波形存儲器構(gòu)成。頻率預(yù)置電路負(fù)責(zé)調(diào)節(jié)頻率設(shè)定位(K)和相位設(shè)定位(P),其中K即為讀取ROM表時的步長,P即為讀取ROM表時的開始位置。由此可得其輸出的頻率為Kfc/N,其中fc為DA轉(zhuǎn)換器的采樣頻率,N為ROM表的長度。根據(jù)奈奎斯特采樣定理可知,K最大為N/2。

累加器由n位加法器+n位寄存器組成,負(fù)責(zé)在激勵信號的作用下,累加相位,然后將相位信息輸出到波形儲存器中讀出波形幅值信息,將幅值信息輸送到DA轉(zhuǎn)換器中,經(jīng)過低通濾波器后得到輸出波形。

1.2 DDS的電路組成

整體的DDS電路由四大部分組成,圖1所示的低通濾波器和DA轉(zhuǎn)換器由SmartSOPC試驗箱提供。分頻器電路對開發(fā)板提供的穩(wěn)定48MHz信號進行了分頻,以提供給各個電路模塊使用,如表1所示。

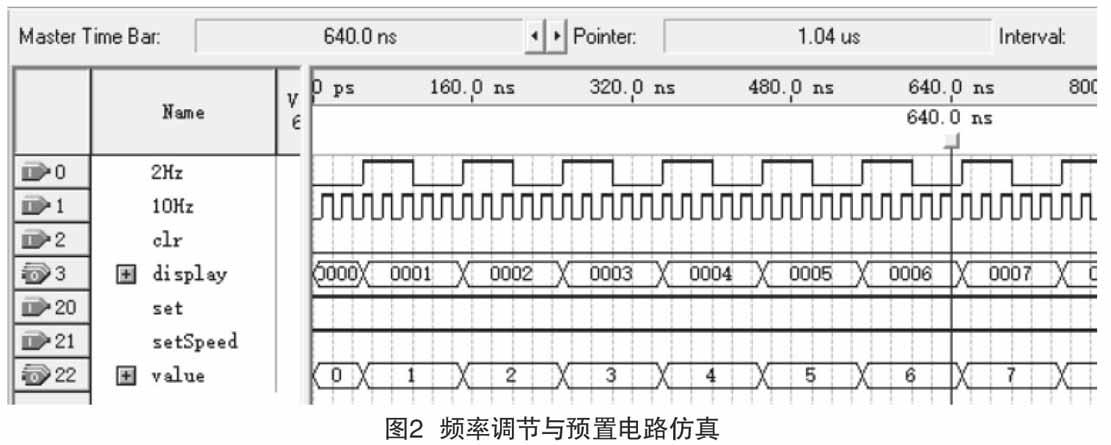

頻率預(yù)置電路用于調(diào)節(jié)K和P,其中K和P的調(diào)節(jié)范圍均設(shè)置為1~1024,我們提供了兩種調(diào)節(jié)速率(快調(diào)和慢調(diào)),分別使用2Hz和10Hz的調(diào)節(jié)脈沖信號作為激勵。

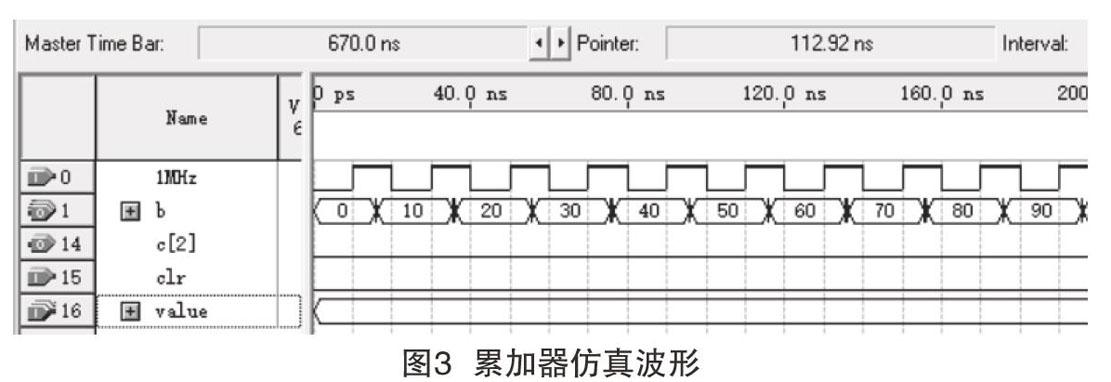

累加器由三片7483四位加法器實現(xiàn),將加法計算出的結(jié)果輸送給D觸發(fā)器寄存,等待下一個上升沿到來后將這個數(shù)發(fā)送到加法器的輸入端,實現(xiàn)累加。這里接入的是1MHz的脈沖信號,這個脈沖的頻率需要和ROM的讀取頻率相同。

波形儲存器為12位尋址,相當(dāng)于將一個周期的正弦信號離散成樣值序列,將每個樣值對應(yīng)的幅值以10位二進制輸入到ROM中。在ROM的輸入端加入使能引腳,命令電路只讀取已經(jīng)使能的ROM,這樣可以節(jié)省電路的性能損耗,同時也給波形選擇帶來了極大的方便。

為防止用戶在操作時的抖動,加入除顫電路。利用一個集成的D觸發(fā)器進行除顫,除顫電路的頻率是10Hz。

2? 附加功能

在設(shè)計完基礎(chǔ)的DDS功能之后,為了實現(xiàn)與客戶的友好交互,繼續(xù)設(shè)計了波形選擇,測頻等。

2.1 波形選擇

DDS需要輸出多種波形,需要通設(shè)計一個ROM選擇電路來實現(xiàn)不同波形的切換。

波形選擇模塊主要由74160模十計數(shù)器、74138譯碼器、兩個8選1的總線選擇器構(gòu)成。74160用來計數(shù)從而選擇波形;74138將計數(shù)的結(jié)果譯碼,來選擇哪個ROM被讀取;8選1總線選擇器用來將從ROM中讀取的數(shù)據(jù)選擇出來,送到DA轉(zhuǎn)換器轉(zhuǎn)換。

2.2 測頻功能

此功能用于測量此時輸出的波形的頻率,并將其輸出在數(shù)碼管上。其基本原理是讀取ROM中的數(shù)據(jù)的峰值出現(xiàn)的時刻,當(dāng)峰值出現(xiàn)時計數(shù)器就+1,在T=1s的范圍內(nèi),計數(shù)器的值即為輸出信號的頻率。

3? 仿真

下面羅列出各個模塊的仿真情況。其中分頻電路和波形存儲電路因仿真時間較長,在這里不提供仿真結(jié)果。

4? 示波器測試結(jié)果

由于測試結(jié)果較多,在這里僅提供兩種示波器的結(jié)果。一種是基本的三角函數(shù)信號,一種是經(jīng)過設(shè)計的一箭穿心圖樣,如圖4、5所示。

參考文獻

[1] 王靜.基于FPGA直接數(shù)字頻率合成器DDS的設(shè)計[J].科技信息,2012(23):113-114.

[2] 蔣立平,姜萍,譚雪琴,等.數(shù)字邏輯電路與系統(tǒng)設(shè)計[M].北京:電子工業(yè)出版社,2013.

[3] 鄭燕,郝建國,黨劍華.基于VHDL語言與Quartus II軟件的可編程邏輯器件應(yīng)用與開發(fā)[M].北京:國防工業(yè)出版社,2007.

[4] 楊東霞,巨永鋒.基于FPGA和DDS的數(shù)字調(diào)制信號發(fā)生器設(shè)計與實現(xiàn)[J].電子設(shè)計工程,2013,21(6):90-93.