一種A/D轉換電路的設計與應用

呂小鳳,杜 丹,張萬玉

(1.中國電子科技集團公司第五十四研究所,河北 石家莊 050081;2.陸裝駐石家莊地區第一軍代室,河北 石家莊 050081;3.陸軍裝備部裝備項目管理中心,北京 100071)

0 引言

模擬數據的采集與處理是信息技術的一個重要分支,廣泛應用于地空信息傳輸系統中。隨著信息技術的高速發展和對控制要求的不斷提高,地空信息系統對模數轉換速度和精度要求也在不斷提高[1]。A/D轉換芯片作為模擬量采集的核心部件,其內部ADC容易受到輸入信號、電路布局以及芯片自身工藝的影響,使轉換結果無法滿足系統控制要求[2]。受硬件發展水平的限制,傳統的地空信息系統中,通常采用單片機對A/D轉換芯片進行控制的方式來完成模擬信號的采集和轉換,處理速度慢,外圍控制通過FPGA完成,硬件電路結構繁雜,軟件設計中數據交互同時涉及到單片機和FPGA,可靠性不高。鑒于以上A/D轉換發展與應用存在的兩大瓶頸:① A/D轉換器的速率和性能;② 可編程邏輯器件的處理速度[3],本文利用MAXIM公司具有12位高精度的多通道A/D轉換芯片和具有高速數據處理能力的ALTERA公司Stratix系列+5 V工作電壓的FPGA作為主控芯片實現了A/D轉換,不僅接口簡單、轉換速度快、精度高[4],而且利用延時調整等技術解決了A/D轉換芯片與FPGA之間的高速數據傳輸問題。

1 A/D采集轉換控制電路的設計

1.1 方案設計

設計之初,考慮到應用的可擴展性,要求可對多路模擬數據進行轉換,常用的設計方法有2種:① 電路使用多片A/D轉換芯片,每片對一路模擬信號進行轉換,多片芯片同步工作;② 電路選用多通道A/D轉換芯片,通過軟件控制依次完成多路模擬信號的轉換。

顯然,方案1可滿足系統的實時性和同步性要求,但是針對目前的系統小型化需求,芯片使用數量多,占電路板空間大,而且外圍電路復雜[5],大大增加了PCB設計難度。相較之下,方案2電路簡化,雖然對軟件控制的要求較高,但應用上更加靈活[6]。

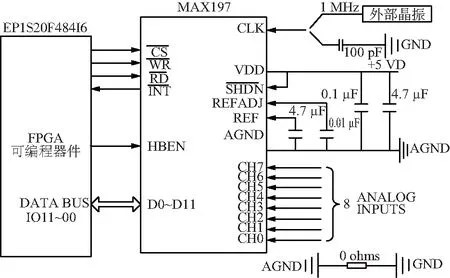

本設計使用的FPGA可編程器件選用ALTERA公司Stratix系列的EP1S20F484I6N,該芯片工作電壓為+5 V,A/D轉換器選用MAXIM公司的8通道12位高精度MAX197芯片,該芯片僅需+5 V供電,工作電壓與EP1S20F484I6N相匹配,二者硬件管腳可以直接相連,不需再使用電平轉換芯片,極大簡化了電路設計。

1.2 電路實現

本文設計重點是為完成A/D轉換的MAX197芯片外圍電路提供可靠接口,實現多通道的模擬數據采集轉換功能。硬件電路主要由模擬數據接收和控制轉換處理電路組成。

為了保證電路的轉換精度和可靠性,合理的電路及PCB設計非常重要[7],尤其對于模數混合電路,如何減少模擬電路和數字電路之間的相互串擾,也是要精心考慮的問題[7-8]。

本設計在PCB優化布局和走線的基礎上,將數字地和模擬地之間用0 Ω電阻連接,這樣可保證直流電位相等,能有效限制環路電流,抑制噪聲;否則,模擬信號將會受到干擾,嚴重影響轉換結果。

圖1 A/D轉換控制處理電路

2 軟件設計

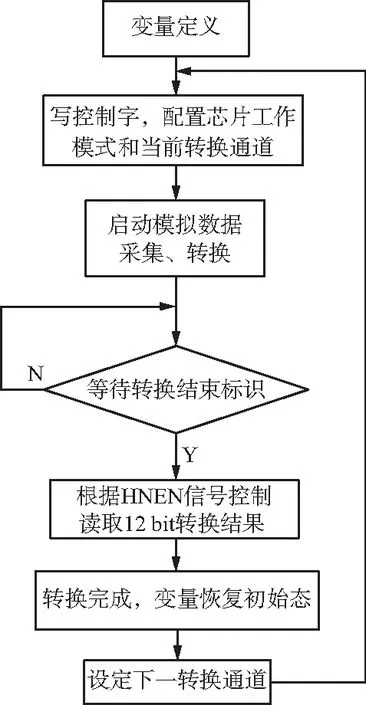

軟件設計采用Verilog HDL語言利用FPGA編程,通過有限狀態機模式[13],實現對MAX197運行模式的配置、模擬數據采集和轉換的控制。

程序流程如圖2所示。

圖2 A/D轉換程序流程

在本系統實際應用中,A/D轉換只是硬件電路板上FPGA所需完成功能的一部分且數據采集對時間無嚴格要求。因此,為了保證設計中所用時鐘的全局性[14-15],MAX197選擇在外部時鐘模式下工作,信號獲取方式選用時序關系更為簡明的內部自動采集模式,模擬信號量程選擇0~5 V,則寫入的8位控制字為{5’b0,chNum},其中,chNum為模擬通道,數據位寬3 bit,有效范圍為3’b000~3’b111,用來表示當前選定的模擬數據通道。

分步狀態執行過程如下:

iSt0:初始化A/D轉換芯片。nCS,nWR,nRD,HNEN信號置1,數據讀寫使能triEn置0;

iSt1:nCS信號置0,拉低片選信號;

iSt2:nWR信號置0,拉低寫信號,準備產生寫信號的上升沿;

iSt3:數據讀寫使能triEn置1,并按控制字格式編排數據準備寫入數據總線,數據內容為{5’b0,chNum};

iSt4:nWR信號置1,拉高寫控制信號,產生上升沿,此時,數據讀寫使能triEn有效,將控制字寫入數據總線配置A/D轉換芯片MAX197的運行模式,同時控制字中選定的模擬輸入通道上的數據開始進行采集;

iSt5:數據讀寫使能triEn置0,并將nCS信號置1,拉高片選信號,不再對數據總線進行操作,同時等待模擬數據采集轉換完成。當檢測到nINT信號為低電平時,表示模擬數據已轉換完成,轉換結果已在數據總線上等待讀出[16],否則,繼續等待;

iSt6:nCS信號置0,使片選信號有效;

iSt7:nRD信號置0,拉低讀控制信號,準備從數據總線上讀取轉換結果;

iSt8:HNEN信號從狀態iSt0時一直為高電平,此時讀控制有效,從數據總線上讀取轉換結果的高4 bit,當從總線上開始讀取轉換結果時,轉換結束標識信號nINT恢復高電平,等待下一次轉換;

iSt9:HNEN信號置0,準備讀取轉換結果的低8 bit;

iSt10: HNEN信號為低電平且讀控制有效,從數據總線上讀取轉換結果的低8 bit;

iSt11:12 bit轉換結果已全部從數據總線上讀出,nRD信號置1,拉高讀控制信號,不再對數據總線進行讀操作,同時,HNEN信號置1,恢復到初始態;

iSt12:nCS信號置1,拉高片選信號,使片選信號無效,使所有控制和狀態信號都恢復到初始態。

當所有控制和狀態信號都恢復到初始態值時,表示對當前模擬通道的轉換操作已全部完成,狀態機跳轉到iSt0,開始進行下一通道轉換操作,以此循環8次,可實現8個模擬通道的順序轉換。開啟新一輪的轉換時,當模擬通道的信號量程、極性有變或需改變芯片的運行模式時,需按格式對控制字進行重新設置。如果在當前轉換周期未結束時寫一個新的控制字將使當前轉換失效,并啟動一次新的采集轉換過程[17]。

3 系統仿真

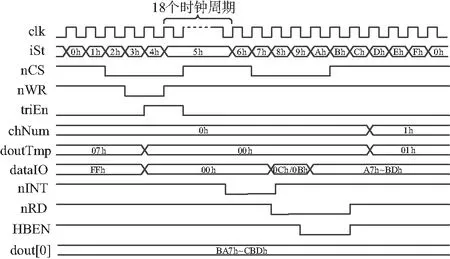

在Quartus II開發平臺上,用Verilog語言進行程序設計,并用Quartus II軟件的嵌入式邏輯分析儀Signal Tap II通過JTAG端口來查看以實際系統速率運行的系統內的各設計節點,從而實現對FPGA設計內部節點的訪問。本設計的主時鐘將外部晶振從FPGA芯片的全局時鐘管腳輸入,使用Alter公司的PLL內置模塊對輸入的外部時鐘倍頻[18],對高頻鐘分頻后為MAX197提供1 MHz時鐘。在模擬通道1上接入+5 V電壓,數據采集轉換時序如圖3所示。

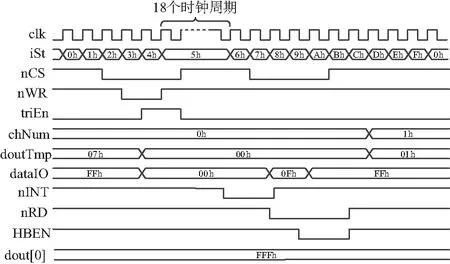

圖3 通道1數據采集轉換時序

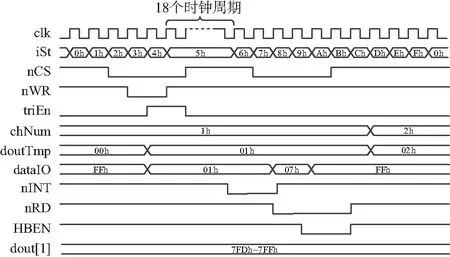

圖3中,clk是外部時鐘模式下由外部晶振為MAX197芯片提供的時鐘;iSt為狀態機;doutTmp為FPGA內部寄存器,存儲設置的控制字;dataIO為MAX197與FPGA交互的8 bit并行數據線;當nCS有效,nWR為低電平時,triEN使能將寄存器內的數寫入數據線,初始化控制字。dout[i]為轉換結果。軟件設計中,所有賦值操作使用的都是非阻塞型過程賦值,則對應的狀態機中,每一次信號的賦值要到下一個時鐘周期來臨時才會執行。通過時序圖可以看到,在狀態機iSt為4時,設置好的控制字寫入了數據總線dataIO,配置好MAX197轉換芯片的運行模式,并選定當前需轉換的模擬通道為通道1。狀態機iSt為5時,nWR的上升沿到來,開始采集信號,經過18個時鐘周期,信號采集并轉換完成;此時,轉換結束標識信號nINT變為低電平,并開始向數據線上準備轉換結果。狀態機iSt為8時,nRD為低電平,開始從數據線上讀取轉換結果,nINT恢復為高電平等待下一次轉換過程。dout[0]顯示模擬通道1上+5 V的電平信號轉換結果不穩定,數值一直在12’hBA7~12’hCBD間不停跳動,換算成電平值則為3.63~3.98 V。說明每次對+5 V電平采樣時,采樣到的電平值不穩定且數值偏差很大,模擬信號受到了嚴重干擾。檢查電路布線,發現模擬地與數字地間未做等電位處理,可能造成模擬信號不能正確識別。將MAX197芯片的第28管腳和15管腳直接短接,并在模擬通道1上通過直流可調電源接入+5 V電壓,模擬通道2上接入約+2.5 V電壓,數據采集轉換時序如圖4和圖5所示。

圖4 優化后通道1數據采集轉換時序

從圖4轉換結果可以看出,電路經初步優化后,+5 V電平的轉換結果穩定,且轉換值12’hFFF正確。

圖5 優化后通道2數據采集轉換時序

通道1轉換完成后在轉換周期結束前,通道號加1,準備進行通道2的數據轉換。圖5中,在新一輪轉換周期中,chNum值由0變為1,表示當前選定模擬通道2,轉換芯片的運行模式沒有改變,此時,控制字doutTmp設置為’h01,dout[1]顯示模擬通道2上+2.5 V的電平信號轉換結果為12’h7FD~12’h7FF。

結合圖4和圖5,模擬信號經初步抗干擾優化處理后,+5 V,+2.5 V信號轉換結果正確且穩定,芯片A/D采集轉換功能正常。

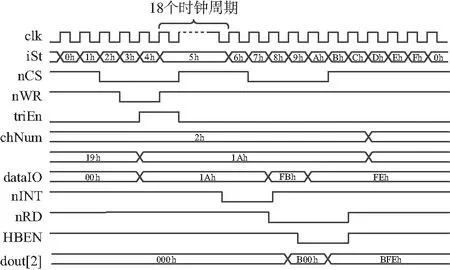

為測試軟件的通用性,改變模擬通道信號量程和極性,將模擬通道3上信號量程設置為±10 V,并將通道3接入穩定-5 V電壓,數據采集轉換結果如圖6所示。

圖6 通道3數據采集轉換時序

圖6中,由于通道3信號量程改變,在進行數據采集轉換前,控制字doutTmp應設置為{5’b11,3’b10},表示當前選定模擬通道3,且信號量程為±10 V,dout[2]顯示模擬通道3上-5 V的電平信號轉換結果為12’hBFE,轉換結果與實際相符,芯片A/D采集轉換功能依舊正常。

4 系統測試

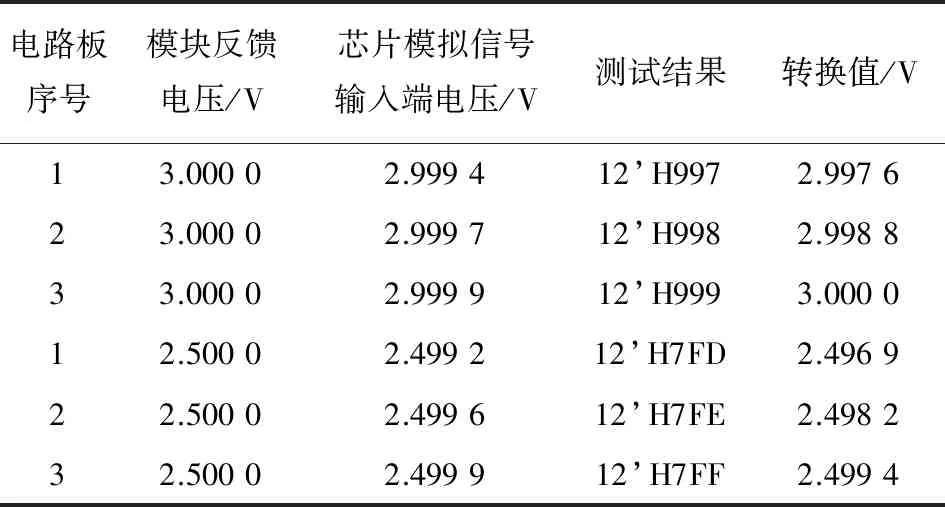

在實際地空信息系統特定功能機箱內,將重新優化設計后的電路板與功放模塊連接,模塊反饋的模擬電壓作為A/D轉換電路的輸入信號來檢測硬件電路及軟件的實用性。在數據轉換測試中,通過功能機箱上的狀態顯示屏可查看12 bit A/D轉換結果。調節反饋電壓,當電壓值為單極性且在0~+5 V間變化時,轉換結果在12’h000~12’hFFF間變化。調節反饋電壓分別穩定至+3.0 V,+2.5 V時,使用3塊電路板進行測試,轉換結果如表1所示。

表1 A/D轉換測試結果

電路板序號模塊反饋電壓/V芯片模擬信號輸入端電壓/V測試結果轉換值/V13.00002.999412’H9972.997623.00002.999712’H9982.998833.00002.999912’H9993.000012.50002.499212’H7FD2.496922.50002.499612’H7FE2.498232.50002.499912’H7FF2.4994

5 結束語

MAX197的采樣精度和其時序密切相關,本設計電路使用FPGA做主控芯片,處理速度快,通過表1的測試數據,對3塊不同的電路板灌裝本設計軟件后,誤差均不超過3 mV,轉換精度高,且多通道轉換模式和數據處理通過FPGA編程控制,在硬件電路不變的情況下修改軟件程序就能滿足多種數據采集需求[19]。該設計已應用到實際的地空信息系統中,具有一定的實用價值,同時由于該設計采用Verilog語言完成電路的軟件設計,易用性和可移植性得到了加強,不僅使硬件功能的設計修改和產品升級變得十分方便,而且極大地提高了電子系統的靈活性和通用性。結合圖3~圖5的實驗數據,設計還強調了模數混合電路設計中信號抗干擾處理的重要性,具有一定的學習參考價值。