電子信息類研究生綜合實踐平臺開發與教學設計

黃武煌,葉 芃,邱渡裕,楊擴軍,蔣 俊,張沁川,曾 浩,郭連平,袁 淵,潘卉青

(電子科技大學 自動化工程學院, 成都 611731)

0 引 言

為了落實國家對高層次應用型人才培養的戰略需求,探索提高創新能力和提升職業能力的研究生培養模式已勢在必行[1-2]。電子信息類專業是一門應用現代化電子、信息、通信技術進行信息獲取、處理和控制的學科,具有極強的工程應用性。該類專業所培養的研究生需要掌握扎實的電子技術與信息系統設計、開發和應用知識,具備較強的解決復雜工程問題的能力,是當前各行各業急需的高層次工程技術人才[3-4]。這就需要在具體的科研項目研發過程中得以系統的技能訓練并積累相關設計、調試的實踐經驗。然而,我國研究生教育長期以來所形成的以理論教學為主的培養模式,在實踐教學環節上相對薄弱,使得培養過程很難獲得系統且充分的實踐鍛煉[5-6]。本文將結合電子信息類專業的共同特點來探討研究生綜合實踐平臺的開發與教學設計。

1 綜合實踐平臺開發

1.1 開發需求

為了達到培養目標,電子信息類專業研究生所須掌握的現代電子技術理論及其系統設計的原理和方法非常多,其中公共專業基礎課程包括模擬電路基礎、數字邏輯設計、微機原理與系統設計、信號與系統、數字信號處理、高級程序語言設計等。該類課程所涉及的知識點多、知識面廣,然而由于各個教師知識面和實踐內容都具有特定的范圍,通常在以往的實踐教學環節中都側重于某些理論的驗證和單一器件的功能應用,使得實驗所涉及的知識點較為零散,缺乏系統性,無法傳承一個完整的電子系統[6-7]。而且,由于學生人數眾多、實驗設備昂貴,一般都是幾個同學1組共同來完成某個實驗。這就導致大多數學生失去了獨立的實踐思考空間,無法達到工程設計的全面鍛煉目的。

當前,電子信息類專業研究生的實踐鍛煉機會主要靠導師所在的教研室課題組,但不同導師所承擔科研項目和指導方式存在較大的差異,無法對研究生實現系統性的實踐技能培養。即使導師所在的課題組能給予充分的鍛煉機會,而由于時間、進度等多方面原因限制,導師在指導研究生時也無法確保每個研究生都能得到手把手的及時指導。這使得研究生動手能力培養在大多數時間只能依靠個人自學及師兄弟的傳幫互帶。由于來自不同高校的研究生的理論基礎及接受能力差異較大,這使得有些研究生進入課題組后無法快速進入項目研發的角色,面對科研問題缺乏基本的分析方法和調試手段,一般需要花費幾個月甚至半年以上的時間才能完成基本的科研實踐技能鍛煉。

結合當前電子信息類研究生綜合實踐課程的特點和需求,在研究生學習初期階段急需有一門能夠覆蓋公共基礎課程知識面且滿足基本工程設計和應用創新實踐的多學科綜合實踐課程,為后續的科研解決復雜工程問題打下堅實的基礎[4-5]。

1.2 平臺方案

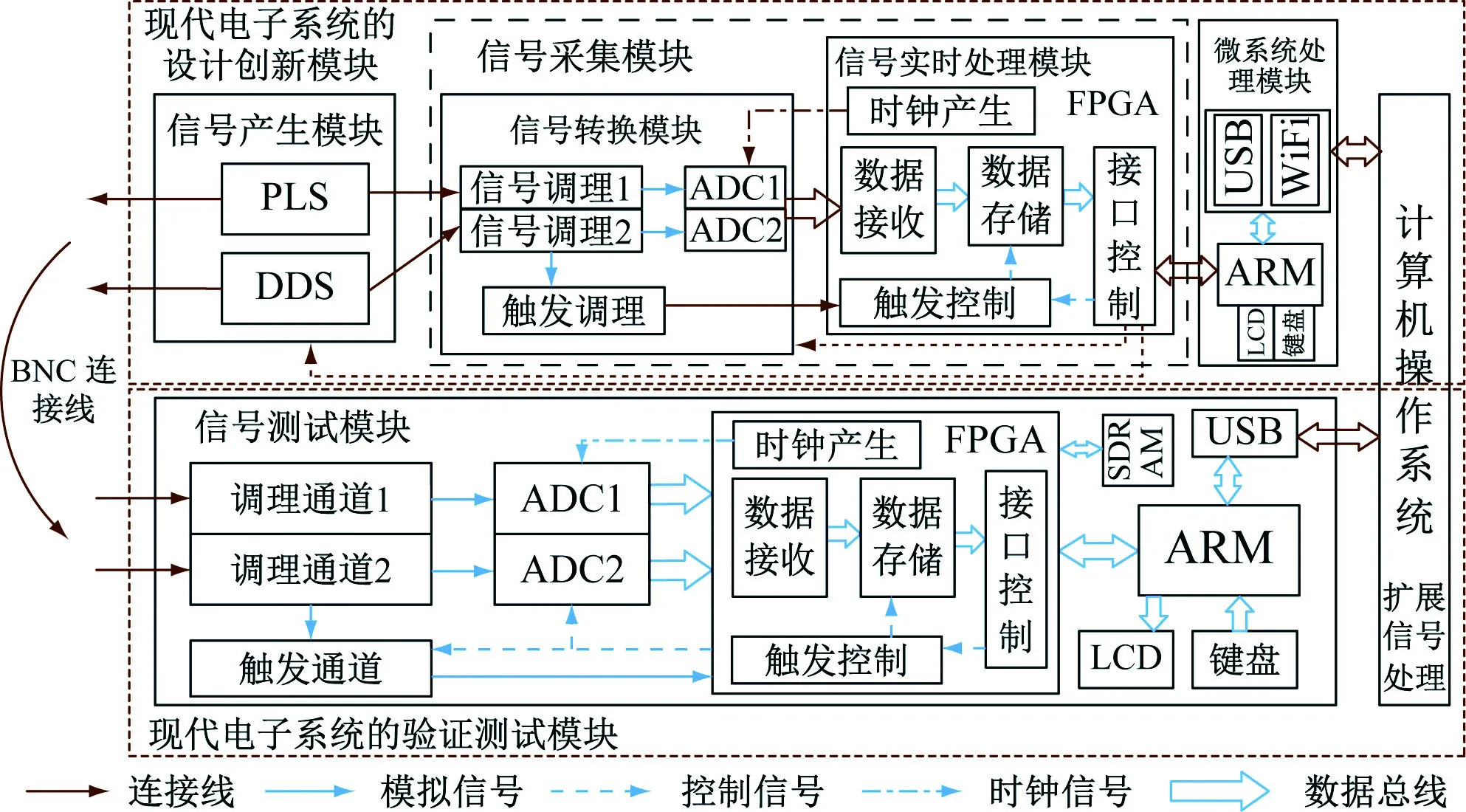

從需求可以看出,電子信息類專業所需的研究生綜合實踐平臺應能夠融合該類專業的核心理論知識進行較為復雜工程的多方位驗證、設計與創新訓練。為此,筆者借助電子測試技術教育部工程研發中心的前沿科研優勢并發揮多年與企業合作的產品研發經驗來開發了一套以工程應用創新為導向的現代電子系統綜合實踐平臺[8-9],其具體設計方案如圖1所示。

圖1 研究生綜合實踐平臺設計方案

該平臺以現代電子測試技術為核心,融合信號產生、獲取、處理、多器件(ADC、FPGA、ARM等)應用、計算機操作系統編程(Matlab、C、C++、C#、Java等語言)等多方面的電路理論、硬件設計、算法、軟件技術,可構建出一個較為綜合的電子系統設計創新實踐體系,包括現代電子系統的驗證測試(MESVT)與設計創新(MESDI)兩個功能模塊[10-12]。前者是一個相對獨立的信號獲取與處理模塊,具體包括模擬信號調理(放大、衰減、運算等)、模數轉換、時鐘產生、數據接收、數據存儲、觸發控制、數字信號處理、顯示與人機操作等功能,而且能通過USB接口將采樣獲得的數據上傳至計算機操作系統中進行擴展的數字信號處理。它具有兩個重要功能:一是用于信號獲取與處理過程中原理性的驗證,為設計創新模塊提供一個展示性的范例;二是在進行電子系統設計創新時它可以作為一臺高性能的示波器來使用,配合設計創新模塊進行信號測試來完成系統設計的調試與驗證。后者是一個由多個可擴展子模塊組成的電子設計創新系統,如信號產生、信號轉換、實時處理、微系統處理等子模塊。信號產生模塊可進行鎖相合成(PLS)和直接數字合成(DDS)兩種典型的信號產生原理驗證與用于測試所需的模擬信號輸出,具有幅度和頻率可調功能。信號轉換模塊接收待測模擬信號,完成信號衰減、放大、運算(偏置)、觸發調理和模數轉換等功能的設計與調試;信號實時處理模塊采用現場可編程邏輯門陣列(FPGA)來實現,完成采樣時鐘產生、數據接收、存儲、觸發控制等功能的設計與創新應用;微系統處理模塊由ARM控制器及其顯示、鍵盤、USB/WiFi接口組成,完成信號產生與采集過程的系統控制及其與計算機系統(Windows、Android)的數據交互功能。信號轉換、實時處理與微系統處理3個獨立模塊的聯合設計與創新應用可構成一個類似MESVT模塊的新功能。計算機系統實現器件開發環境的編程、上位機軟件開發(C#、Java)和信號處理的擴展應用(Matlab)。

該平臺摒棄了單一理論驗證或器件應用的做法,從該類專業共性的電子技術出發,更加注重實驗平臺對知識應用的系統性與創新性。為了讓學生能夠充分體驗到實踐過程,整個平臺采用模塊化設計,配合亞克力面板以全透明的方式展示實驗過程的每個環節,并在合適的地方設置對應的測試點。另外,盡可能在滿足實驗內容的前提下降低平臺價格,使得每個學生能夠擁有一個獨立的實踐平臺。綜合以上各種因素,本實驗平臺設計的主要技術指標為:① MESVT,采樣率2GSPS(MXT2001),帶寬1 GHz,通道數2個,存儲深度256 Mpts;② MESDI采集模塊,采樣率200 MS/s(MXT2088),帶寬100 MHz,通道數2個,存儲深度128 Mpts;③ MESDI的DDS,輸出頻率0.1~120 MHz,更新率2 MHz,可調幅度(峰峰值)2 V;④ MESDI的PLS,輸出頻率35~120 MHz,幅度(峰峰值)1 V。

2 課程教學設計

2.1 課程內容設計

研究生綜合實踐課程需要依據電子信息類專業公共基礎課的核心內容,以理論驗證為出發點、以工程開發訓練為主,注重創新性實驗內容設計,開展多方位的理論知識驗證和工程創新應用[3-5]。為了使得該課程具有較強的可操作性和系統性,其內容由多個獨立的小實驗來構成,每個小實驗分別由多年科研經驗的老師以濃縮工程實踐方式在MESVT和MESDI模塊中進行理論與實踐相融合的課程內容設計,包括理論分析、工程演示、開發設計、調試糾錯、應用創新5個內容,然后通過這些小實驗的訓練最終構建一個完整的信號獲取與處理系統。

具體課程內容設計實例如下:

(1) 綜合實踐平臺原理驗證實驗。熟悉平臺中信號產生、調理、采樣、存儲、處理等過程的基本原理;使用預設定好的程序(下載至MESDI 模塊中的ARM和FPGA)并調節輸出對應幅度與頻率的信號,通過連接線送至MESVT模塊中進行信號觀測;在觀測信號時,學習時基、幅度和觸發的信號調理與控制流程,體會信號獲取與處理的每個環節,學會利用電子測試儀器進行復雜信號的觀測與處理。

(2) 器件開發環境實驗。熟悉該平臺核心器件的開發軟件環境,包括FPGA開發的ISE/VIVADO和ARM開發的Keil;該實驗通過設計獨立的小功能實現來熟練掌握開發環境和編程語言(HDL和C語言)的基本應用與調試手段,例如在FPGA中利用外部時鐘產生分頻計數點亮外部LED,或者調用內部的時鐘管理器(DCM)IP核來產生特定的頻率信號并輸出至MESVT模塊進行測試,在完成這項功能控制時需要進行ARM的C語言編程;通過這些訓練,不僅要掌握工程開發工具的基本應用,而且還會利用這些工具進行舉一反三,實現較為復雜的新功能設計。

(3) 信號產生實驗。理解DDS和PLS的信號合成原理,通過對ARM和FPGA的編程來控制信號產生過程,掌握頻率控制、幅度調節(放大、衰減、濾波等)方法與過程調試;通過該實驗,學會嘗試自行設計特定頻率和幅度的信號產生模塊。

(4) 信號調理與采樣實驗。理解模擬信號放大、衰減、阻抗變換、濾波(交直流耦合、高低頻抑制)、運算(直流偏置)、模數轉換的基本原理,掌握這些信號調理和采樣過程的控制方法,達到信號觀測的幅度控制目標;學會利用這些信號調理方法嘗試進行較為復雜信號調理與采樣的設計與調試,例如較高帶寬的調理通道和較高采樣率的模數轉換方法(時間交替采樣)。

(5) 數據實時處理實驗。理解采樣時鐘產生、并行同步數據接收、預處理(抽取、峰值檢測)、小容量與大容量存儲的基本原理,掌握利用FPGA內部的資源(SERDES、DCM、SRAM、SDRAM等IP核)產生采樣時鐘、接收與存儲并行同步數據,并用HDL語言實現并行數據的預處理,達到信號觀測的時基控制目標;在實驗過程中,學會數字電路的邏輯功能、時序分析處理的調試方法,拓展現有的數據處理功能,例如實時濾波器與插值的算法設計實現。

(6) 觸發實驗。理解觸發在數據采集過程的作用與重要性,掌握模擬觸發電路調理過程(觸發源選擇、交直流耦合、高低頻抑制、遲滯比較、反相等),達到對數據存儲的控制目的;拓展數字觸發方式學習,完成利用數字觸發實現模擬觸發功能的編程訓練(HDL、C語言)與調試,如邊沿、斜率、脈寬、毛刺、高低頻抑制等觸發功能。

(7) 數據傳輸實驗。熟悉在不同控制器間的數據傳輸原理,如串口、USB、WiFi、同步總線等;設計實現FPGA與ARM間的數據傳輸、ARM與計算機之間的數據傳輸,訓練FPGA、ARM、計算機操作系統的編程(HDL、C、C++、C#/Java語言)與調試;在基本數據傳輸功能實現的基礎上,思考高效率數據傳輸方法,如FPGA與ARM之間數據傳輸加速、ARM與計算機之間數據傳輸的高效交互(多線程)。

(8) 在線控制與數據處理實驗。熟悉ARM中的采集控制與數據在線處理過程,掌握采集過程的整體控制流程、數據在線處理(濾波、頻域分析、波形參數測量、波形顯示等)的基本原理;利用C語言編程來設計實現采集控制與數據在線處理功能,并完成相應的系統調試;思考利用微處理器的有限資源和處理能力來最大化實現系統功能。

(9) 信號處理擴展應用實驗。理解數字信號處理的基本原理(濾波、頻域分析、小波變換等算法),學會利用Matlab工具進行程序開發,設計實現采樣數據的算法分析并進行相關調試,同時可以根據自己專業的特點對采樣數據作進一步擴展算法應用創新。

以上實驗課程內容僅列舉了部分較為重要的知識點實驗,在實際課程開設過程可以根據不同層次、專業和課時的具體情況對這些實驗內容和難度進行適當的增減,也可以結合特定的專業方向作一定的創新性拓展實驗或者自行設計具有新功能的電路模塊。

2.2 教學方式設計

為了適應新形勢下的高層次工程技術人才培養需求,研究生綜合實踐的教學應充分考慮理論與應用的結合,引導學生的創新意識。這就需要突破傳統課程的設計理念,創新實踐課程形式與內容,從工程需求引導、理論關聯分析、應用設計探索3個方面來構建一個綜合創新的“三位一體”的教學模式[13-14]。總的來說,就是要通過實驗,由淺入深,讓學生能夠更深地理解知識、關聯知識、應用知識,并能夠體會知識應用的創新意識。

在實施過程中,實驗教學團隊必需具備深厚的理論和實踐教學功底,而且設計實驗的教師需全程參與整個實驗的教學環節,在工程需求和理論關聯上給予必要的分析(時間占比20%),重點放在應用設計上指導學生進行規定實驗內容和調試過程(時間占比60%);之后應引導學生學以致用,舉一反三,進行開放性的拓展實驗(時間占比20%),充分激發他們的創新思維[3-5,9]。為了使得課程適用于不同專業、不同層次的學生,在課程內容和難度上需拿捏得當,可分別開設基礎性或挑戰性課程。

由于實驗過程的不確定性事件較多,所以每個老師在上課時還需配備1或2名具有較強工程經驗的高年級研究生協助進行實驗過程的指導,以確保在規定的時間內能夠完成規定的實驗內容,并有一定的拓展實驗時間。但是,由于拓展性實驗具有非常強的不確定性,所以學生做實驗的時間不僅局限于課堂上,可以在課下進行自行設計,然后在實驗室的公共開放時間進行調試驗證。

該課程的目標是培養研究生的理論與應用關聯的動手創新意識,其考核方式分為規定內容和開放內容兩部分[15]:規定內容由指導教師每次在課上檢查實驗結果,當場給予實驗操作成績,課后學生需上交總結報告,總成績根據操作成績和總結報告折算而成;開放內容由學生利用課程最后2周和課余時間完成,演示可擴展的實驗并上交實驗報告,然后指導教師根據演示和報告進行考核,折算記入實驗的總成績中。

3 教學實施

本教學團隊在研究生教育改革創新項目支持下自從2011年就著手開發基于時域測試技術的電子信息類研究生綜合實踐平臺,并于2012年開設了時域測試技術綜合實驗的全校研究生公選課,實行小班教學(60人),確保每2個研究生都有1套完整且獨立的實踐平臺,至2017年共計培養了約1440名學生。該課程入選2016年第一批“全國工程碩士專業學位研究生教育在線課程重點自建項目”目錄,適用于電子工程、控制工程、通信工程、儀器儀表工程等專業研究生的培養。為了增加實踐平臺的前沿性和創新性,在高速采集與測試技術研究生實踐平臺建設項目支持下,并結合團隊獲得的國家技術發明獎寬帶復雜信號實時捕獲與合成技術相關前沿技術成果,開發了如圖1所示的基于現代電子測試技術的研究生綜合實踐平臺。同時,該實踐平臺于2018年上半年開設了高速測試技術綜合實驗的全校研究生公選課,為了增加每個學生獨立的實驗思考空間,在實行小班教學的基礎上,把教學班分成了基礎班和挑戰班,并縮小每個教學班至30人,共計培養了約240名學生。

經調查發現,認真上過現代電子系統綜合實踐課程的同學能夠在工程開發和調試上得到較為充分的鍛煉。雖然他們在上課階段需要多花些心思,但在進入教研室后能夠在較短時間內適應較為繁瑣的科研節奏,能夠調試并解決工程開發過程中出現的問題,顯著地提升了科研實踐能力。這可以有效地縮短了研究生進入科研狀態的煎熬期,在一定程度上解決了動手能力培養的老大難問題。這也使得電子信息類研究生在有限的培養期內能夠更加注重自己專業方向的鍛煉,發揮專業創新意識。同時,這些研究生在就業時能夠更加受到用人單位的賞識,普遍能夠找到較好的工作崗位。

4 結 語

綜上所述,電子信息類研究生綜合實踐平臺綜合了電子信息大類專業的共性技術,能夠突破專業局限,通過理論與工程相結合的課程設計與教學方式的創新,多方位培養研究生的知識綜合應用及解決實際問題的能力,使得學生的工程創新意識能夠得到充分的激發。