基于雙環(huán)系統(tǒng)的細(xì)步進(jìn)頻率合成器

沈文淵,唐光慶,楊清福,穆曉華,李慶洪,蔣創(chuàng)新

(1. 中國(guó)電子科技集團(tuán)公司第二十六研究所,重慶400060;2. 空軍裝備部駐重慶地區(qū)軍事代表室,重慶400060)

0 引言

頻率合成器是雷達(dá)、通信、導(dǎo)航、電子對(duì)抗等電子系統(tǒng)的核心部件,其作用是利用高穩(wěn)的參考信號(hào)作為基準(zhǔn),通過(guò)一系列的倍頻、分頻和混頻等變頻處理產(chǎn)生電子系統(tǒng)所需特定射頻信號(hào)。頻率綜合器的頻率帶寬、跳頻步進(jìn)、相位噪聲及雜散抑制等指標(biāo)直接影響電子系統(tǒng)的功能和性能。現(xiàn)代軍事電子系統(tǒng)對(duì)頻率綜合器的綜合性能提出了越來(lái)越高的要求,寬頻帶、細(xì)步進(jìn)、低相噪、低雜散、低功耗和小型化成為頻率合成器的主要發(fā)展趨勢(shì)。鎖相頻率合成因具有寬頻帶、低功耗及易于程控等優(yōu)勢(shì)而廣泛應(yīng)用于現(xiàn)代軍用電子系統(tǒng)中[1-4]。

本文研究并設(shè)計(jì)了一種雙環(huán)級(jí)聯(lián)的鎖相頻率合成器,實(shí)現(xiàn)了寬帶、細(xì)步進(jìn)和低雜散的指標(biāo)要求。該方案中,第一級(jí)鎖相環(huán)采用HITTITE的集成鎖相環(huán)芯片HMC830產(chǎn)生頻率fref作為第二級(jí)鎖相環(huán)的參考輸入,第二級(jí)鎖相環(huán)采用ADF41513+HMC586通過(guò)小數(shù)分頻鎖相最終產(chǎn)生4~8 GHz寬帶頻率信號(hào)輸出,頻率步進(jìn)1 kHz。通過(guò)優(yōu)化fref的值來(lái)消除小數(shù)分頻鎖相所帶來(lái)的雜散問(wèn)題,實(shí)現(xiàn)全頻段范圍內(nèi)雜散指標(biāo)優(yōu)于75 dBc。

1 細(xì)步進(jìn)鎖相的原理

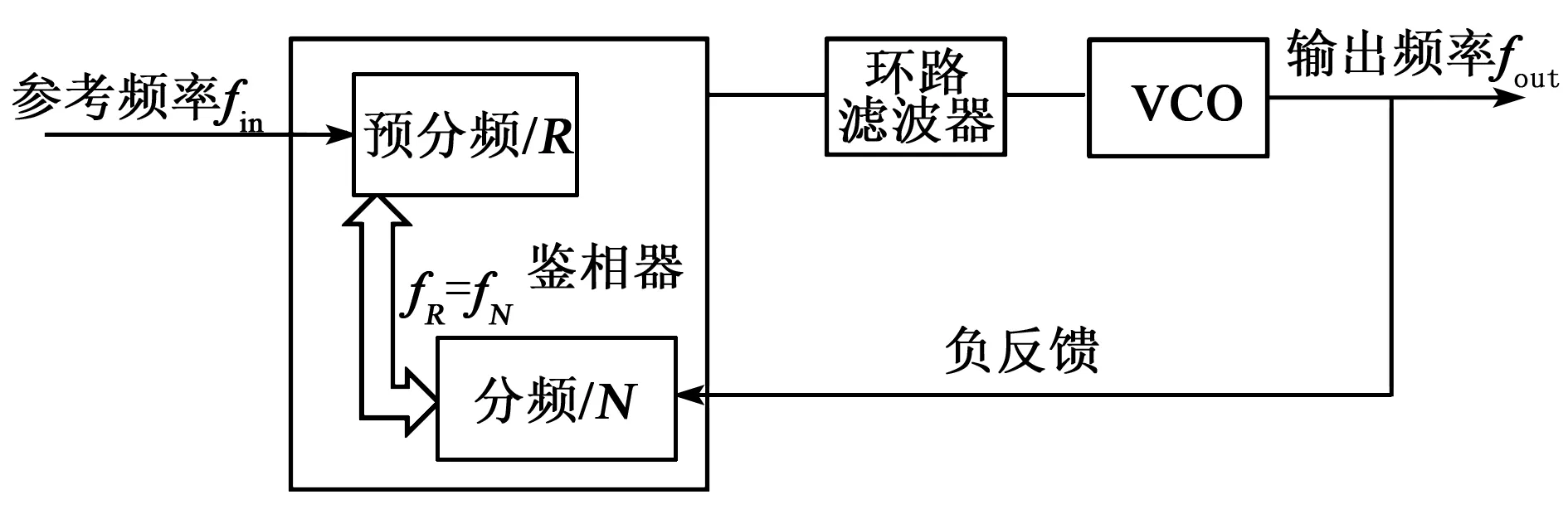

鎖相頻率合成作為一種間接頻率合成法廣泛應(yīng)用于通信和雷達(dá)領(lǐng)域,經(jīng)典的鎖相環(huán)(PLL)系統(tǒng)由鑒相器(PD)、環(huán)路濾波器(LF)和壓控振蕩器(VCO)構(gòu)成,如圖1所示。

圖1 鎖相環(huán)結(jié)構(gòu)原理圖

PLL通過(guò)負(fù)反饋的相位控制系統(tǒng)進(jìn)行輸入?yún)⒖夹盘?hào)與VCO輸出反饋信號(hào)進(jìn)行相位比較,然后通過(guò)鑒相器給出誤差電壓或電流經(jīng)環(huán)路濾波器濾波處理后,產(chǎn)生一個(gè)穩(wěn)定電壓來(lái)控制VCO的頻率輸出fout。當(dāng)負(fù)反饋環(huán)路穩(wěn)定而進(jìn)入鎖定狀態(tài)后,VCO輸出頻率與參考頻率完全同步。目前,主流的數(shù)字鑒相器集成了參考輸入的預(yù)分頻數(shù)R和反饋輸入的N分頻,通過(guò)數(shù)字程控R和N的取值而實(shí)現(xiàn)PLL輸出頻率fout的變化,即

(1)

式中:fref=fin/R為鑒相頻率;fin為參考頻率。

因此,鎖相頻率合成方式通過(guò)選擇寬帶VCO器件,并控制數(shù)字鑒相器R和N的取值,易實(shí)現(xiàn)寬帶的頻率合成輸出。

PLL根據(jù)分頻N值的不同可分為整數(shù)分頻鎖相和小數(shù)分頻鎖相兩大類。整數(shù)分頻的N取值為整數(shù),此時(shí)VCO輸出的鎖定頻率為fref的整數(shù)倍。一般fref越小,環(huán)路濾波器對(duì)鑒相泄露雜散抑制能力越弱。fref≥1 MHz時(shí),通過(guò)環(huán)路濾波器仿真調(diào)試及特殊頻點(diǎn)陷波處理,可實(shí)現(xiàn)70 dBc左右的鑒相泄露抑制。如果鑒相頻率再減小,鑒相泄露雜散很難滿足工程應(yīng)用中對(duì)雜散指標(biāo)的要求。因此,一般整數(shù)分頻的fref≥1 MHz,即頻率步進(jìn)不小于1 MHz。

小數(shù)分頻鎖相即N取值為小數(shù),設(shè)N值分為整數(shù)部分Nint和小數(shù)部分Nfrac之和,即

N=Nint+Nfrac

(2)

此時(shí)VCO輸出鎖定頻率為

fout=fref×Nint+fref×Nfrac

(3)

Nfrac的取值與鑒相器的小數(shù)分頻位數(shù)相關(guān)。目前市面上主流的小數(shù)分頻鑒相器如ADI公司的ADF41513,HMC704,以及國(guó)產(chǎn)振芯電子的GM4704等芯片均可達(dá)24位,換算過(guò)來(lái)即小數(shù)分頻的精度小于1 Hz。因此,理論上小數(shù)分頻可實(shí)現(xiàn)VCO頻率范圍內(nèi)的任意細(xì)步進(jìn)頻率輸出[5-6]。

2 小數(shù)分頻雜散分析及雙環(huán)鎖相方案

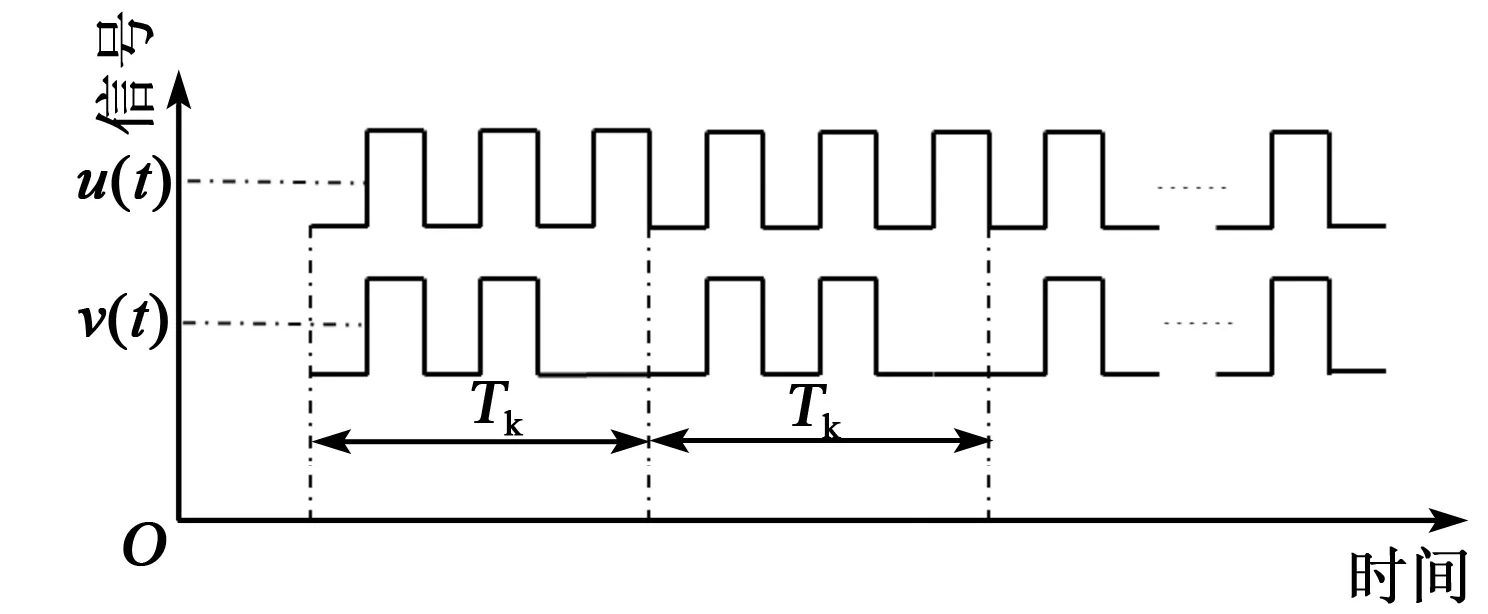

小數(shù)分頻鎖相是基于脈沖移除技術(shù)實(shí)現(xiàn)的。假設(shè)一個(gè)頻率為fk的信號(hào)u(t)每隔Tk的時(shí)間移除F個(gè)周期,則輸出信號(hào)v(t)每Tk時(shí)間就會(huì)輸出fk×Tk-F個(gè)脈沖,即fout=fk-F/Tk。因此,通過(guò)改變F和Tk可實(shí)現(xiàn)小數(shù)分頻。這里Tk可通過(guò)對(duì)fref的A分頻得到,當(dāng)信號(hào)鎖定時(shí),鑒相器預(yù)分頻后輸入與輸出頻率相等,即

fref=(fout-F/Tk)/Nint

(4)

(5)

式中A=Tk/fref。圖2為脈沖移除原理。

圖2 脈沖移除原理

通過(guò)小數(shù)分頻的原理可發(fā)現(xiàn),小數(shù)分頻鎖相可解決整數(shù)分頻方式由于fref不能無(wú)限制減小而造成頻率步進(jìn)較大的問(wèn)題,即解決了高頻分辨率和fref間的矛盾。

小數(shù)分頻鎖相輸出頻率由整數(shù)部分和小數(shù)部分組成,也因此帶來(lái)了PLL整數(shù)邊界雜散(Nint×fref)和小數(shù)雜散(1×fref/Nfrac,2×fref/Nfrac,…)問(wèn)題,整數(shù)邊界雜散和小數(shù)雜散離中心頻率很近,很難通過(guò)外部環(huán)路濾波器濾出,嚴(yán)重情況近端小數(shù)雜散僅比輸出主頻率信號(hào)電平低10~20 dB,嚴(yán)重影響通信系統(tǒng)的整體性能,直接限制了其在工程中的應(yīng)用。因此,針對(duì)小數(shù)分頻雜散問(wèn)題需要新的技術(shù)加以解決。

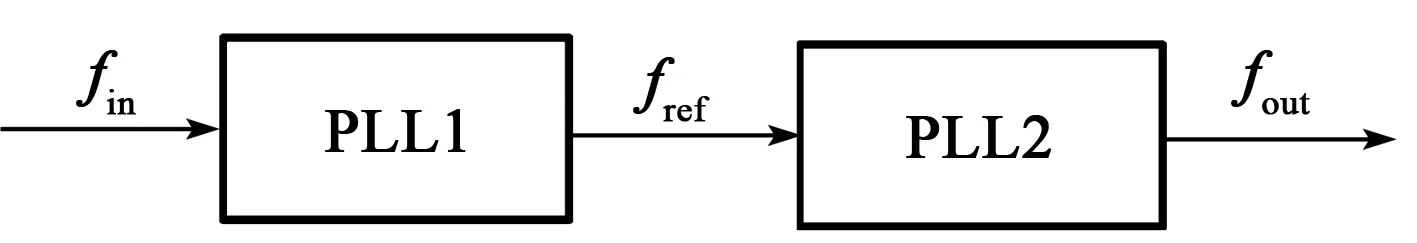

對(duì)于小數(shù)雜散問(wèn)題可通過(guò)∑-Δ調(diào)制技術(shù)來(lái)解決[7-9],該技術(shù)通過(guò)對(duì)雜散進(jìn)行整形,將雜散從低頻段推到高頻段,進(jìn)而通過(guò)環(huán)路濾波器進(jìn)行濾出。目前主流的小數(shù)分頻鑒相器均集成了∑-Δ調(diào)制技術(shù)。因此,可較好地解決小數(shù)分頻帶來(lái)的小數(shù)雜散問(wèn)題,但對(duì)于整數(shù)邊界雜散∑-Δ調(diào)制技術(shù)無(wú)法有效解決。目前解決方法大多采用數(shù)字頻率合成器(DDS)作為參考源,用作小數(shù)分頻鎖相環(huán)fref的參考輸入[10],通過(guò)DDS改變小數(shù)分頻鎖相環(huán)輸入fref,從而避開較近的整數(shù)邊界雜散點(diǎn),由于較遠(yuǎn)處雜散可通過(guò)環(huán)路濾波器濾除,因此,最終達(dá)到消除整數(shù)邊界雜散的目的。一種典型的DDS參考鎖相原理框圖如圖3所示。

圖3 傳統(tǒng)DDS+PLL方案

圖3方案可解決小數(shù)分頻鎖相的雜散問(wèn)題,但由于DDS也需參考頻率fDDS輸入,因此,還需增加額外的DDS參考產(chǎn)生電路,通常采用梳譜倍頻濾波或單環(huán)鎖相實(shí)現(xiàn),該方式在成本、體積和功耗方面均需增加較大的額外開銷。由于寬帶細(xì)步進(jìn)的小數(shù)分頻頻點(diǎn)數(shù)量大, DDS控制程序較復(fù)雜,也增加了較大的軟件開銷。因此,本文設(shè)計(jì)了一種低成本、低功耗的雙環(huán)鎖相系統(tǒng),該系統(tǒng)設(shè)計(jì)思路是采用一級(jí)鎖相環(huán)來(lái)代替DDS實(shí)現(xiàn)變參考的目的。該方案實(shí)現(xiàn)框圖如圖4所示。第一級(jí)PLL(PLL1)采用整數(shù)分頻方式實(shí)現(xiàn)變參考,第二級(jí)PLL(PLL2)采用小數(shù)分頻實(shí)現(xiàn)細(xì)步進(jìn)。通過(guò)改變PLL1的輸出頻率,進(jìn)而實(shí)現(xiàn)第二級(jí)小數(shù)分頻鎖相環(huán)的變參考目的,最終實(shí)現(xiàn)第二級(jí)小數(shù)分頻鎖相環(huán)的整數(shù)邊界雜散的優(yōu)化。與圖3相比,該方案可節(jié)省一半以上的空間體積和功耗,實(shí)現(xiàn)了小型化的寬帶細(xì)步進(jìn)頻率合成。

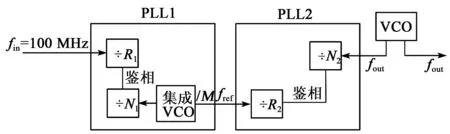

圖4 雙環(huán)細(xì)步進(jìn)鎖相方案

3 雙環(huán)細(xì)步進(jìn)頻率合成器設(shè)計(jì)

首先根據(jù)工程實(shí)用的需求提出如下雙環(huán)細(xì)步進(jìn)頻率合成器擬達(dá)到的技術(shù)指標(biāo)要求:輸入?yún)⒖夹盘?hào)頻率為100 MHz;輸出頻率為4~8 GHz;輸出頻率步進(jìn)為1 kHz;相位噪聲≤-95 dBc/Hz@1 kHz;雜波抑制≥70 dBc;跳頻時(shí)間≤50 μs。

3.1 硬件方案設(shè)計(jì)

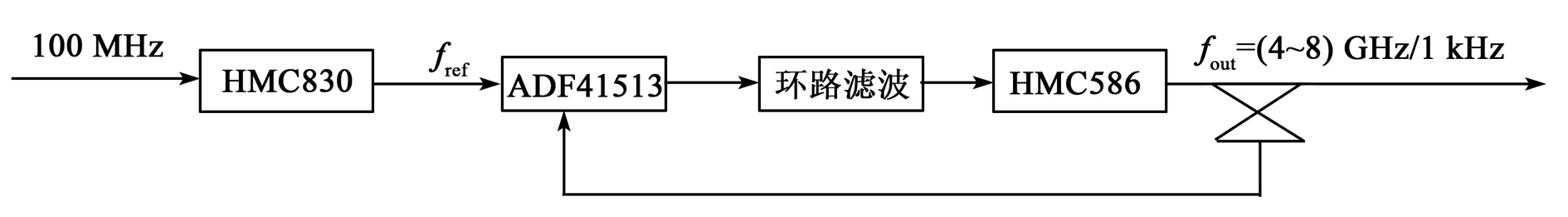

雙環(huán)系統(tǒng)的細(xì)步進(jìn)頻率合成器采用一級(jí)整數(shù)分頻鎖相環(huán)(PLL1)和一級(jí)小數(shù)分頻鎖相環(huán)(PLL2)級(jí)聯(lián)實(shí)現(xiàn)。PLL1采用HITTITE公司的HMC830集成VCO鎖相芯片,該芯片的歸一化噪聲基底為-227 dBc/Hz,輸出頻率覆蓋25~3 000 MHz,芯片封裝尺寸為6 mm×6 mm,通過(guò)該集成芯片可實(shí)現(xiàn)設(shè)計(jì)的小型化。第二級(jí)小數(shù)分頻鎖相環(huán)芯片采用ADI公司的ADF41513鑒相器及HITTITE的HMC586型VCO芯片。ADF41513型鑒相器反饋頻率最高可到26.5 GHz,歸一化噪聲基底優(yōu)于-234 dBc/Hz。具體設(shè)計(jì)方案如圖5所示。圖6為鑒相器內(nèi)部分頻比設(shè)置示意圖。

圖5 細(xì)步進(jìn)雙環(huán)鎖相設(shè)計(jì)框圖

圖6 雙環(huán)鎖相分頻比設(shè)置示意圖

雙環(huán)系統(tǒng)最終輸出頻率與兩級(jí)鑒相器的R分頻和N分頻均有關(guān),即

(6)

式中:fin=100 MHz;N1/R1為第一級(jí)整數(shù)分頻鎖相環(huán)分頻比;M為HMC830的VCO輸出的分頻數(shù);N2/R2為第二級(jí)小數(shù)分頻鎖相環(huán)的分頻比,其中N2為小數(shù)。

在實(shí)際設(shè)計(jì)中,固定R1和R2不變,雙環(huán)系統(tǒng)輸出最終頻率確定的情況下,給出一個(gè)N1/M值,則可計(jì)算出N2。即通過(guò)改變N1和M值,可實(shí)現(xiàn)小數(shù)分頻鎖相環(huán)fref的改變,實(shí)現(xiàn)不同fout對(duì)應(yīng)參考信號(hào)fref的調(diào)整,進(jìn)而實(shí)現(xiàn)消除整數(shù)邊帶雜散的目的。該雙環(huán)頻率合成系統(tǒng)硬件電路實(shí)現(xiàn)簡(jiǎn)單,以最低的成本和功耗實(shí)現(xiàn)變參考,從而解決小數(shù)分頻整數(shù)邊帶雜散的問(wèn)題。

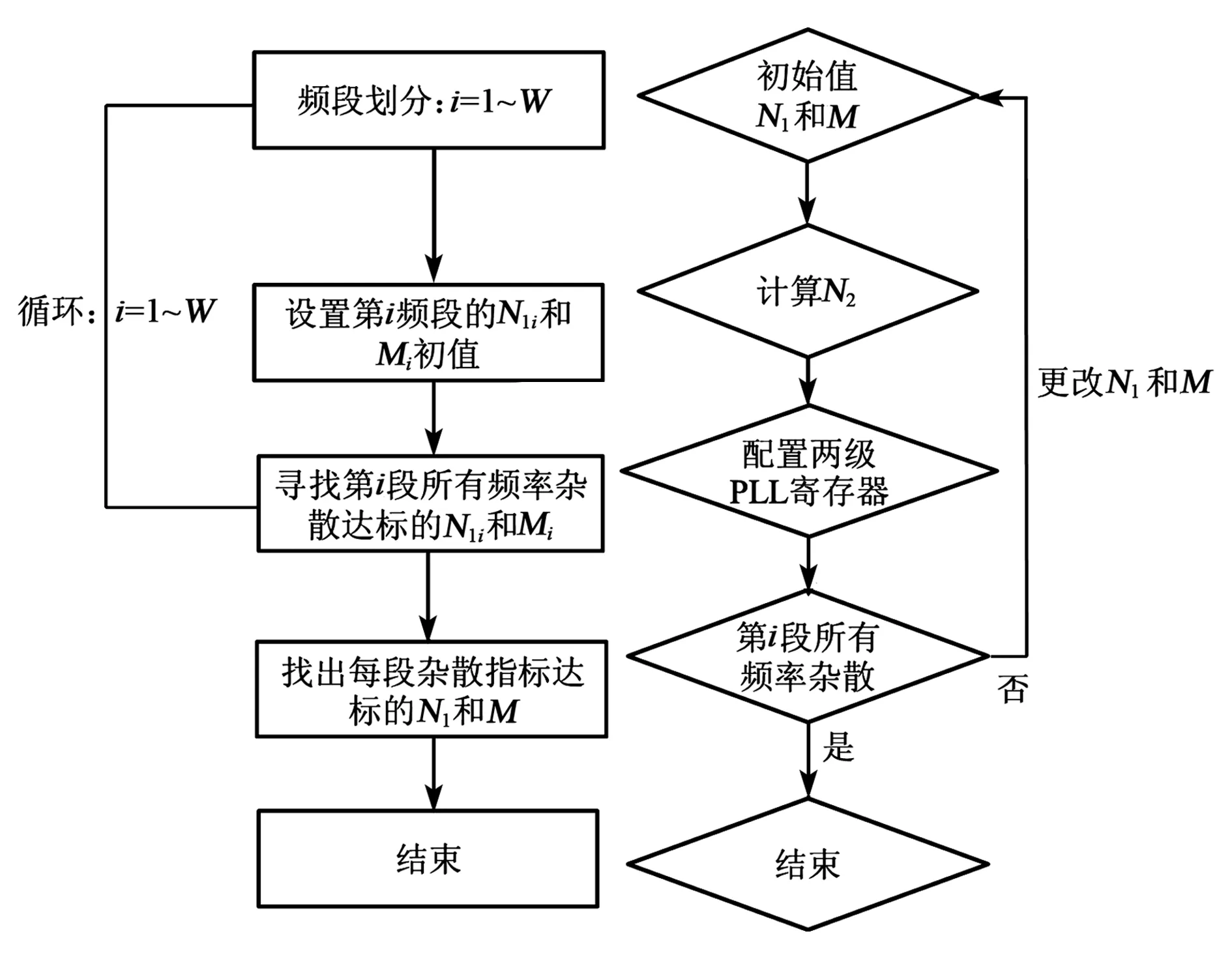

3.2 軟件方案設(shè)計(jì)

基于雙環(huán)系統(tǒng)的細(xì)步進(jìn)頻率合成器的軟件部分設(shè)計(jì)重點(diǎn)在于:通過(guò)N1/R1選擇來(lái)避開第二級(jí)PLL小數(shù)分頻所帶來(lái)的整數(shù)邊帶雜散。本方案控制部分采用現(xiàn)場(chǎng)可編程門陣列(FPGA)硬件,基于硬件描述語(yǔ)言最終實(shí)現(xiàn)。

首先對(duì)全頻段4~8 GHz進(jìn)行分段處理,假設(shè)總共分段數(shù)為W段,每段頻率帶寬Δf=4 000/W(MHz)。每段內(nèi)采用相同的N1/M值,通過(guò)給定的N1和M計(jì)算對(duì)應(yīng)輸出頻率的N2值。這里設(shè)第一個(gè)輸出頻點(diǎn)值為4 000 MHz,第二個(gè)頻率點(diǎn)為4 000 MHz+1 kHz,依次類推,那么第k個(gè)頻點(diǎn)對(duì)應(yīng)頻率值為

fk=4 000 MHz+(k-1)×1 kHz

(7)

第k個(gè)頻點(diǎn)對(duì)應(yīng)的頻段數(shù)i(1≤i≤W)可表示為

(8)

式中INT表示取整。

第k個(gè)頻點(diǎn)對(duì)應(yīng)輸出頻率值的N2值為

(9)

根據(jù)計(jì)算的N2值,通過(guò)FPGA對(duì)2個(gè)PLL的R1、N1和R2、N2寄存器進(jìn)行配置,然后測(cè)試輸出最終頻率的雜散,如果雜散指標(biāo)不滿足要求,則調(diào)整N1和M值直至滿足,通過(guò)這種方式找出所有頻段雜散滿足指標(biāo)的N1和M值。圖7為算法示意圖。表1為優(yōu)化后的輸出前6段頻率對(duì)應(yīng)取值表。

圖7 雙環(huán)鎖相軟件設(shè)計(jì)流程圖

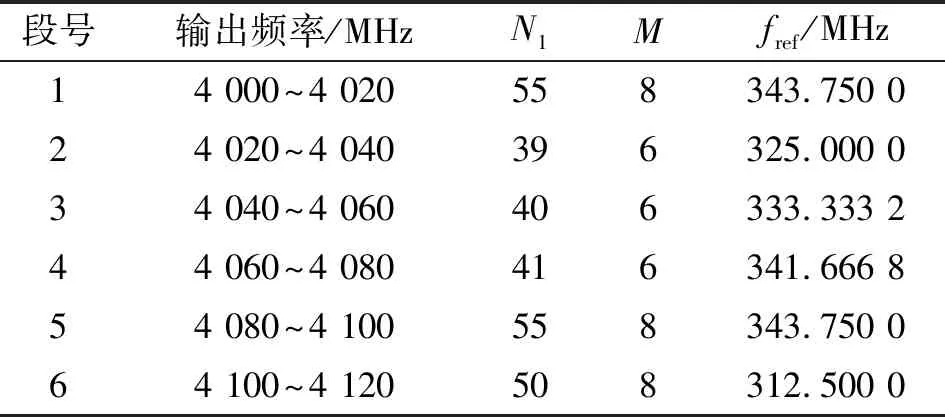

表1 1~6段優(yōu)化后的N1、M及fref

4 雙環(huán)系統(tǒng)的細(xì)步進(jìn)頻率合成器性能分析

按照前文所述設(shè)計(jì)方案對(duì)雙環(huán)系統(tǒng)的細(xì)步進(jìn)頻率合成器進(jìn)行電路和結(jié)構(gòu)設(shè)計(jì),加工實(shí)物如圖8所示,產(chǎn)品總尺寸為40 mm×40 mm×10 mm,該體積中包含了兩級(jí)鎖相環(huán)硬件電路、+12 V電源處理電路和FPGA控制電路,頻率合成器總功耗為2.6 W。

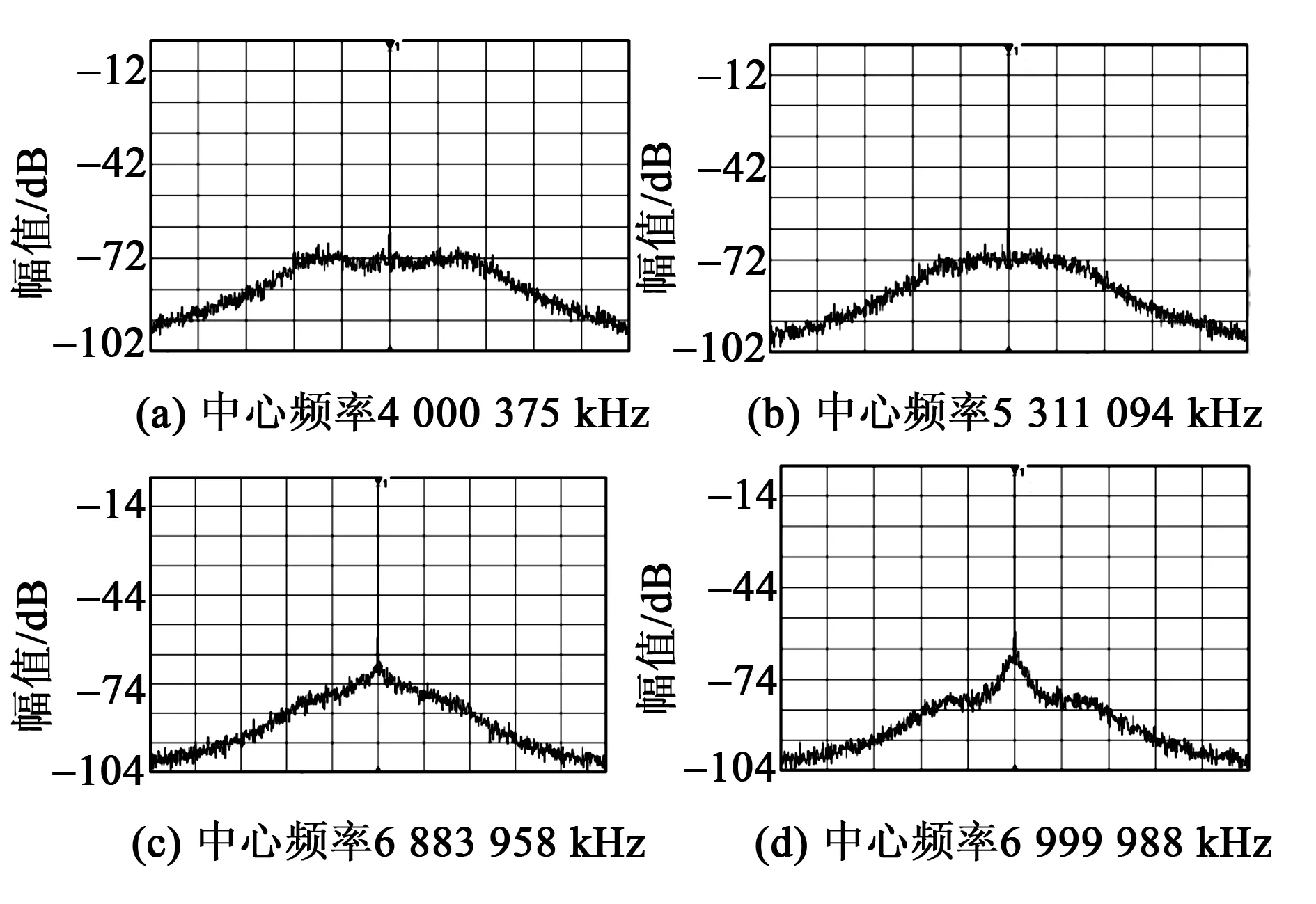

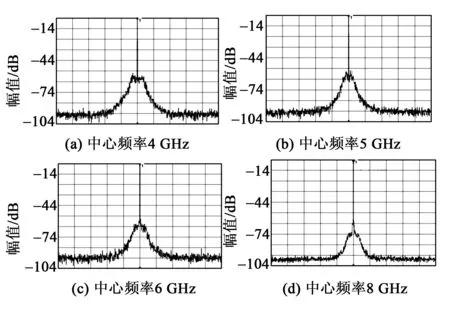

圖9、10分別為工作頻帶內(nèi)任選4個(gè)頻點(diǎn):4 000 375 kHz,5 311 094 kHz,6 883 958 kHz和7 999 988 kHz的頻譜圖。圖9中頻譜儀分辨率帶寬設(shè)為5 MHz,圖10中頻譜儀頻寬設(shè)為20 MHz。由圖9、10可看出,所測(cè)試頻率雜散均優(yōu)于75 dBc。

圖9 分辨率帶寬為5 MHz頻譜測(cè)試圖

圖10 分辨率帶寬為20 MHz頻譜測(cè)試圖

圖11為中心頻率不同、頻寬100 MHz時(shí)的頻譜測(cè)試圖。綜合圖9~11可知,本文提出的雙環(huán)系統(tǒng)細(xì)步進(jìn)鎖相方案可消除小數(shù)分頻鎖相所帶來(lái)的整數(shù)邊帶雜散,實(shí)現(xiàn)了寬帶、細(xì)步進(jìn)合高雜散抑制的頻率合成輸出。

圖11 分辨率帶寬為100 MHz頻譜測(cè)試圖

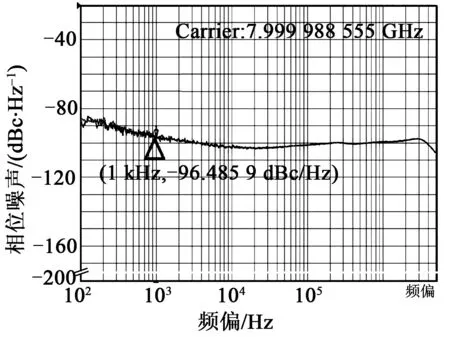

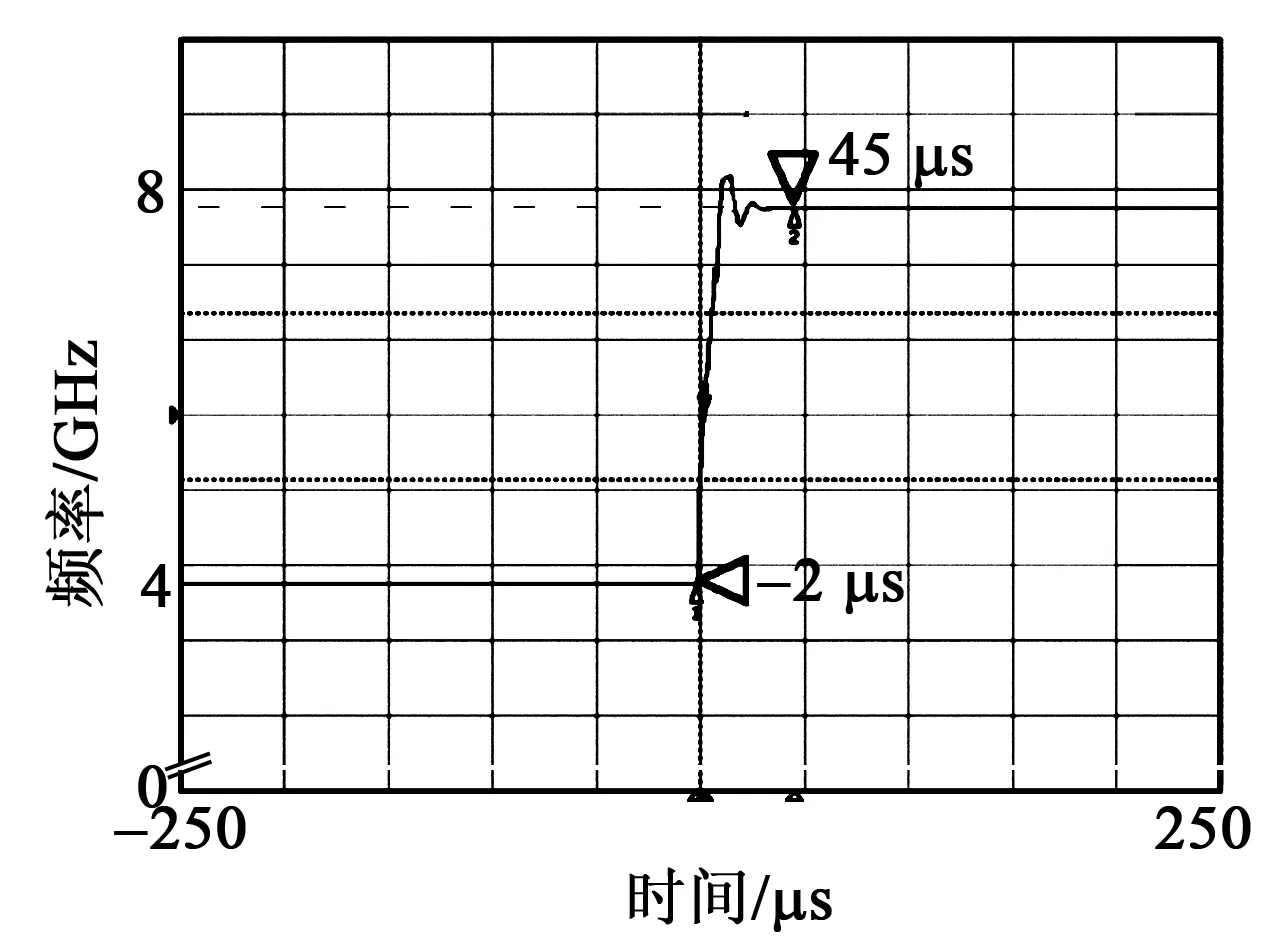

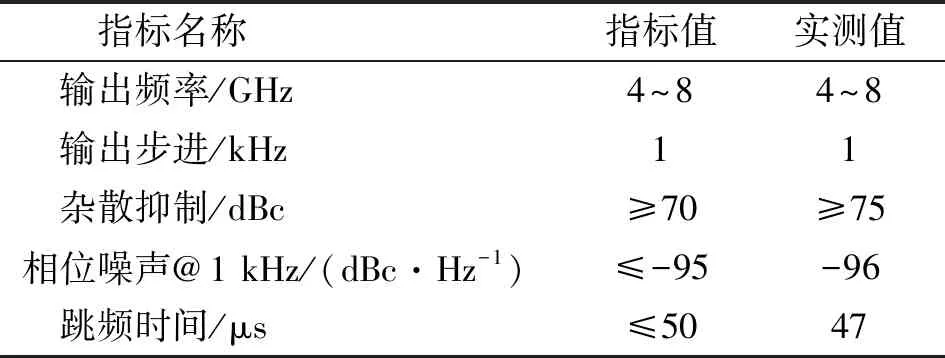

圖12、13分別為該頻率合成器的相位噪聲和跳頻時(shí)間實(shí)測(cè)結(jié)果。由圖12、13可看出,頻率合成器相位噪聲優(yōu)于-96 dBc/Hz@1 kHz, 跳頻時(shí)間小于47 μs;實(shí)測(cè)指標(biāo)與擬達(dá)到對(duì)比如表2所示。由表可知,所有指標(biāo)均達(dá)到預(yù)期值。

圖12 輸出頻率8 GHz時(shí)相位噪聲測(cè)試曲線

圖13 輸出頻率4~8 GHz間跳頻時(shí)間測(cè)試圖

表2 頻率綜合器擬達(dá)到指標(biāo)與實(shí)測(cè)指標(biāo)對(duì)比

5 結(jié)束語(yǔ)

本文介紹了一種基于雙環(huán)系統(tǒng)的寬帶細(xì)步進(jìn)頻率合成方法,該方法采用兩級(jí)級(jí)聯(lián)鎖相環(huán)的方式,解決了在細(xì)步進(jìn)的情況下小數(shù)分頻鎖相所帶來(lái)的整數(shù)邊帶雜散問(wèn)題。根據(jù)該方法設(shè)計(jì)的頻率合成器模塊實(shí)測(cè)結(jié)果表明,4~8 GHz全頻段范圍內(nèi)雜散抑制可達(dá)75 dBc,相位噪聲優(yōu)于-96 dBc/Hz@1 kHz,跳頻時(shí)間小于47 μs,滿足系統(tǒng)對(duì)頻率合成信號(hào)高質(zhì)量的要求。此外,該方案還具有小型化、低成本、低功耗、設(shè)計(jì)簡(jiǎn)單等優(yōu)點(diǎn)。通過(guò)該方案易對(duì)輸出頻率范圍進(jìn)行拓展,具有極高的實(shí)用價(jià)值和較好的應(yīng)用前景。