一種雷達信號處理機程序切換方法

周威威, 陶 翠, 金埡梅, 李宇翔, 李夢妍

(上海無線電設備研究所,上海201109)

0 引言

近年來,得益于性能的快速提升,雷達在國防[1]、交通[2]、測繪、汽車、無人機[3]等領域的應用越來越廣泛。雷達信號處理機作為雷達系統的重要組成部分,是雷達算法的運行平臺和硬件基礎,主要負責采樣數據的處理與分析。FPGA+DSP是現代雷達信號處理機的主流架構,FPGA和DSP程序的調試和燒寫主要通過延伸到單板外的JTAG總線。

日益惡劣的工作環境和更高的性能要求,使得雷達信號處理機的數據處理、搜索、識別、跟蹤算法越來越復雜[4]。與人工智能等新型算法的融合,進一步增加了處理機算法架構的復雜性和多樣性[5]。雷達系統測試時通常需要對比多種算法,從中篩選出綜合性能最優的方案。為實現高可靠性,雷達系統需要在整機狀態下充分測試[6]。一方面,現有雷達信號處理機JTAG總線燒寫速度慢、誤碼率高、抗干擾能力差,通常只延伸到單板外,因此整機狀態下不能通過重燒程序來切換算法,只能通過遠程通信更改部分參數;另一方面,高擬真度仿真環境和極端測試環境搭建困難,可供測試的時間有限。另外,可定制化要求雷達整機能夠根據部署環境和部署策略快速切換算法程序。綜上所述,雷達整機測試、驗證和部署都需要處理機能夠進行多程序遠程快速切換,以便在盡可能短的時間內充分驗證多種程序方案和進行定制化部署。

1 處理機硬件設計

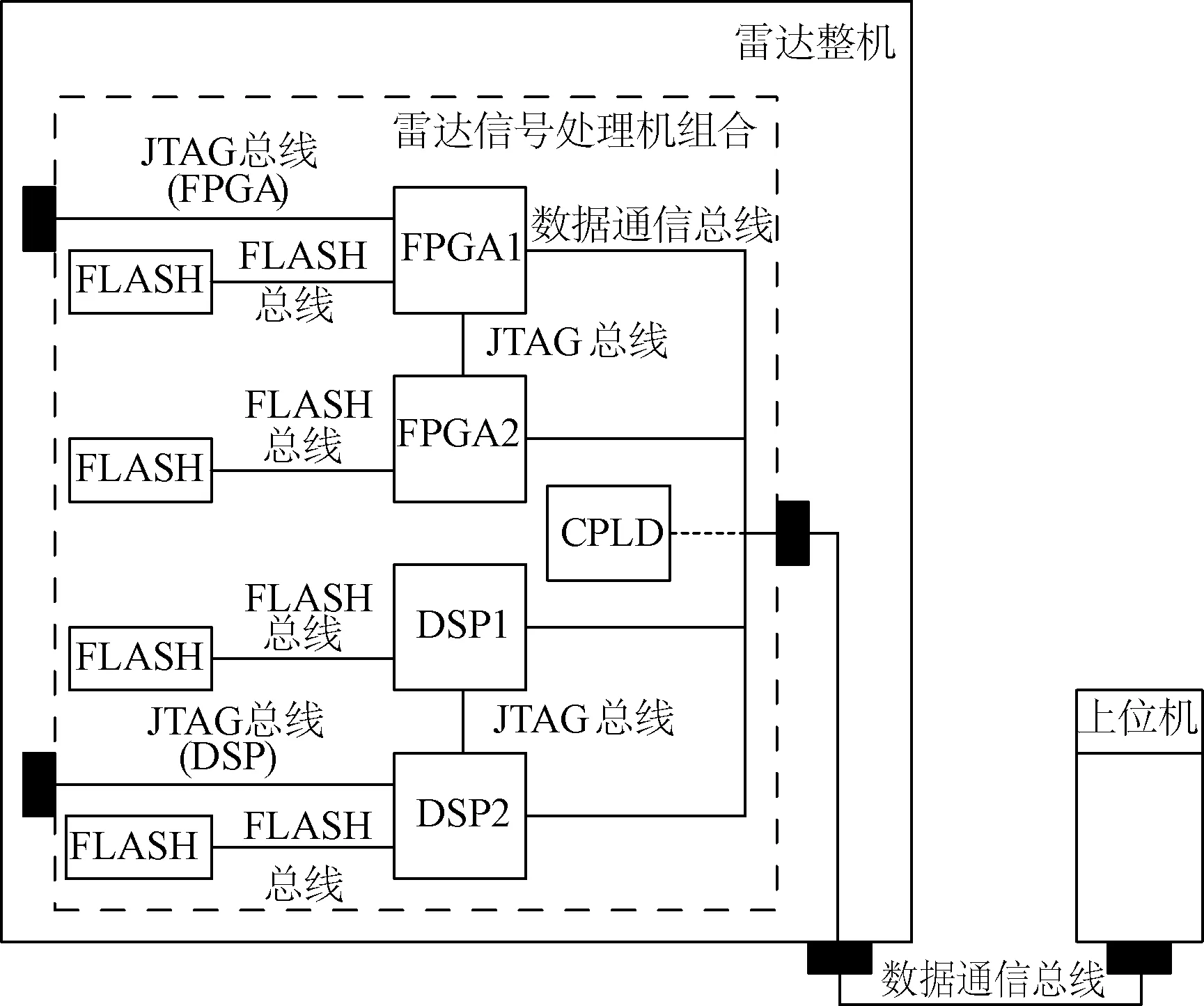

常見的雷達信號處理機組成框圖如圖1所示。其中:兩片FPGA芯片用于模數轉換芯片、時鐘芯片和交換芯片等外圍器件的驅動控制,數字信號預處理,算法加速和接口控制等;兩片DSP芯片用于大規模數據運算和復雜算法順序執行等;一片CPLD控制板上電源芯片,在上電時滿足各FPGA和DSP芯片的啟動時序要求。每片FPGA或DSP芯片分別通過FLASH總線與一片FLASH芯片相連。上電后,FPGA和DSP芯片自動讀取加載保存在各自FLASH芯片中的程序,完成處理機啟動。

圖1 雷達信號處理機框圖

兩片FPGA芯片通過JTAG總線串聯后連接至單板外部接插件,用于單板狀態下的FPGA程序在線調試和燒寫。兩片DSP芯片也采取同樣的連接方式。所有FPGA與DSP芯片均接入數據通信總線,總線連接外部測試設備上位機(CPLD芯片不接入總線)。數據通信總線用于雷達整機狀態下各單板芯片間數據交互,也用于上位機傳輸測試命令與測試數據、監控測試狀態。常用的數據通信總線包括1553B、SRIO、CAN、RS422等。

目前,雷達信號處理機中的DSP和FPGA芯片對應的配置FLASH中只燒寫一個程序,與其他單板一起裝入雷達整機進行測試。測試中處理機各芯片加載程序不能修改更換,若要更換只能拆開整機,取出處理機單板,用仿真器通過JTAG接口燒寫新程序后重新裝回整機。隨著技術的發展,在雷達整機狀態下快速進行處理機程序遠程切換的需求越來越迫切。雖然FPGA部分可重構和DSP參數遠程更新技術可以在一定程度上緩解需求,但也會帶來新的問題:片上資源浪費,實現難度大,不能整個程序切換等。

為實現雷達信號處理機多程序遠程快速切換,對處理機硬件進行設計改進。如圖1虛線所示,將CPLD芯片接入數據通信總線,使得CPLD能夠接收上位機發出的控制信號,通過CPLD配合上位機復位重啟FPGA與DSP芯片,實現程序切換功能。

2 多程序切換策略

由于FPGA芯片和DSP芯片具有不同的程序加載方式,因此需要對其采用不同的程序切換策略。

2.1 FPGA多程序切換

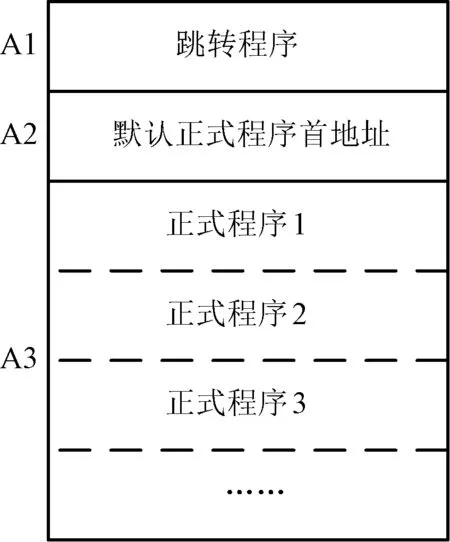

圖2 FPGA的FLASH芯片存儲區域劃分

FLASH存儲空間共分為三個區域:A1跳轉程序存儲區,A2默認正式程序首地址存儲區,A3正式程序存儲區。A1區域從地址0x0開始,存儲FPGA跳轉程序,FPGA上電或復位重啟后自動加載此程序與上位機通信,確定要加載的正式程序首地址后進行跳轉。A2區域中存儲默認正式程序的首地址,用作跳轉程序在沒有從上位機接收到有效的跳轉地址時加載默認正式程序。A3區域中保存有多個完整的FPGA正式程序,跳轉程序執行后會從此存儲區中選擇一個正式程序進行跳轉。在ISE i MPACT工具或Vivado中將多個FPGA工程文件(.bit)和數據文件合成為FLASH燒寫文件(.mcs),通過FPGA的JTAG接口燒入FLASH中。

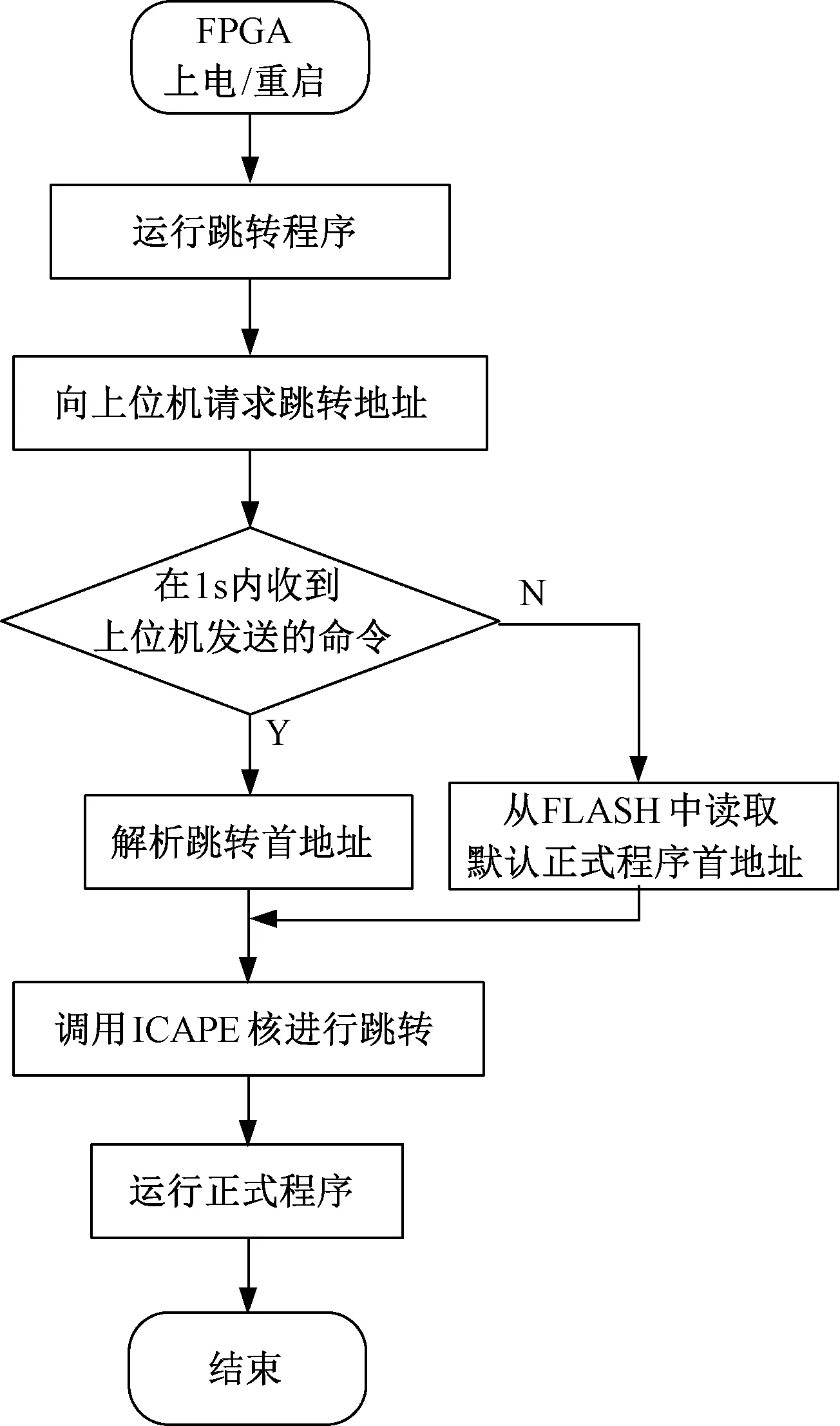

雷達信號處理機FPGA芯片多程序遠程快速切換流程如圖3所示。在FPGA上電或被CPLD重啟后,首先加載運行跳轉程序,通過RS422等數據通信總線向上位機請求跳轉地址。如果在1 s內收到有效的跳轉命令,則解析出跳轉地址,否則從FLASH中讀取默認正式程序首地址作為跳轉地址。確定跳轉地址后,FPGA將調用ICAPE核進行指定首地址的程序跳轉,并自動重啟,從該地址加載運行正式程序,完成程序切換。

圖3 FPGA多程序遠程快速切換流程圖

2.2 DSP多程序切換

DSP的FLASH芯片存儲空間分為三個存儲區域,如圖4所示。A1區域中存儲DSP芯片的二次加載引導程序bootloader,用于DSP啟動后C語言運行環境搭建,通信接口初始化,與上位機通信選擇要加載正式程序的首地址,從FLASH中讀取正式程序加載進內核等。A2區域中存儲DSP默認正式程序首地址。A3區域中保存多個正式程序,其中所有正式程序都不包含二次加載引導程序bootloader。采用CCS軟件編譯得到DSP正式程序的.out文件,通過TI公司官方格式轉換軟件hex6x轉換為.hex文件,通過JTAG接口燒入DSP的FLASH中。

圖4 DSP的FLASH芯片存儲區域劃分

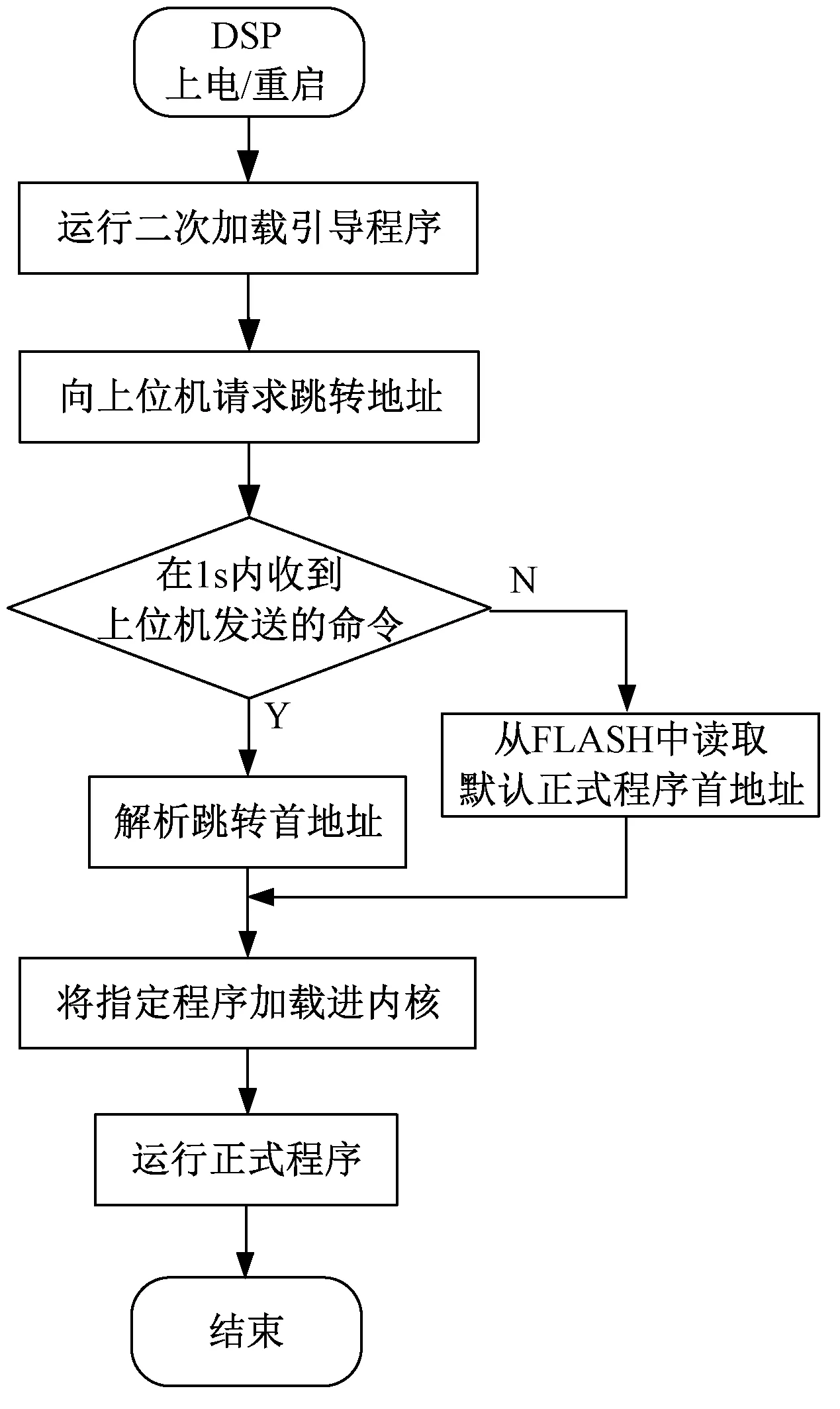

DSP芯片多程序遠程快速切換流程與FPGA芯片類似,如圖5所示。區別只在于DSP可以直接在二次加載引導程序bootloader中與上位機通信,獲取要加載正式程序首地址后,直接從FLASH中將該地址對應的正式程序加載進DSP內核并運行。

圖5 DSP多程序遠程快速切換流程圖

3 方案實施

本文選用的FPGA芯片為XILINX公司的XC7K325T,DSP芯片為TI公司的TMS320C6678,FLASH芯片為SPANSION公司的S29GL01GS,CPLD芯片為INTEL公司的EPM1270G,數據通信總線為RS422總線,上位機為Lab VIEW程序。根據不同的工作場景,對雷達信號處理機采用不同的程序加載模式,同時采取多種措施確保安全和方便使用。

3.1 程序加載模式

FPGA和DSP芯片在上電或重啟后1 s內根據上位機指令選擇要加載的正式程序,上位機通過CPLD芯片控制指定芯片的重啟。因此,雷達信號處理機有上電運行、上電切換、重啟切換三種程序加載模式。

(1)上電運行默認程序

正常上電,1 s內無上位機命令或FPGA與DSP芯片收到“啟動默認程序”命令時,各芯片從A2區域讀取默認正式程序首地址,執行程序跳轉或加載。

“去你的!”柳紅推了一把蘇秋琴,剛巧推到她敏感的部位。蘇秋琴就故意哎唷唷地呻吟起來,還狠狠地拍了一下柳紅的屁股。柳紅倒不覺得痛,感覺麻酥酥的。她也在蘇秋琴的屁股上回敬了一巴掌。蘇秋琴又趁機抓了一把柳紅的胸膛。倆人在井邊打打鬧鬧的,氣氛就有些曖昧了。

(2)上電切換正式程序

正常上電,1 s內FPGA與DSP芯片收到上位機“切換程序”命令,從中解析出要執行程序切換的器件編號和各自的切換程序首地址,相關器件從解析出的地址加載正式程序,其他器件加載默認程序。

(3)重啟切換正式程序

雷達信號處理機正常運行時,CPLD接收到上位機“重啟芯片”命令,從中解析出器件編號并重啟對應芯片。上位機在FPGA或DSP芯片重啟1 s內發送“切換程序”命令,重啟芯片解析出各自要切換的正式程序首地址后完成跳轉。

3.2 改進措施

為提高穩定性和安全性,并擴展系統功能,本文方案采取了多項改進措施。

(1)可更換默認正式程序

為方便在工程中應用,增加默認程序更換功能。更換時,處理機正常運行,上位機向CPLD發送“重啟芯片”命令,完成對應芯片重啟。上位機在芯片重啟1 s內發送“更換默認程序”命令,重啟芯片解析出各自要更換的默認正式程序首地址,擦除各自FLASH中A2區域并將解析出的地址寫入,完成默認正式程序首地址的更換。

需要注意的是,FLASH芯片在寫操作之前需要先進行擦除操作,擦除以硬件分區(sector)為最小操作單元進行。如表1所示,試驗中采用的S29GL01GS芯片存儲空間大小為128 Mbytes,從地址0x0開始分為1 024個128 kbytes的硬件分區。更換默認正式程序操作需要對A2默認正式程序首地址存儲區域進行擦除與寫入,因此需要將A2區域邊界與FLASH硬件分區對齊,即只能使用1 024個硬件分區中的一個或者連續數個。

表1 FLASH段劃分和硬件分區示意圖

(2)嚴格的校驗機制

采用多種方式確保通信內容完整準確:通信幀中均包含循環冗余校驗(CRC),連續多個特殊幀指代單條命令,指令幀回傳二次校驗,FLASH修改內容回傳校驗。RS422通信總線中上位機為主,其余各芯片為從,采取應答式通信方式。上位機單條指令包含控制內容和數據內容,控制內容由事先約定的連續多個特殊幀指代。各芯片解析出控制命令與數據后,需要回傳上位機確認后才會執行此指令,修改A2區域FLASH存儲內容后需要讀取修改后內容并回傳上位機進行校驗。

(3)全面的狀態監測

各FPGA和DSP芯片進入燒寫程序或二次加載程序、執行命令、開始跳轉,以及CPLD芯片執行重啟指令時,都有狀態信息回傳上位機,可以實時監測通信情況和各芯片工作狀態,有助于故障排查。

4 結果與討論

確定雷達信號處理機多程序遠程快速切換方案后,在驗證系統中實現并進行測試。測試結果表明:該方案能夠在雷達整機狀態下實現信號處理機中FPGA與DSP芯片多程序遠程快速切換功能;單芯片程序切換時間,即從上位機發出切換命令到切換到正式程序運行的時間,在5 s以內。切換功能由FPGA跳轉程序和DSP二次加載程序實現,既能最小化對正式程序的改動,又能不占用正式程序芯片資源。指令傳遞穩定可靠,狀態監測實時全面。

5 結束語

本文對整機狀態下雷達信號處理機多程序遠程快速切換方法進行了研究。針對常見處理機架構,提出了一種切實可行的方案,實現了FPGA和DSP芯片多程序的快速切換。通過提高雷達信號處理機程序加載的靈活性,有助于實現雷達系統多方案快速測試驗證和定制化靈活部署。