一種基于抗輻照體系架構的單粒子效應等效評估擬合算法

高 翔,賴曉玲,賀勇鵬,王 軒,周國昌

(中國空間技術研究院西安分院,西安 710100)

航天應用實踐表明空間單粒子效應(SEE)是航天器工作異常或故障的重要誘因之一[1],同時空間單粒子效應抗輻照加固設計方法也已經廣泛應用于航天器設計中。因此,快速、有效的SEE在軌預測評估方法有助于提升航天器系統可靠性設計效率。

目前,重離子加速器模擬實驗方法是廣泛用于評估和驗證航天器抗輻照設計有效性的重要方法之一[2]。該方法借助實驗獲取多個粒子線性能量轉移(LET)值能譜下的系統功能中斷截面變化值,并進行Weibull飽和曲線擬合,進而可評估航天器在軌預示指標;然而,受國內加速器的條件限制,無論在實驗機時,還是提供可達有效硅表面射程的高能粒子能譜均無法充分滿足航天系統應用需求,例如裝有倒裝焊SRAM型FPGA器件的系統,器件硅襯底表面高達幾百微米,只有通過器件減薄工藝使部分粒子穿透到達器件輻照敏感區,并且在減薄過程中器件冒著被損壞的高風險概率。除了重離子加速器模擬實驗,地面模擬故障注入實驗和基于軟錯誤傳播的故障概率評估方法也是常用的兩種單粒子效應有效性評估方法,然而所述的兩種方法無論在實現復雜度還是在需求等效性上均存在不足。有文獻報道[3-4]開發了SRAM型FPGA的模擬故障注入系統,可定性評估系統可靠性設計,然而無法定量給出在軌預示結果;同時受器件結構的影響,一旦器件類型升級,需要重新解析bit文件完成新注入系統設計,該方法通用性差、設計復雜。有研究者[5]結合SRAM型FPGA配置資源與電路耦合關系,提出基于軟錯誤傳播概率的系統故障評估方法,以概率評判系統的抗輻照可靠性設計,其量化后的概率值不能用于系統在軌預示分析。

因此,本文從系統抗輻照架構的影響因子出發[5-6],結合器件靜態截面和以部分輻照實驗數據為參考[7],構建多能譜LET值與系統功能中斷截面自適應擬合算法模型,獲取單粒子效應下系統功能中斷截面隨LET值變化的等效耦合關系,實現以通用性的等效擬合算法而降低重離子加速器實驗的依賴,達到以高效精準的擬合實驗數據完成對航天器系統抗SEE效應評估驗證的目的。

1 系統抗輻照架構設計

本文以數字信號處理領域中通用的調制解調系統設計為例,構建抗輻照架構系統,并選定LET值開展重離子輻照試驗,獲取算法模型所需的基準數據。

如圖1所示,系統由調制和解調兩大核心功能組成,并分別基于兩塊SRAM型FPGA器件實現,其器件的配置存儲區及關聯的設計資源為空間單粒子效應(SEE)敏感核心部件[8],開展系統防護架構設計。針對器件的內部資源防護,以時序邏輯電路功能模塊為對象開展三模冗余防護設計[9],從而降低電路功能模塊因單粒子軟錯誤在功能模塊間傳播耦合造成系統功能中斷的幾率;針對整個系統的防護設計,設置系統軟錯誤防護監控單元,對配置存儲區實現配置信息加載和動態刷新的防護設計,從而減少單粒子軟錯誤的累積,同時通過數據接收比較模塊對功能的關鍵數據信號監測,開展系統功能異常軟復位設計。

圖1 系統抗輻照架構體系設計框圖

2 算法模型構建

2.1 重粒子輻照實驗環境與器件的匹配

通常,系統抗輻照性能由被輻照器件獲取的系統動態功能中斷截面(σsys)隨離子LET值變化的曲線來表征,隨后結合系統所處的空間輻照環境,完成系統在軌翻預示[10]。因此地面加速器模擬實驗的重要目的是獲取多個器件σsys-LET離散點,擬合出較精確的分布曲線。

圖2[7]給出了Xilinx公司Virtex4型FPGA配置存儲單元靜態翻轉截面與LET值輻照實驗的擬合變化曲線。然而,由于該類器件是倒裝芯片,即使通過器件減薄,國內輻照實驗也只可進行有限射程范圍的離子束輻照實驗,獲取部分基準采樣數據。

圖2 Virtex4型FPGA配置存儲單元靜態翻轉截面與LET值輻照實驗的擬合變化曲線

2.2 EFA-ESEE自適應等效擬合算法模型

利用系統抗輻照架構設計特性,并基于可獲取的部分輻照實驗的基準數據,采用二次擬合構建EFA-ESEE算法模型,獲取飽和LET閾值內的任意σsys與LET自適應變化關系,實現系統的可靠性設計評估,以下為算法模型的實現過程。

(1)構建系統功能中斷頻率函數

SRAM型FPGA在內部電路模塊防護體系設計架構下,當被有效射程的離子束輻照時,單位時間內引起FPGA系統功能中斷頻率定義為系統功能中斷頻率,用函數EFPGA表示:

EFPGA=f(σ,L,T,nsrams,SERF)

(1)

式中,σ表示LET值下的FPGA配置存儲區靜態單粒子翻轉截面(cm2/bit);L表示實驗時的離子注量率(個/cm2·s);T表示實驗時的離子輻照單位時間(s);nsrams表示FPGA系統所占的配置存儲區資源(bit);SERF表示系設抗輻照計架構下,電路的抗單粒子軟錯誤功能中斷可靠性系數。

因此,帶入上述參數,式(1)可近似等效為:

EFPGA=σ·L·T·nsrams·SERF

(2)

引入參數α,定義為基于外部軟錯誤監控單元,系統級軟錯誤防護措施作用于FPGA的可靠性貢獻度耦合因子。在系統級防護設計架構下,式(2)可變換為:

Esys=α·σ·L·T·nsrams·SERF

(3)

根據參數σsys的物理含義,即平均一個離子輻照引發系統功能中斷的概率,等價為:

(4)

式中,N表示一次功能中斷平均注入的離子總數。

因此,式(2)和式(3)可轉化為:

(5)

式中,Lfpga和Lsys分別對應FPGA在內部電路模塊防護設計架構和系統級防護設計架構下,平均一次功能中斷的離子注量率;而Nfpga和Nsys分別對應上述兩種防護設計架構下,平均一次功能中斷累積輻照離子數。

(2)構建LET-系統功能中斷截面自適應變化函數

針對同一個FPGA系統,在相同內部電路模塊防護設計架構和輻照時間內,采用LET1和LET2值離子能譜輻照,可得到:

(6)

同理,同一個FPGA系統,在系統級防護設計架構和輻照時間內,可得到:

(7)

式中,α1和α2分別為LET1和LET2值,對應系統級軟錯誤防護措施可靠性貢獻度耦合因子。

因此,當已知一組LET值的輻照實驗數據,由式(6)和式(7),即可等效得到其他任意飽和LET閾值范圍內的系統功能中斷截面。

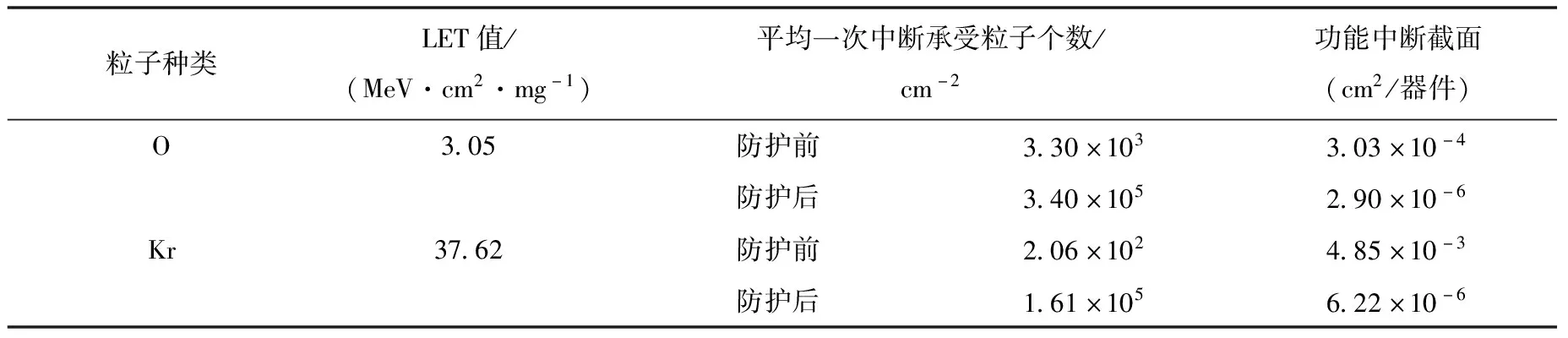

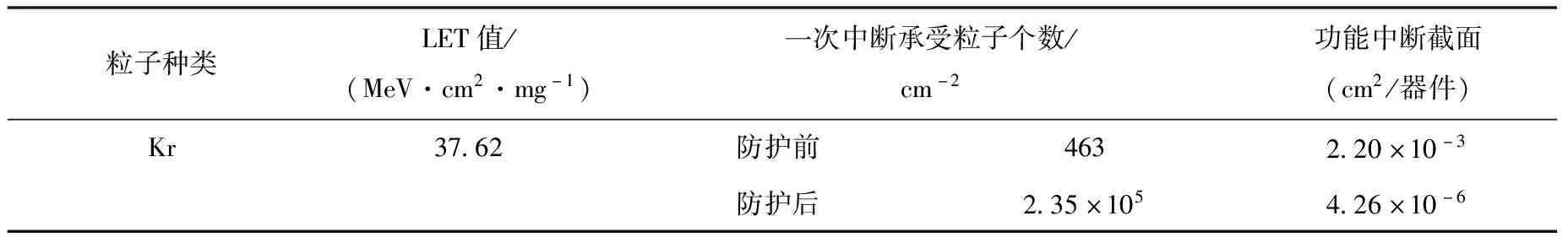

3 實驗分析

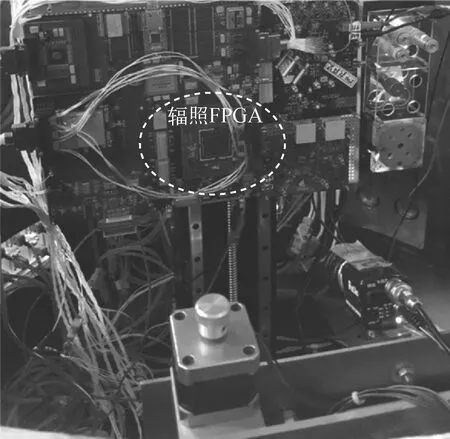

基于圖3為例的系統架構,實驗中采用了兩片Xilinx公司的Virtex4 FPGA器件,分別完成了調制和解調系統的電路設計。實驗前對器件襯底進行精細打磨,并且在中國原子能科學研究院的串列加速器和中科院的重離子加速上分別進行了O和Kr離子的輻照實驗,作為獲取基準數據,詳見表1和表2。在表中,防護前表示實驗系統未采取任何抗輻照防護措施;防護后則表示該系統采用了系統級抗輻照防護架構設計,實現在器件內部采用部分三模冗余、塊RAM軟錯誤反饋糾檢錯防護設計,同時結合系統級單粒子軟錯誤防護監控單元,實現對器件關鍵信號監測與復位、系統關鍵功能信號監測與復位、系統定時刷等系統級防護設計。

圖3 Virtex4 FPGA電路系統輻照實驗現場圖

表1 調制系統FPGA實驗數據

表2 解調系統FPGA實驗數據

基于表2,防護前實驗數據代入EFA-ESEE模型中的式(6),可得到LET值分別為37.62 MeV·cm2/mg 的Kr離子和3.05 MeV·cm2/mg的O離子,靜態翻轉截面比值近似為σKr/σO≈16,而從圖2 Xilinx提供的器件輻照數據,該比值為14。因此,算法模型分析的數據近似等效實驗數據,模型推論過程合理有效。

同時,利用表2解調FPGA防護后實驗數據,代入模型中的式(7),可以得到在Kr離子和O離子輻照下,可靠性貢獻度耦合因子比值αO/αKr≈7.58。由于隨著入射粒子的LET值增大,器件配置存儲區受能量激發出現多位翻轉情況,使系統級單粒子軟錯誤防護監控單元對系統的可靠性貢獻度將減弱,詳見圖2實驗數據的曲線變化趨勢。因此,Kr離子與O離子可靠性貢獻度因子比值反映出上述系統可靠性防護設計變化趨勢,同時證明了算法模型設置該值的合理有效性。

因此,結合上述分析,EFA-ESEE模型的計算結果與圖2實驗數據相吻合。

調制和解調FPGA系統均構建于相同的系統級防護設計架構,利用可靠性貢獻度因子等價原理。由表1和表2,擬合得到調制系統在Kr離子輻照條件下的數據,結果見表3。

表3 調制系統FPGA的擬合實驗數據

同理,基于EFA-ESEE模型,還可以任意自適應擬合得到其他任意飽和LET閾值內系統的功能中斷截面數據。圖4為中國原子能科學研究院的串列加速器開展的Viretex5 FPGA配置存儲區動態回讀系統翻轉截面輻照實驗,其中靜態翻轉截面由文獻[11]獲取,通過表4的數據比對,擬合模型與輻照實驗數據誤差控制在5%以內,因此擬合模型可用于地面模擬輻照實驗評估。

圖4 Virtex5 FPGA電路系統輻照實驗現場圖

表4 Virtex5 FPGA配置存儲區回讀電路系統的翻轉截面數據

4 結論

當前,由于器件制造工藝、系統架構不同,造成了抗輻照實驗條件選取的差異,從而增加了被測試系統數據獲取難度。本文從抗輻照系統架構設計出發,建立隨粒子LET值變化的EFA-ESEE自適應評估擬合算法模型。該模型以系統抗輻照設計架構與器件單粒子效應傳播機理為出發點,利用輻照實驗基準數據完成功能中斷截面隨LET值的自適應擬合,獲取飽和LET值內的功能中斷截面變化值,實現了實用、高效、精準的數據提取過程,從而減低以加速器輻照實驗獲取翻轉截面的依賴性。最終通過實驗結果分析,該算法模型可以提升航天器系統抗SEE效應的評估效率。