航空電子產品信號完整性及信號串擾控制設計分析

吉茂林 王瑋

摘要:本文主要介紹了航空電子產品的信號完整性設計中信號傳輸損耗控制、信號反射處理、信號串擾控制、差分互聯設計,依據理論進行設計分析。

關鍵詞:信號完整性;信號串擾控制

一、引言

航空電子產品設計過程中時常會遇到一個問題:在設計高頻高速信號電路時,未考慮信號完整性問題帶來的影響,導致信號質量差,裝機后在復雜工作環境中不滿足產品性能要求。

為了解決上述電子產品設計過程中存在的可靠性問題,開展信號完整性設計分析。目的是在PCB設計中就考慮影響信號完整性的因素,設計過程中或設計完成后利用仿真進行定性或定量分析,進而排查并優化可能存在的風險問題,以提高電路健壯性。

二、信號完整性概述

信號完整性是指信號傳輸過程中能夠保持信號時域和頻域特性的能力,即信號在電路中能以正確的時序、幅值以及相位等做出響應。信號完整性主要包括以下幾個方面內容:

(1)信號沿印制板傳輸線傳遞時,由于輻射損耗、導線損耗和介質損耗,會使信號強度衰減。必要時,需對印制板傳輸線的衰減常數進行測定或計算。

(2)信號傳輸過程中,只要遇到瞬時阻抗突變,就會存在反射和失真,現象包括:振鈴、邊沿是否單調、過沖/下沖、邊沿臺階等。

(3)串擾是兩條信號線之間距離相近產生耦合,在信號線之間的互感和互容而引起的噪聲,在高頻、高速電路設計時,應重視信號串擾。

(4)差分互連是利用存在耦合的傳輸線進行信號輸入輸出,抵御差分串擾的魯棒性高,且具有對抗返回路徑間隙阻抗突變的能力。

三、信號串擾控制設計分析

(一)信號串擾控制注意事項

控制信號串擾應注意:

(1)如果布線空間允許,線間距宜盡量大。

(2)同層和相鄰層走線不宜長距離平行。

(3)信號線間應隔離地線。

(4)信號線過孔周圍應接地過孔。

(二)設計應用

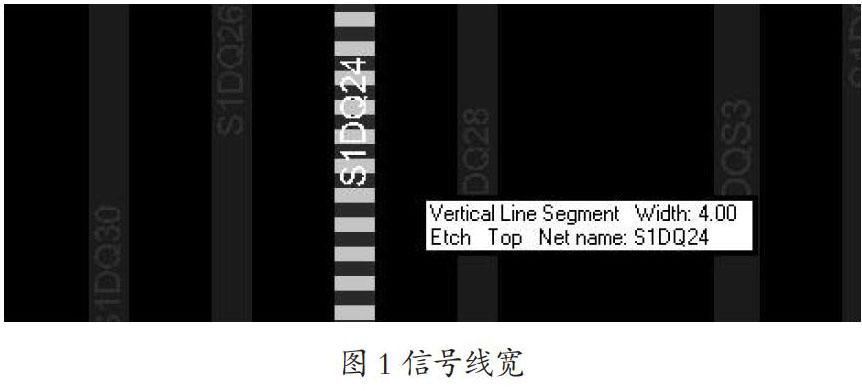

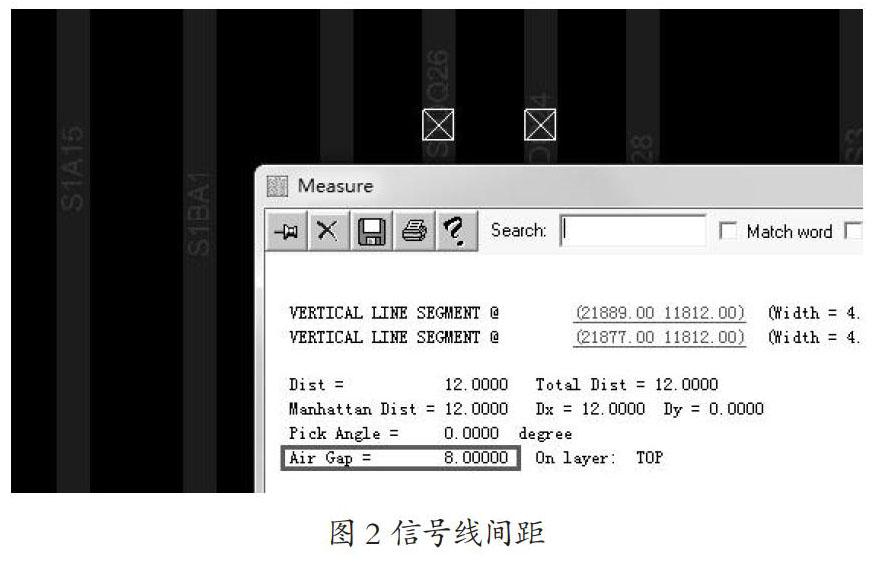

DDR3數據信號線屬于高速信號線,信號線間容易發生串擾,設計要求滿足3W原則,當前信號線寬4.0mil,信號間距為8.0mil,如圖1和圖2所示。

四、結束語

傳統的電路設計方法是根據要求研制產品樣機,然后進行電路調試,調試過程中通過測試發現問題,然后重新設計再次加工調試,即所謂“試錯”方式。這種方法開發周期長,成本很高,有時出現的問題可能需要多次改版才能解決。如今產品的研制時間和產品的成本、性能同等重要,采用傳統做法效率會很低。如果在設計初期不考慮信號完整性,就很難做到一次成功。

參考文獻:

[1] 《信號完整性分析 Signal Integrity:Simplified》 [美] Eric Bogatin 著,李玉山、李麗平 等譯,電子工業出版社