一種高效的源同步總線收發編碼方法

徐磊 紀小明 趙永春

摘要:源同步串行總線是FPGA片間互連的常用方式。針對傳統的源同步串行總線傳輸方法對線路的利用率不高的情況,提出了一種高效的源同步總線收發編解碼方法,可以顯著提高源同步串行總線的傳輸效率。

關鍵詞:FPGA;源同步;編碼方法

0 引言

現場可編程門陣列(FPGA)是近年來快速發展的新型可編程邏輯器件,主要應用于集成電路的定制電路開發驗證[1]。在數字系統中,多片FPGA互連傳輸數據需要穩定高效的接口,源同步串行總線是FPGA片間互連的常用方式。源同步系統中每兩個部件之間數據進行單向或雙向傳遞,在和數據同向的傳遞方向上同時傳遞一個和數據保持特定相位關系的參考時鐘,在數據的源端,參考時鐘和數據保持確定的相位關系,而在數據的目的端,另外一個部件可根據參考時鐘的相位來準確捕獲對應的數據[2]。系統采用源同步機制,可以允許發送端在數據信號線或時鐘信號線上出現周期性或隨機的信號抖動,即使數據或時鐘因為抖動出現偏差,只要確保兩者的時序關系保持一致就可以保證收端獲得正確的信號[3]。

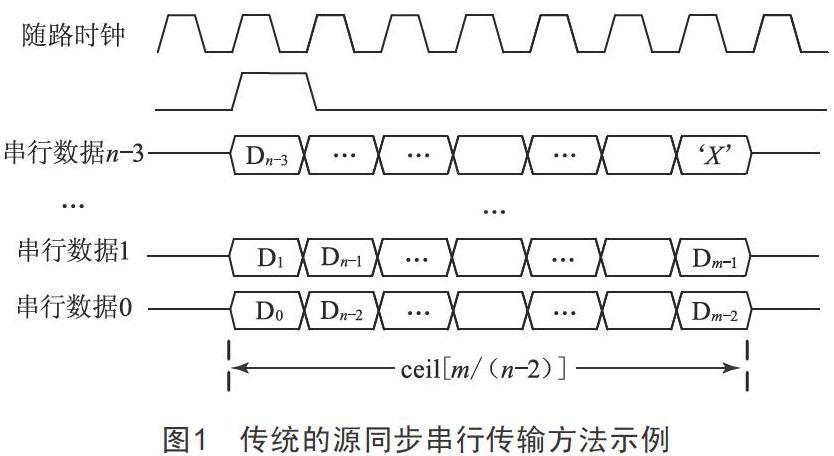

FPGA片間有傳輸數據需求時,傳統的源同步串行總線編碼方法,以n根線路傳輸m位寬數據為例,n根線路中固定一路傳輸隨路時鐘,再選一路傳輸高有效的同步脈沖,同步脈沖指示傳輸的有效數據的起始,再將m位寬數據進行并串轉換并依次序平鋪在剩余的n-2根線路上,易知并串轉換后數據長度為ceil[m/(n-2)],其中ceil為向上取整。接收端進行解碼時,使用隨路時鐘采集同步脈沖的狀態,當檢測到高有效的同步脈沖時,認為接收到了有效數據的低位,開始對串行的有效數據進行緩存,逐次接收數據,在第ceil[m/(n-2)]次時,串行有效數據全部接收完畢,此時再串并轉換就最終恢復出m位寬數據。傳統的源同步串行傳輸方法如圖1所示。

顯然,傳統的源同步串行總線傳輸方法,連續傳輸的最小間隔為ceil[m/(n-2)],即數據傳輸延遲。

1 高效的源同步總線收發編解碼方法

傳統的源同步串行總線傳輸方法對線路的利用率并不高,尤其是同步脈沖這一路并未參與有效數據的傳輸,為了提高線路利用率,減小連續傳輸的最小間隔(傳輸延遲),本文提出了一種高效的源同步總線收發編解碼方法。

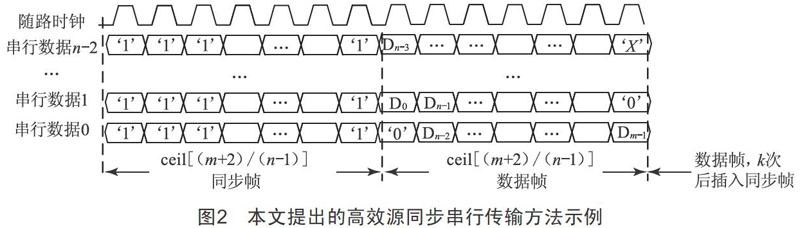

以n根線路傳輸m位寬數據為例,n根線路中固定一路傳輸隨路時鐘,剩余的n-1路全部用來傳輸有效數據,同時將有效數據分為數據幀和同步幀兩種類型。本文提出的高效源同步串行傳輸方法原理如圖2所示。

數據幀的設計:m位寬數據在最低位和最高位之外分別增加一位“0”,形成m+2位寬數據,將m+2位寬數據進行并串轉換并依次序平鋪在剩余的n-1根線路上,并串轉換后串行數據長度為ceil[(m+2)/(n-1)]。

同步幀的設計:同步幀與數據幀的長度保持一致,也為ceil[(m+2)/(n-1)],同步幀的數據全部為“1”。

發送端在首次傳輸數據幀之前先發一次同步幀,之后每隔ceil[(m+2)/(n-1)]長度傳輸1次數據幀,在連續發k次數據幀后插入一次同步幀,后續按k次數據幀插入一次同步幀的規律持續發送。同步幀的插入確保接收端同步性的判斷和維持,插入間隔k可設置為100萬次。

接收端使用隨路時鐘采集其余n-1線路的狀態,每次對連續的ceil[(m+2)/(n-1)]長度串行數據進行判斷,如果其內容全部為“1”則檢測到了同步幀。數據幀是由“0”作為起始和結尾的,故這樣檢測得到的同步幀是唯一的。檢測到同步幀后,對后續的連續k次ceil[(m+2)/(n-1)]長度串行數據做串并轉換,并舍棄起始和結尾的“0”就得到了最終的有效數據。k次之后驗證接收到的是否是同步幀,若是則說明總線傳輸穩定,接收的數據正確可靠,若否則說明總線出現傳輸錯誤。驗證了同步幀后,按k次數據幀接續1次同步幀的規律對總線進行有效數據的提取和同步性驗證。

由上述設計可知,本文提出的高效源同步總線收發編解碼方法,連續傳輸的最小間隔和傳輸延遲為ceil[(m+2)/(n-1)],相比傳統方法有顯著提升,并引進了錯誤檢測機制。

2 效果對比

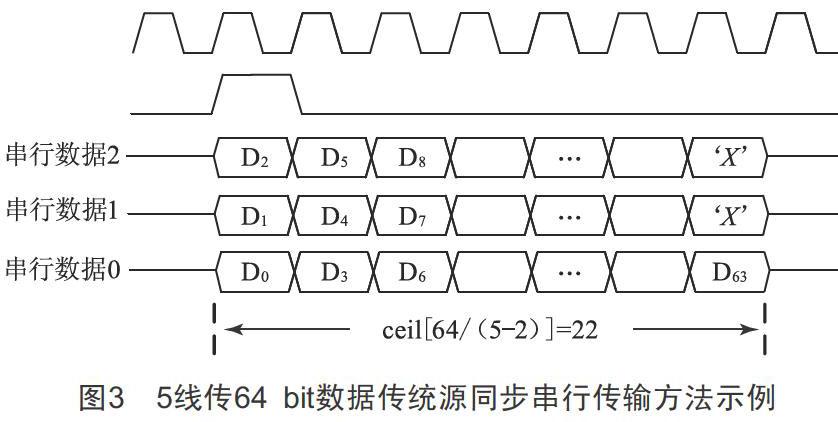

本文提出的編碼方法能顯著提高源同步總線的傳輸效率,具體以5線傳輸64 bit數據為例,傳統源同步串行傳輸方法如圖3所示。源同步時鐘用1根線,數據同步有效標志用1根線,64 bit并行數據經過并串轉換需要ceil[64/(5-2)]=22個時鐘節拍傳輸,因此連續傳輸間隔為22個時鐘周期。

5線傳64 bit數據的高效源同步串行傳輸方法如圖4所示。源同步時鐘用1根線,其余4根線全用于有效數據的傳輸。數據幀的長度為ceil[(64+2)/(5-1)]=17,同步幀的長度與數據幀相同。同步幀的插入間隔在源同步條件下可以比較大,比如10 000次數據幀后插入1次同步幀,因此同步幀的影響可以忽略不計,從而線路資源全用于有效數據的傳輸。

設隨路時鐘為150 MHz,周期為6.66 ns,則2線傳輸28 bit數據包的傳輸效率對比如表1所示。新編碼方法在線路資源不變的情況下,傳輸效率提升了29%。

3 結語

源同步高速接口使用并行鏈路連接,以時鐘和多位數據相伴傳輸,解決了接收方的數據同步問題[4]。針對傳統的源同步串行總線編碼方法效率不高的情況,本文提出了一種更高效的編碼方式,該方式可以充分利用線路的帶寬資源,顯著提升數據傳輸速率。

[參考文獻]

[1] 卿啟新.基于FPGA的LVDS視頻信號轉換系統設計實現[D].廣州:華南理工大學,2011.

[2] 顧峰,呂余清.應用源同步技術實現高速ADC與FPGA互連[J].電子技術,2016(10):30-33.

[3] 張驊.源同步接口芯片的測試[J].集成電路應用,2003(10):62-64.

[4] 許勇.一個源同步高速接口的設計[J].高性能計算技術,2003(4):29-33.

收稿日期:2020-08-03

作者簡介:徐磊(1987—),男,陜西西安人,碩士研究生,工程師,研究方向:電子對抗技術。