基于Zynq-7100數據存儲模塊的設計

鄭駿 徐海納

摘要:數據存儲模塊廣泛地用于雷達、醫療、通信等行業。隨著雷達系統高數據率、小型化的要求,對數據存儲模塊帶來了更大的挑戰。針對相關要求,設計了一款基于Zynq-7100的數據存儲模塊。該數據存儲模塊一方面采用Zynq-7100內的PL實現raid0方式完成對多路mSATA盤的控制,以及高速采集數據的收發;另一方面采用Zynq的PS實現自定義文件,完成了對mSATA盤的管理。模塊測試結果表明,設計的數據儲存模塊速度高,性能穩定,并有效地減少了設備的體積。

關鍵詞:Zynq-7100;raid0;mSATA;文件系統

中圖分類號:TP311? ? ? 文獻標識碼:A

文章編號:1009-3044(2020)23-0045-02

數據存儲模塊是用來對系統運行、系統測試或科學試驗等過程中產生的數據流或信號進行記錄,后期向用戶提供獲得的原始數據的設備。其廣泛應用于軍工、安全、控制、航天航空等領域。隨著雷達系統的發展,高速多通道采集技術的成熟,對相應的數據存儲模塊提出了更大的要求:1)高存儲速率,可以實時連續記錄高速的原始數據;2)大存儲容量,滿足采集設備下發的海量數據的存儲;3)存儲可靠性,保證存儲設備穩定的工作,以及存儲數據的正確性;4)小型化設計,在保證存儲容量的同時,需要減少系統的體積,有一定的擴展性。

Xilinx公司的全可編程Zynq-7100系列芯片成功將高大1GHz的Cortex-A9 MPCore雙核處理器與低功耗可編程邏輯緊密集成在一起;并在ARM處理器與FPGA之間采用AXI4通信總線,在器件內部提供了高可靠性,高帶寬的通道。結合該器件的優勢,設計實現的數據存儲模塊相對于其他架構的存儲模塊具有存儲速率高,存儲空間靈活的特點。

1 數據存儲模塊總體設計

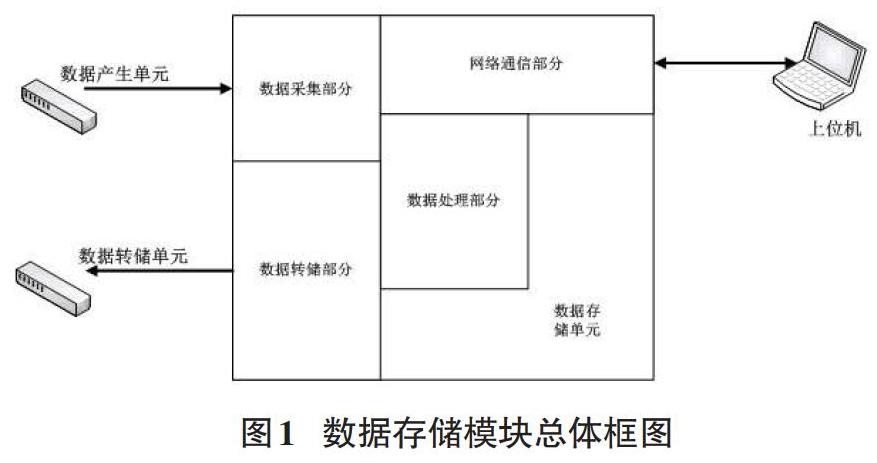

基于Zynq-7100數據存儲模塊由數據處理單元和數據存儲單元兩部分組成,數據存儲模塊總體框圖如圖1所示。

數據處理單元完成高速數據的接收,存儲自定系統的數據打包,數據寫入讀取,以及外部通信、調試的工作。

數據存儲單元由mSATA固態硬盤陣列構成,提供1TB~8TB的存儲空間的擴展,以及410MB/s~3.2GB/s的數據讀寫速率。

2 硬件構成與設計

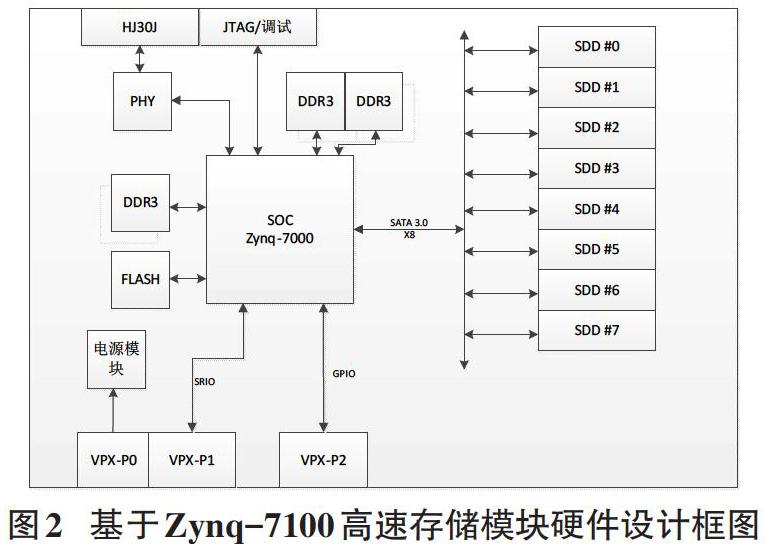

基于Zynq-7100數據存儲模塊硬件設計框圖如圖2所示。模塊為標準的6U VPX結構,其主要由Zynq-7100處理平臺,數據存儲單元DDR3、FlASH,文件存儲單元,以及通信外設組成。

2.1 Zynq-7100處理平臺

Zynq-7100處理平臺主要實現高速數據的接收,存儲文件的生成,存儲,轉儲,以及系統狀態檢測的功能。

XC7Z100芯片為Xilinx公司Zynq-7000系列的全可編程Soc,PL單元提供1組X4的SRIO接口;提供8組SATA接口;提供多個交互接口。PS單元則提供以太網接口,以及串行接口。

借助AXI(高級擴展總線)互聯技術,實現芯片內部PL與PS之間的高性能的數據交換。為自定義文件系統的生成,文件數據管理方面提供了片內高速可靠的途徑。

2.2 數據存儲單元

數據存儲單元分為3個部分:數據緩存、內存以及配置存儲部分。

數據緩存單元采用兩組MT29F系列芯片,構建容量為4GB存儲數據的緩存。

內存單元采用2片MT41K系列芯片以及1GB的數據空間,完成系統的運行。

配置存儲單元采用256Mb的QSPI FLASH芯片,用于系統的上電配置以及引導。

2.3 外部通信單元

外部通信單元主要有以太網通信單元,串口通信單元,以及GPIO接口單元。

以太網通信單元,選用100/1000M傳輸速率自適應功能的以太網物理層芯片88E1116。配合XC7Z100芯片PS單元的MAC層控制器,實現以太網通信功能。

串口通信單元,選用電平轉換芯片MAX3232。配合XC7Z100芯片PS單元的串口控制器,實現串口通信功能。

GPIO接口單元,由XC7Z100芯片PL單元直接提供,采用電平轉換芯片進行信號的保護。

2.4 文件存儲單元

文件存儲單元由mSATA固態硬盤構成。其讀寫速率可達到410MB/s,物理接口為mSATA接口。

設計中固態硬盤通過接插件安裝在電路板上。可實現多達8塊固態硬盤的安裝。可以根據需要安裝靈活安裝所需的固態硬盤。

3軟件系統架構與設計

本設計采用Vivado2017.4設計套件完成軟件系統的架構與調試工作。按照存儲的功能,將整個系統分為五個功能模塊,分別為高速數據接口管理模塊、數據緩存管理模塊、文件系統管理模塊、RAID控制管理模塊,狀態顯示模塊。

3.1 高速數據接口管理模塊設計

高速數據接口管理模塊主要通過Zynq-7100的高速串行數據收發控制器實現的控制功能,提供存儲系統對外的數據交互控制。

接收數據經過高速數據接口管理模塊。如果是模塊的控制指令,將被分發到文件系統管理模塊;反之將分發到數據緩存管理模塊。

發送數據經過高速數據接口管理模塊,區分模塊的狀態數據、轉儲數據,供外部系統使用。

3.2 數據緩存管理模塊設計

由于數據存儲單元(mSATA)在數據存儲時會有短暫性的帶寬下滑,以及數據偶發的數據傳輸錯誤出現,采用DDR3存儲芯片實現輸入數據的緩存。

數據存儲模塊對外的數據輸入接口為X4 SRIO,最大數據速率為5Gb/s×4×0.8=2GB/s(即每秒有2GB的數據需要寫入)。而模塊的數據存儲單元最大為8個固態硬盤,最大數據速率為410MB/s×8=3.2GB/s(即出現最壞的帶寬下滑情況,抑或數據傳輸錯誤情況下的數據量為3.2GB)。

此外數據存儲模塊可實現對DDR3芯片組的控制,其讀寫最大數據速率為1600Mb/s×16×1/8=3.125GB/s(即每秒可滿足3.125GB的數據要求)。可以在數據緩存的容量以及數據率的兩個方面滿足系統需求。

3.3 文件系統管理模塊設計

文件系統管理模塊實現在Zynq-7100的PS端。使用自定義的文件系統,該系統支持文件的建立、命名、信息備注等功能。對每個文件的扇區地址進行了管理,用戶只需指定文件ID號。當需要對存儲數據進行讀寫操作時,文件系統管理模塊將獲取文件對應的扇區地址,并完成相關操作。

3.4 RAID控制管理模塊設計

設計中通過Zynq-7100 PL端的數字邏輯實現mSATA盤的控制和管理。SATA控制管理模塊遵循SATA協議。使用Zynq-7100集成的高速串行數據收發控制器實現SATA數據的解碼、同步以及RAID工作。

3.5 狀態顯示模塊設計

本板指示燈顯示模塊主要將本模塊中各個電源軌的反饋信號,mSATA盤在位信號,工作狀態等信息,通過板載的LED燈反饋工作狀態。

狀態信息上報模塊將mSATA盤的工作狀態,電源軌工作狀態,系統周期自檢信息等通過以太網形式進行發送給上位機,實時觀測。

4模塊測試與分析

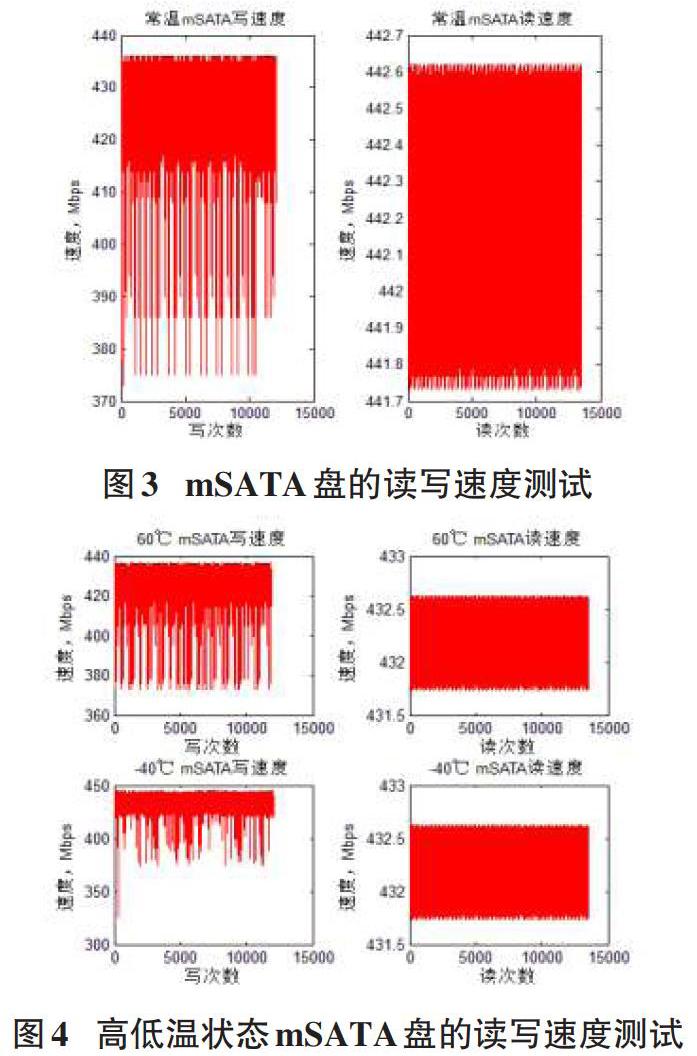

對數據存儲模塊性能進行測試,將模塊通過母板與數據產生板相連接。模塊采用8個mSATA盤(容量1TB)做為存儲介質,內部的緩存區設置為1Mb。對連續的數據進行寫入操作,每個mSATA盤的測試結果如圖3所示。在高溫60℃,低溫-40℃的環境中進行相同測試。每個mSATA盤測試結果如圖4所示。

滿足對于模塊具有1TB~8TB的存儲空間的擴展,以及410MB/s~3.2GB/s的數據讀寫速率的設計要求。

5 結論

基于Zynq-7100數據存儲模塊軟硬件相結合的設計,以及相關的測試結果表明,使用該平臺進行存儲模塊的設計方法,為高速存儲模塊的設計提供了可行的設計方案。基于Zynq-7100處理平臺的設計,即具備了FPGA硬件可編程的優勢,又將文件系統有效的移植到Cortex-A9處理器上完成,滿足了高速率、大容量以及小型化的需求。

參考文獻:

[1] 楊佳朋.SATA控制器的設計與FPGA驗證[D].太原:太原理工大學,2013.

[2] 李曄.基于FPGA的嵌入式高速SATA接口主機控制系統研究與設計[D].北京:北京郵電大學,2011.

[3] 劉文國,李廣軍,林水生.基于FPGA的SATA硬盤加解密控制器設計[J].電子與封裝,2009,9(6):25-28.

[4] 朱琛,崔鐳,邵春偉,等.基于FPGA的高速光纖傳輸卡[J].電子與封裝,2018,18(3):22-25.

[5] 范國浩,張艷兵,李新娥.基于FPGA抗高沖擊機載雷達回波存儲系統設計[J].電子技術應用,2016,42(4):78-80,84.

【通聯編輯:李雅琪】