高速量子隨機數產生中的實時并行后處理

吳明川,成 琛,張江江,郭曉敏,郭龑強,2

(1. 太原理工大學 a.新型傳感器與智能控制教育部重點實驗室; b. 物理與光電工程學院,太原 030024;2. 山西大學 量子光學與光量子器件國家重點實驗室,太原 030006)

0 引 言

隨機數是多種現代應用中的重要資源,如密碼學[1-2]、統計學和科學模擬[3]等。量子隨機數發生器(Quantum Random Number Generator, QRNG)利用量子物理學的基本原理,理論上可以產生不可預測、不可復現的真隨機數,但實際應用中量子信號會不可避免地混入經典噪聲,影響隨機性和安全性[4],因此需要對原始量子隨機數進行后處理。在目前已有的多種后處理方法中,托普利茨(Toeplitz)提取器為信息論可證的隨機提取方案,且目前已開展了基于現場可編程門陣列(Field Programmable Gate Array, FPGA)實時后處理的實驗研究。

基于FPGA的量子隨機數實時后處理方案中,在模數轉換器(Analog to Digital Converter, ADC)采樣獲得原始隨機數的同時,需要FPGA實時對隨機數后處理。目前基于FPGA硬件已達到了3.36[5]和6.00 Gbit/s[6-7]等較高的量子隨機數產生速率,而采用的ADC采樣頻率達到1 GSa/s[5-7],同時依賴于FPGA對高采樣率ADC的支持,實質上造成了QRNG的高成本,阻礙了其實用化。

本文基于量子真空態寬帶噪聲起伏[8-12]以較低采樣率的ADC并行提取3個通道的量子隨機數,基于FPGA的后處理設計,充分利用FPGA資源,發揮了FPGA的最大處理性能。在一個中等性能的FPGA中構建了3路并行后處理的Toeplitz哈希提取器。最終,FPGA后處理模塊資源占用為61%,其余輔助模塊為30%,實現了提取速度為8.24 Gbit/s的3通道量子隨機數的實時產生及安全后處理。此外對生成的隨機數進行了多項評測以保證隨機數的隨機性。

1 實驗設計與分析

1.1 實驗裝置

實驗方案如圖1所示。量子熵源源于真空態的正交起伏,其為能量最低的自然純態,具有較高的安全性。之前的研究工作中[10-12],基于真空狀態QRNG的生成速率受量子邊帶模式帶寬的限制。為了充分利用量子熵源,利用寬帶平衡零拍探測器(Balanced Homodyne Detector, BHD)對量子真空態分量起伏進行提取,同時構建3通道并行隨機數輸出及后處理。

圖1 基于真空態量子分量起伏的高速量子隨機數產生及實時并行后處理實驗方案

圖1中,單模激光器工作的中心波長為1 550 nm,在BHD(1.6 GHz,BPD480C-AC)的零拍探測帶寬內提取3個獨立的量子邊帶模式。隨后,利用混頻器和低通濾波器從零拍信號中提取3個帶寬為120 MHz、中心頻率分別為200、600 MHz和1 GHz的量子邊頻帶模式。混頻濾波中的參考信號由SG提供。3個ADC的采樣頻率均為240 MHz,采樣精度均為16位,分別對相應頻率模式下的信號進行采樣,3路采集獲得的原始隨機比特分別在硬件FPGA(xc7k325t-2ffg676)中進行實時并行后處理,最終將3個通道生成的隨機數通過高速串行計算機擴展總線標準接口(Peripheral Component Interconnect Express, PCI-E)實時輸出。

1.2 FPGA實現Toeplitz后處理的資源占用分析

本文利用集成處理環境(Integration Software Environment, ISE)在一個FPGA(xc7k325t,Xilinx Inc,California,USA)中實現了3路Toeplitz 實時安全量子隨機數后處理。因為Toeplitz矩陣運算中不同列之間的運算完全獨立,而且隨機數后處理僅涉及二進制比特的邏輯運算,FPGA的特性使其非常適合多路量子隨機數生成的并行后處理,但Toeplitz后處理算法涉及大規模矩陣運算,會占用FPGA中大量的邏輯資源,所以有必要分析并優化其硬件資源。

本文優化了FPGA內部的邏輯資源,以實現3個Toeplitz矩陣的并行計算,并使硬件邏輯資源的利用達到最大化。本文選擇的FPGA芯片為Kentex7-325t,可提供約203 800個查找表(Look-Up Table, LUT)。ADC控制和高速輸出控制等其他模塊所需使用的LUT約占總硬件資源的28.4%。根據信息論對后處理安全性的分析[13],Toeplitz矩陣的行數m和列數n至少應為102量級,這就會導致剩余的資源不足以構建相應規模的Toeplitz矩陣。為了減少資源的使用,將整體規模較大的Toeplitz矩陣與原始隨機數序列之間的處理分解為多個Toeplitz子矩陣與較短的原始隨機數子序列之間的處理,同時增加整體后處理所需的時鐘周期數,進而構建可即時處理ADC所生成隨機比特的隨機提取器,最終實現QRNG后處理的實時性。

m×nToeplitz矩陣被劃分為行列數分別為m和k的n/k個子矩陣(n為k的整數倍),因此整個Toeplitz矩陣處理被分為n/k個步驟。每個步驟都是對m×k個子矩陣和k位原始隨機數序列的乘法計算,該過程占用一個時鐘周期,具體拆分過程為

式中:s1,s2,…,sm+n-1為Toeplitz矩陣元;d1,d2,…,dn為ADC的輸入。k值越大,則每個步驟所需的邏輯資源越多。在給定的時鐘頻率下,由于實時性的要求,不能將k的值設置得太小——在一段時間(多個時鐘周期)內,對于每個通道,FPGA中的后處理位數必須等于ADC讀取的位數。本文中ADC采樣和FPGA后處理的時鐘頻率均為240 MHz,k的值設置為16,等于ADC的分辨率。

在確定了子矩陣列數后,需要確定3個Toeplitz矩陣的規模。根據信息論,后處理的提取比例受剩余哈希引理的約束[14]:

式中:l為可提取的隨機比特長度;Hmin為需要進行提取的原始隨機數序列的原始最小熵含量;ε為安全參數。最小熵表征了測量結果統計分布中可提取的隨機數的下限,用于衡量量子隨機數的隨機性,其定義為

式中:Pr[X=V]為樣本空間X中二進制元素V的統計概率;δ為ADC分辨率。在前期真空QRNG熵含量最大化研究的基礎上,實驗實現了3路子熵源的最優化采樣范圍設置。基于3路原始數據采樣(80 Mbits)分析得出各路信號的經典及總的統計分布方差[15],基于下式計算得出每一路各自的最小熵含量為

本文中FPGA的LUT總數為203 800。比較使用不同數量通道后處理時的邏輯資源占用情況,可以發現隨著并行通道數量的增加,PCI-E控制模塊和其他功能模塊所占用的LUT數量變化幅度不大,約占FPGA中所有LUT的28.4%,平均每個通道的Toeplitz矩陣后處理約占總硬件資源的20.3%。顯然,多個真空邊帶模式提取的原始比特僅在一個FPGA中并行獨立地進行后處理,同時具有較高的FPGA邏輯資源利用率。

不同通道數后處理時FPGA的邏輯資源占用情況如表1所示。

表1 不同通道數后處理時FPGA的邏輯資源占用(LUT占用)

1.3 并行Toeplitz后處理算法的時序設計

基于FPGA的并行處理性能,構建了雙層并行結構,以實現對3個不同量子邊帶模式的3組原始隨機比特的Toeplitz哈希后處理。在外層,3個子熵源的Toeplitz提取器是獨立構建的,并且同時運行;在內層,對于每個量子邊帶模式, Toeplitz實時后處理都是在流水線算法中實現的,FPGA中各個數據信號隨時鐘信號進行并行的硬件處理。3個通道的ADC采集和FPGA中的實時并行處理由同一個240 MHz的時鐘控制,隨后將3個通道產生的隨機數每16位交替混合,并實時輸出。

本文設計了后處理過程中每一通道的信號時序,如圖2所示,m×n的Toeplitz矩陣后處理,每處理n位原始隨機數需要n/k個時鐘周期。在其中的第i個時鐘周期,FPGA需要完成以下工作:從m+n-1位的種子中選出m+k-1位(從第(i-1)×k+1位到第m+i-1位)構造出一個子矩陣“sub_tpz”;從ADC讀入16位原始隨機數作為一個子序列“ADC Input”;利用構造出的子矩陣對讀入的子序列進行處理,并將得到的處理結果存入寄存器“sum_reg”中。CLK為控制時鐘,n/k個時鐘周期過后,FPGA完成所有子矩陣與子序列的處理,所得到的n/k個結果(m位向量)被全部保存,然后將所有m位向量按位異或就能得到整個矩陣的計算結果“ans”。

圖2 單路后處理中的信號時序設計

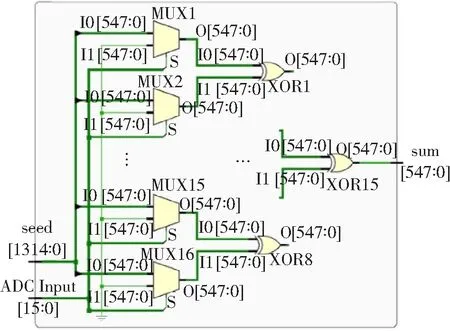

圖3所示為簡化的單個通道子矩陣后處理中的寄存器傳輸級(Register-Transfer Level, RTL)電路。圖中,XOR為異或門;MUX為選通器(Multiplexer),當其S端輸入為“1”時,輸出端O的值等于I0;當S端輸入為“0”時,輸出端O的值等于I1。每一個MUX的I0輸入端為Toeplitz子矩陣的一列,矩陣元素從種子中選出,I1輸入端為0,每一個MUX的S輸入端對應ADC輸入的一位。總共16個MUX的輸出經過4級異或門按位異或以得到子矩陣處理的結果。

圖3 子矩陣后處理的RTL電路

2 實驗結果

在ISE中完成了后處理過程的設定后,使用自帶的仿真模塊對FPGA內部信號進行了行為仿真。如圖4所示,本文以其中一個通道的仿真結果為例,圖4(a)所示為后處理開始后幾個時鐘周期內Toeplitz子矩陣的生成情況,該通道子矩陣規模為548×16,sub_tpzj為子矩陣的第j列,該仿真結果可用于判斷子矩陣生成邏輯的正確性。圖4(b)所示為子矩陣運算的仿真結果。“CLK”為用上升沿控制其他信號變化的時鐘信號,其余信號顯示每4個比特轉化為一位16進制。仿真時使用已采集的隨機數代替了ADC的輸入“ADC_input1”,每個時鐘周期讀取16位比特;“sum_reg”為每個Toeplitz子矩陣處理同時鐘周期“ADC_input1”所得結果;“ans”為整個548×756的Toeplitz矩陣處理756位輸入所得結果,整個矩陣處理一次需要48個時鐘周期。由于在一次矩陣計算中需要完成所有子矩陣運算才能得到最終結果,后處理開始后需要運行48個時鐘周期才能開始得到結果(“ans”的前48個時鐘周期),然而這并不影響后處理的性能和實時性。

圖4 ISE軟件的仿真結果

理想的隨機數序列沒有自相關性。對經過多路并行高速實時后處理的隨機序列進行了自相關測試,測試時將每個比特作為一個樣本,總比特個數為107。測試結果如圖5所示,隨機數經過后處理后,其自相關系數明顯處于較低水平,且維持在10-4~10-7量級,符合高質量真隨機數的特征。

圖5 經后處理后隨機比特的自相關測試

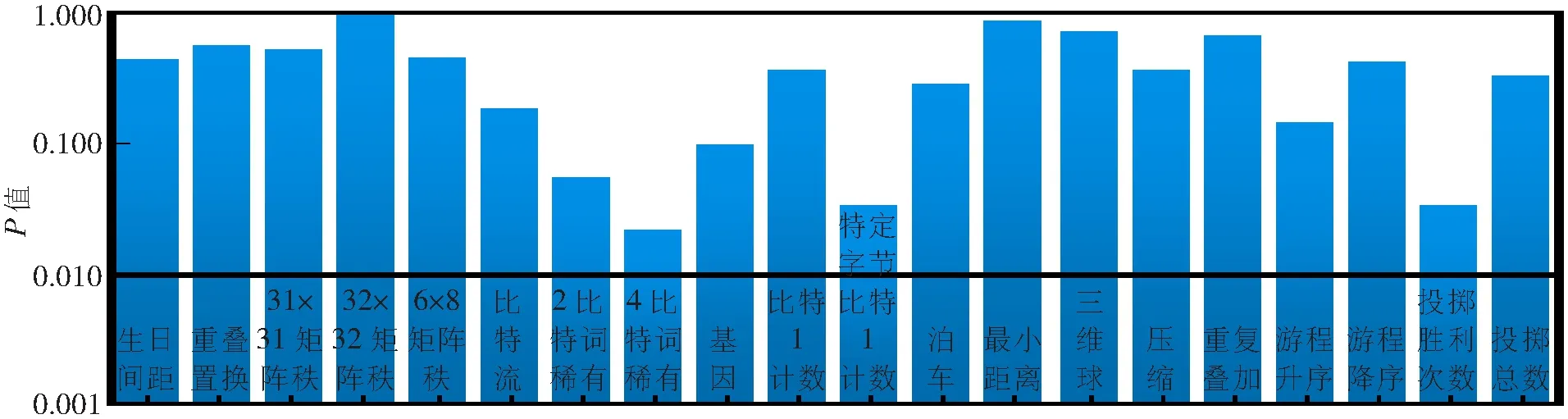

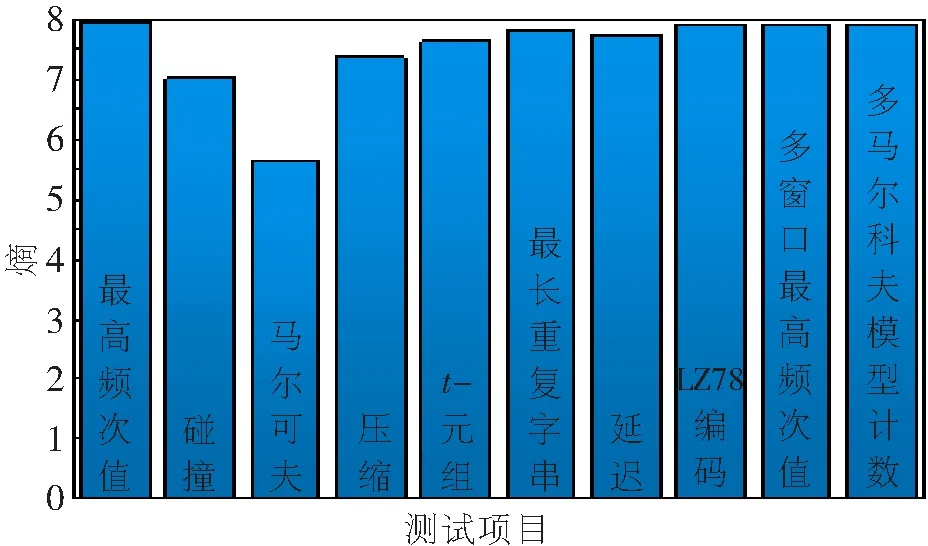

隨后本文對后處理產生的隨機數進行了Diehard測試。Diehard測試是一個測試隨機數生成質量的測試包,其由George Marsaglia發布[17],是目前使用最廣泛的隨機數測試軟件之一。相較于ENT偽隨機數測試和美國國家標準與技術研究院(National Institute of Standards and Technology,NIST)數據測試包,Diehard測試是一個更嚴格的隨機性統計測試套件。本文測試時設置顯著性水平α=0.01,測試的樣本為1 Gbit/s大小隨機數bin文件。當Diehard測試的每項測試結果P值滿足0.01 圖6 實時后處理后對生成量子隨機數的Diehard統計測試 此外,熵是隨機數發生器的安全性和質量的重要評估標準。NIST的800-90系列建議書[18]給出了在隨機數生成過程中10種不同于最小熵評估的熵評估方法,利用該項熵評估標準對本文實驗系統的熵源進行進一步評測。將測試包中的非獨立同分布(Independent Identically Distribution,IID)測試應用于每一個通道的原始比特串,完成后處理前的熵源評測,3個通道熵值測試結果的平均值如圖7所示。本文工作中樣本空間的大小為216,根據測試要求,可采用低8位來進行熵值測試,所產生的最小熵取自所有測試項的最小值,即每8位為5.65。表明后處理前的熵源具有較好的隨機性,熵源原始的隨機性和質量得到了評測和驗證。 圖7 后處理前對熵源的NIST熵值評估測試 本文實現了QRNG中多通道并行實時后處理,從熵源中提取了3個不重疊的量子邊頻帶模式,并分別分析了各個邊帶的最小熵。在性能中等的FPGA中設計構建了信息論可證的多通道并行Toeplitz硬件后處理,并充分利用了FPGA的并行處理優勢和硬件資源。本文利用NIST 800-90B評估套件測試了后處理前熵源的熵含量,同時分析測試了后處理之后生成量子隨機數的自相關性,生成的量子隨機數通過了Diehard統計測試。 通過上述量子隨機數產生及硬件后處理方法,實現了不同量子邊帶模式的3組原始隨機比特的Toeplitz實時后處理,量子隨機數實時生成速率為8.24 Gbit/s。3通道Toeplitz實時后處理占用了約61%的FPGA邏輯資源。這項工作為量子隨機數的后處理提供了一種高速安全的方法,在高速量子隨機數實時產生中有著重要應用。

3 結束語