基于信號完整性的板間互連設計

張玉鈴,王淑娟

[摘? ? 要]在由現場可更換模塊組成的電子設備中,board to board互連的信號完整性問題舉足輕重。基于信號完整性,搭建互連鏈路,進行SRIO總線傳輸,速率10.3125 Gbps,經由兩組連接器及20 inch的有損傳輸線,對信號質量指標進行核算,對全鏈路進行仿真驗證。

[關鍵詞]信號完整性;SRIO;鏈路損耗

[中圖分類號]TP368.1 [文獻標志碼]A [文章編號]2095–6487(2021)12–00–02

Design of Interconnection between Boards Based on Signal Integrity

Zhang Yu-ling,Wang Shu-juan

[Abstract]In the electronic equipment composed of field replaceable modules, the signal integrity of board to board interconnection is very important. Based on the signal integrity, the interconnection link is built for sRIO bus transmission at the rate of 10.3125 gbps. The signal quality index is calculated through two groups of connectors and 20 Inch lossy transmission line, and the whole link is simulated and verified.

[Keywords]signal integrity; SRIO; link loss

現場可更換模塊是系統安裝上和功能上相對獨立的各類通用單元的總稱,具有標準的尺寸和接口,將傳統的三級維護簡化為二級維護。隨著現場可更換模塊的普遍應用和高速串行總線對并行總線的取代,通信速率日益提升,總線的應用也從chip to chip拓展至board to board,在此應用層級上的信號完整性問題,直接制約了構成設備的各模塊之間的交互,是模塊間通信的核心技術所在。

1 鏈路架構

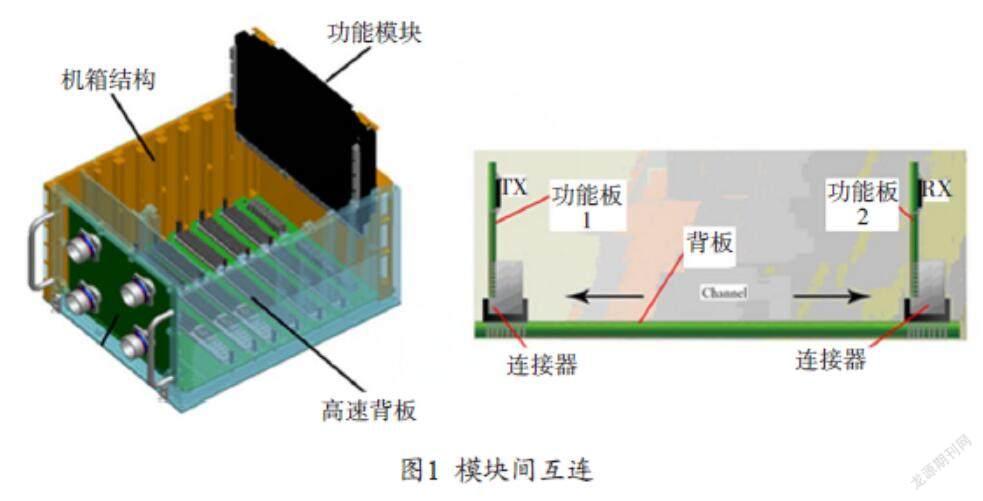

設計目標為基于ASAAC架構的SRIO總線鏈路,單通道最高速率為10.3125 Gbps。SRIO總線是目前高性能嵌入式系統最常用的系統總線之一,可實現board to board互連,速率支持5 Gbps、6.25 Gbps、10.3125 Gbps,信號上升沿達ps級別。選取包含處理器的子板1、子板2及背板組成的鏈路,進行SRIO總線互連,如圖1所示。

1.1 處理器

選取數字信號處理器負責數據的接收、比特譯碼和解串降速。根據資源的使用情況,選取XC7K325T-2FFG900I,為Xilinx公司的FPGA器件,特性參數如下:

326 080個邏輯單元,16 020Kb RAM,10個Bank,16通道高速GTX,速率最高可達12.5 Gbps,500個user I/O。

1.2 連接器

針對目標10.3125Gbps SRIO設計,選用LRMT1-A288-B288-T1、LRMT1-A288-B288-Z1連接器。插頭采用不同種類的金手指印制板接觸件,插座采用彈性插孔接觸件,結構如圖2所示。

2 信號完整性指標分配

整條鏈路可以分為3個部分:發送端、傳輸通道以及接收端。發送端和接收端包含發送芯片、接收芯片以及通信相關的外圍器件,如信號耦合電容等。傳輸通道包含有損傳輸線、過孔、連接器等,共同形成一條長度20 inch的阻抗控制傳輸線。

2.1 SRIO協議指標

為了實現數據的正常通信,SRIO規范中對發送端信號、接收端信號以及傳輸通道的損耗都有非常嚴格的指標要求。

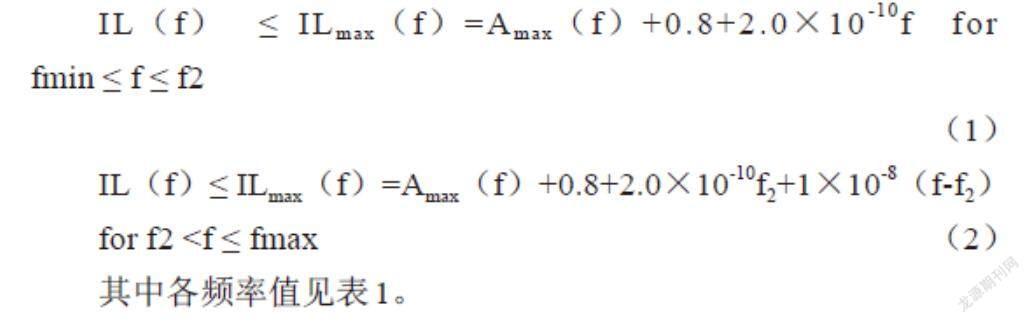

根據IEEE 802.3-2012 Section 69B.4.3,整個鏈路總的插入損耗Insertion Loss(IL)為:

IL(f)≤ILmax(f)=Amax(f)+0.8+2.0×10-10f for fmin≤f≤f2

(1)

IL(f)≤ILmax(f)=Amax(f)+0.8+2.0×10-10f2+1×10-8(f-f2)

for f2 <f≤fmax (2)

其中各頻率值見表1。

其中,Amax(f)根據IEEE 802.3-2012 Section 69B.4.2為:

Amax(f)=20log10(e)×(b1√f+b2f+b3f2+b4f3) for f1≤f≤f2

(3)

其中各系數見表2。

2.2 驅動端

處理器驅動端輸出差分信號。理想情況下,兩個信號邊沿對齊、翻轉方向相反。實際上,晶體管的開啟與關斷需要時間,信號以一定的上升沿來跳變。差分對的單端峰值電壓擺幅為500 mVpp,差分輸出電壓范圍在500~-500 mV,峰峰差分電壓為1000 mVppd。

2.3 傳輸線

在高速信號傳輸過程中,串擾、反射、導線與介質損耗都會造成信號的畸變與衰減。串擾受線間距影響較大,合理設置走線間距可以有效降低串擾水平。反射主要由阻抗突變引起,要降低信號反射,需要對通道各部分進行嚴格的阻抗控制設計。

損耗包含導線損耗和介質材料損耗,導線損耗與線阻成正比,相同介質條件下受走線寬度影響較大;介質損耗會隨著頻率的增加而迅速上升。因此,頻率較高時,介質損耗處于主導地位,選擇合適的絕緣介質十分重要。

選取松下M6材料,介電常數3.6,損耗系數0.002,線寬5 mil間距7 mil的帶狀線設計,仿真在10 G速率下,10 inch傳輸線插入損耗約為3.6 dB@5 GHz。

2.4 焊盤

傳輸通道上包含至少4組焊盤,當數據速率達到10.3125 Gbps時,焊盤的阻抗突變與損耗特性會對通道的傳輸性能產生重大影響。

殘樁(Stub)是設計中需要考慮的關鍵因素,“短樁”長度越長,諧振頻率點的頻率越低,引起的插入損耗越大,越容易影響高速背板產品的傳輸性能。在保證連接器和背板有效壓合的前提下,通過背鉆技術,減小“短樁”長度,從而減少了背板過孔的天線輻射效應,降低插入損耗。

2.5 連接器

LRMT1-A288-B288-T1、LRMT1-A288-B288-Z1連接器插頭采用不同種類的金手指印制板接觸件,插座采用彈性插孔接觸件,對連接器結構建模仿真得到連接器插入損耗約為-1.5 dB@5 GHz。

3 全鏈路仿真

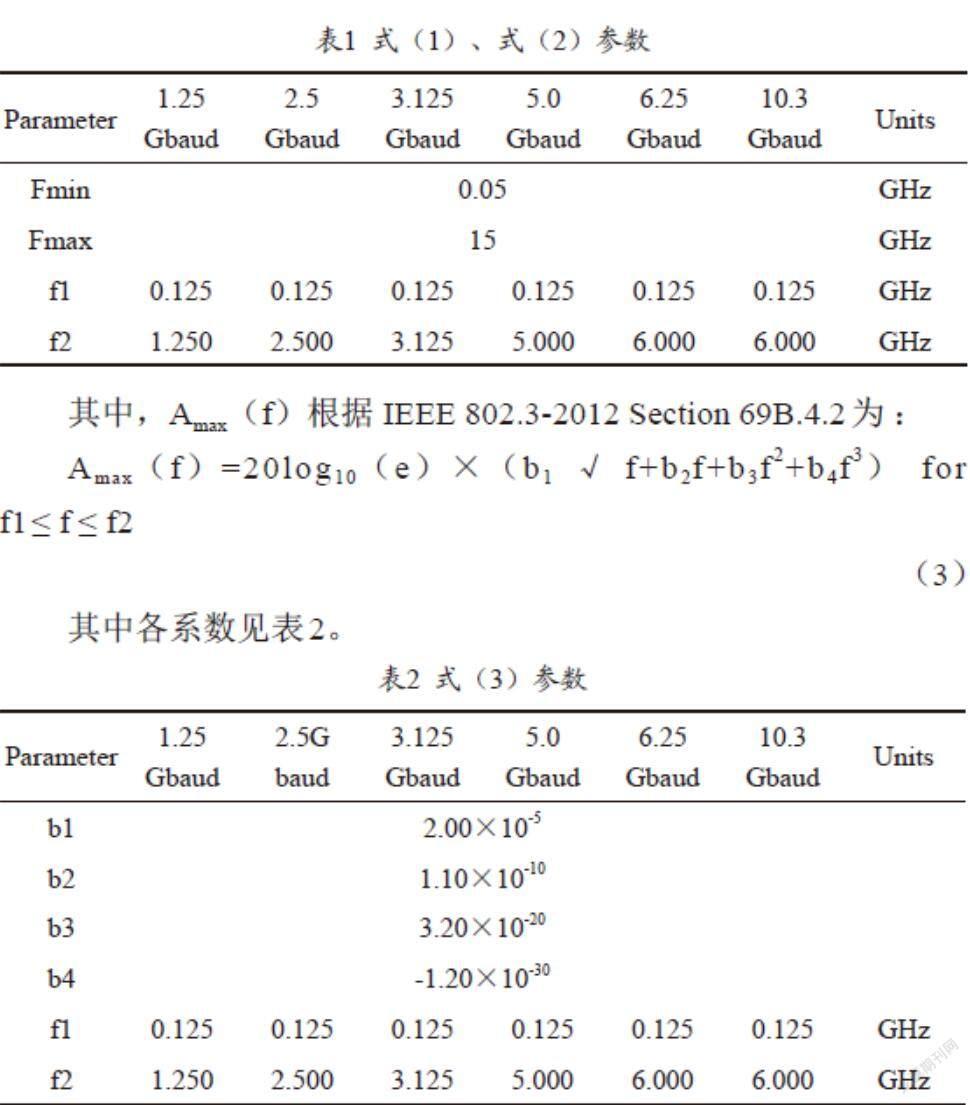

對全鏈路(線長約20 inch)進行仿真,得出插入損耗如圖3所示 。

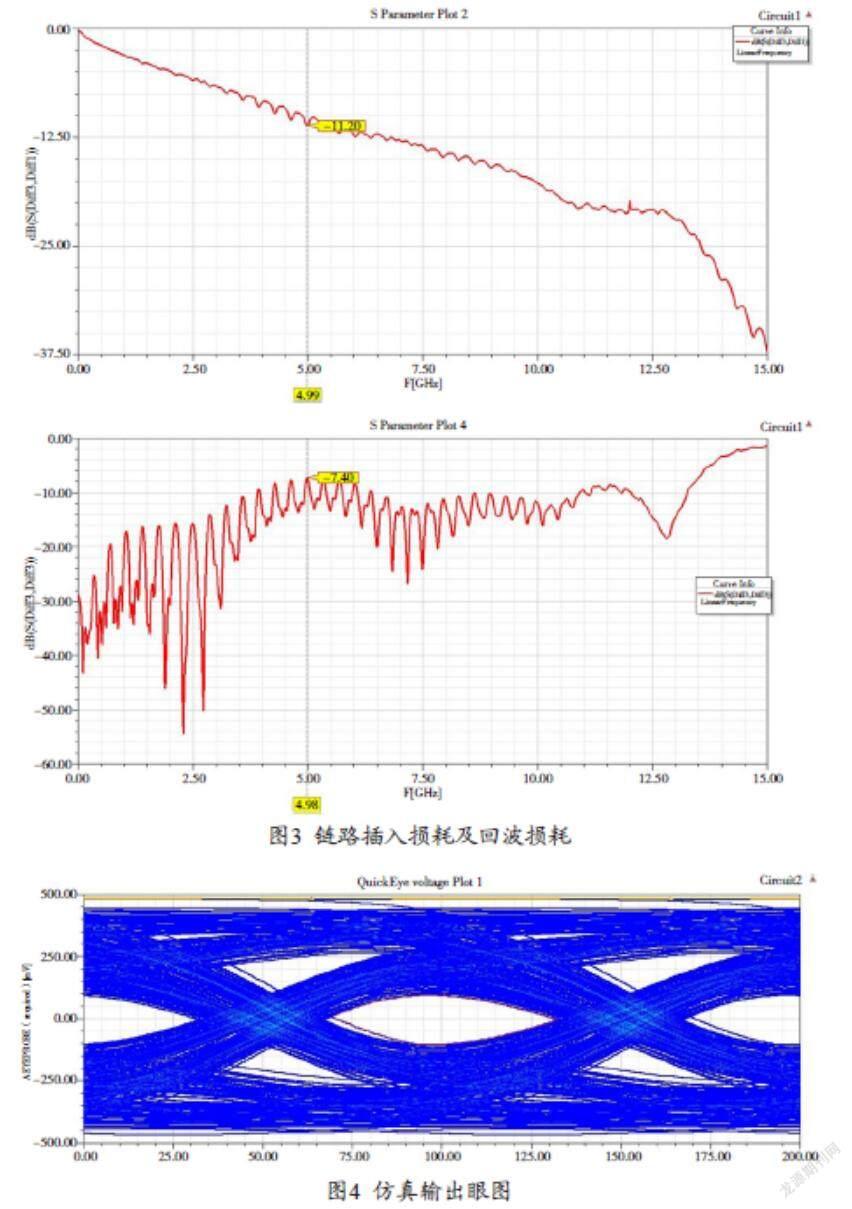

圖中插損為-11.2dB,大于SRIO規范中所要求的Insert Loss≥-21 dB;回損為-7.48 dB,優于SRIO規范中所要求的-5 dB。眼圖仿真結果如圖4所示。

圖4中眼高為101 mV,大于SRIO規范中所要求的Vdiff≥42.5 mV。

4 總結

隨著半導體工藝的不斷發展,高速互連通信的發展也是日新月異,高速傳輸技術將會得到進一步提高。本文給出的基于ASAAC結構的SRIO總線傳輸鏈路,采用標準化設計,可以在一定程度上滿足通用化需求。通過對鏈路指標的分解,可以指導board to board互連鏈路的信號完整性設計。

參考文獻

[1] 李春來,顧軍,王寧.基于ETH規范的高速背板性能仿真與優化設計[J].艦船電子對抗,2018,41(2):107-111.

[2] 于爭.信號完整性揭秘[M].北京:機械工業出版社,2013.

[3] 羿昌宇,祖翔宇.大規模高速背板的信號完整性設計與仿真[J].航空電子技術,2013,44(4):1-6.

[4] 李彥,吳培明,寇小明.高速串行RapidIO總線背板信號完整性仿真研究[J].魚雷技術,2011,19(3):167-171.

[5] 曹勁.RapidIO背板信號完整性測試方法[J].電訊技術,2011,51(1):18-22.