面向窄節距倒裝互連的預成型底部填充技術*

王 瑾, 石修瑀, 王 謙, , 蔡 堅, , 賈松良

(1.清華大學微電子學研究所, 北京 100084; 2.北京信息科學與技術國家研究中心, 北京 100084)

1 引言

傳統的底部填充技術是在完成倒裝芯片互連之后進行的, 因此也被稱為組裝后底部填充技術(Post-assembly Underfill)[1-2]。 應用最為廣泛的是毛細底部填充(CUF)和模塑底部填充(MUF)。 近年來隨著系統集成度不斷提高,倒裝芯片上凸點的尺寸和節距也變得越來越小,凸點節距小于100 μm,甚至不大于10 μm, 傳統的組裝后底部填充技術由于是在凸點互連之后才進行底部填充的,常常會出現凸點間填充不完全到位、產生孔洞等缺陷,使封裝互連的可靠性降低[3]。

為了適應倒裝芯片窄節距互連的填充需求,產業界提出了一種新型的預成型底部填充技術(Preassembly Underfill)[4-5]。這種方法既能簡化工藝,又能對窄節距互連(小于100 μm)進行良好的底部填充。此外,研究機構還提出了一些方法對預成型底部填料的性能進行改進, 從而實現低熱膨脹系數(約20×10-6/℃)、低粘度(小于20 Pa·s)以及高熱導率[大于1 W·(m·K)-1]等優良性能[6-7],進一步提高了預成型底部填充的可靠性。

本文將聚焦于窄節距倒裝芯片互連中的預成型底部填充技術, 介紹該技術的工藝流程以及材料特性,并針對其在實際生產中遇到的問題,總結目前已有的解決方案并預測這種技術未來的發展趨勢。

2 預成型底部填充技術

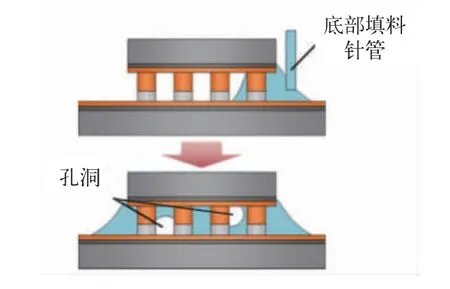

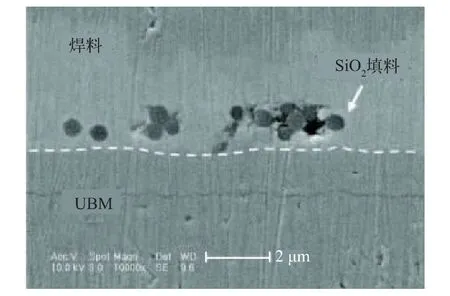

傳統的組裝后底部填充技術主要適用于大節距凸點互連中, 而對于節距小于100 μm 的倒裝芯片凸點互連,如仍采用這種技術,易在填充時產生大量孔洞,如圖1 所示。因此,對于窄節距倒裝芯片互連,目前產業界多采用預成型底部填充技術。

圖1 組裝后底部填充技術在應用于窄節距互連時產生的孔洞[3]

預成型倒裝芯片底部填充技術是指底部填料在芯片互連之前就被施加在芯片或基板上,在后續的回流或熱壓鍵合過程中,芯片凸點互連與底部填充固化同時完成。 該技術主要可以歸納為2 種方法: 非流動底部填充(NUF)和圓片級底部填充(WLUF)。

2.1 非流動底部填充

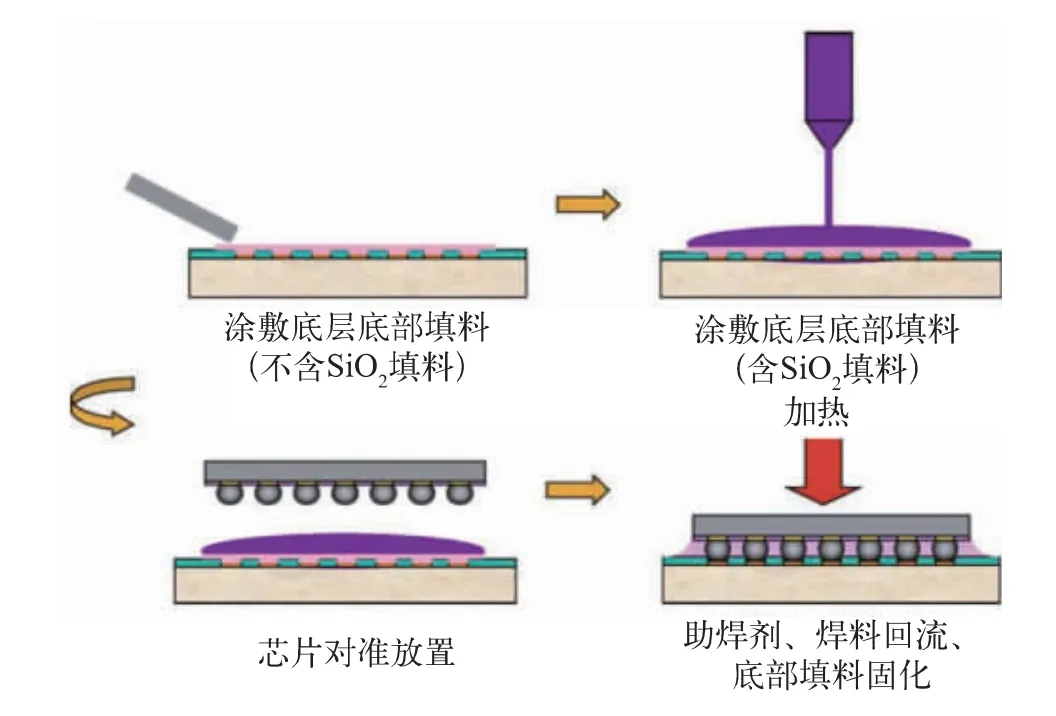

美國佐治亞理工學院于1996 年首先提出了非流動底部填充技術[8]并成功應用于無鉛C4 凸點的倒裝芯片組裝[9],具體工藝流程如圖2 所示[2]。 該技術省去了單獨的助焊劑涂敷、底部填料的毛細流動注入和助焊劑清洗步驟,將焊料凸點回流和底部填充劑固化結合為一個步驟,從而既消除了底部填充時易產生的孔洞又提高了底部填充工藝的生產效率。

圖2 非流動底部填充工藝流程[2]

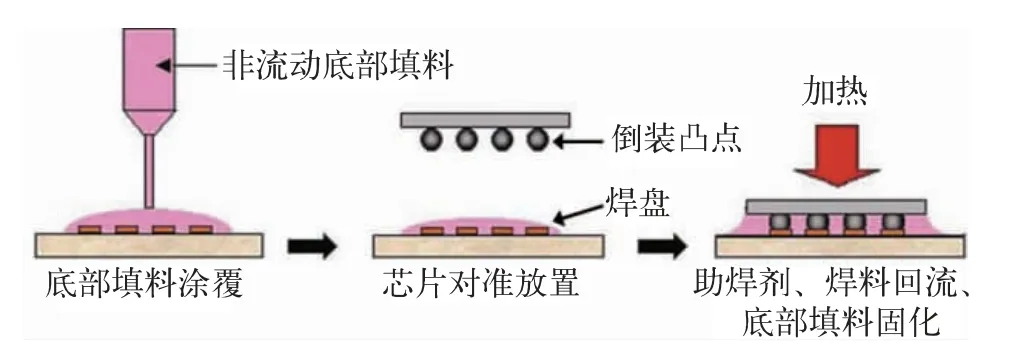

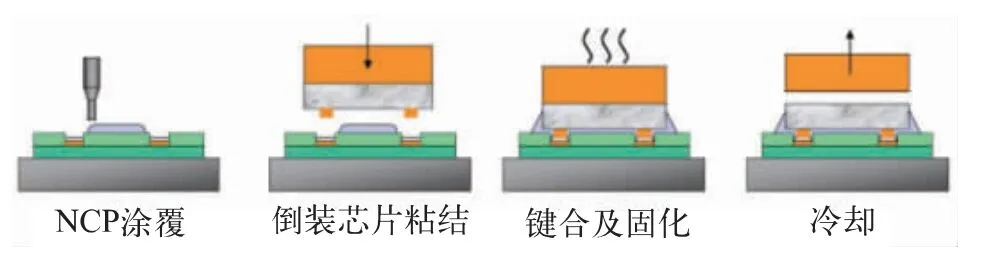

近年來,針對倒裝芯片窄節距凸點的非流動底部填充技術也取得了發展。AMKOR[5]首先提出了利用非導電漿料(NCP)用作非流動底部填料,在實現凸點互連的同時完成NCP 的固化,其工藝流程如圖3 所示。

圖3 面向窄節距凸點互連的NCP 非流動底部填充技術工藝流程[5]

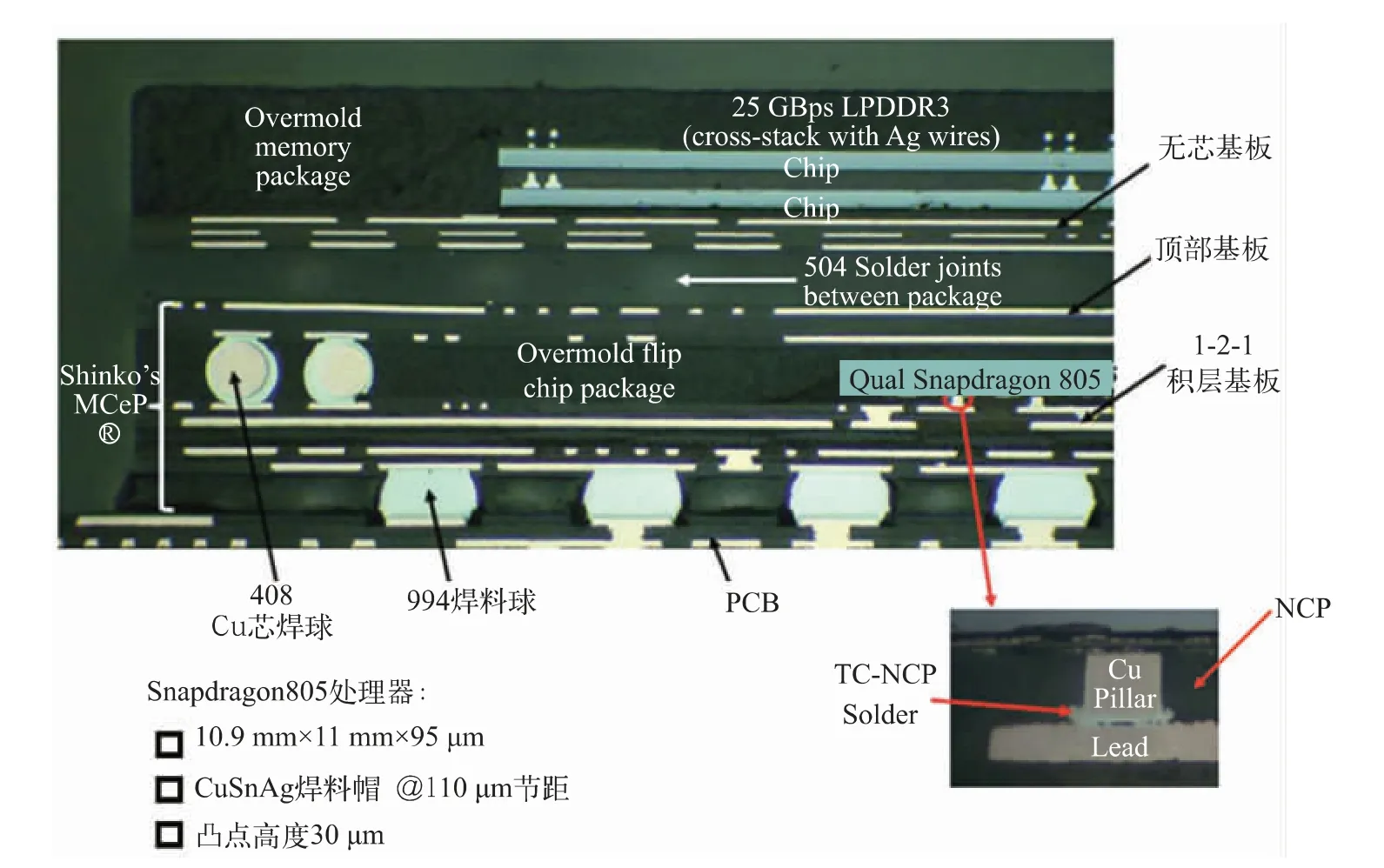

早期針對大節距凸點(圖2)的非流動底部填充技術是通過回流來實現凸點互連與底部填料固化的,為了避免底部填料中的SiO2顆粒鑲嵌在互連界面影響接頭的形成與電互連的可靠性,早期的底部填料中不含或只含很少的SiO2填料。 在基于NCP 的非流動底部填充中(圖3),由于在鍵合過程中施加壓力可以減少SiO2顆粒在互連界面的鑲嵌, 因此NCP 材料中含有SiO2填料, 同時有研究表明隨著NCP 中SiO2填料質量百分比的增加,NCP 材料的熱膨脹系數(CTE)會減小,而粘度和楊氏模量會增加,組裝的可靠性也隨SiO2填料的增加而有所提高[10]。目前NCP 非流動底部填充技術已經成功應用于Samsung 手機處理器的封裝中,如圖4 所示。

圖4 應用于Samsung 手機處理器中的NCP 非流動底部填充技術[11]

2.2 圓片級底部填充

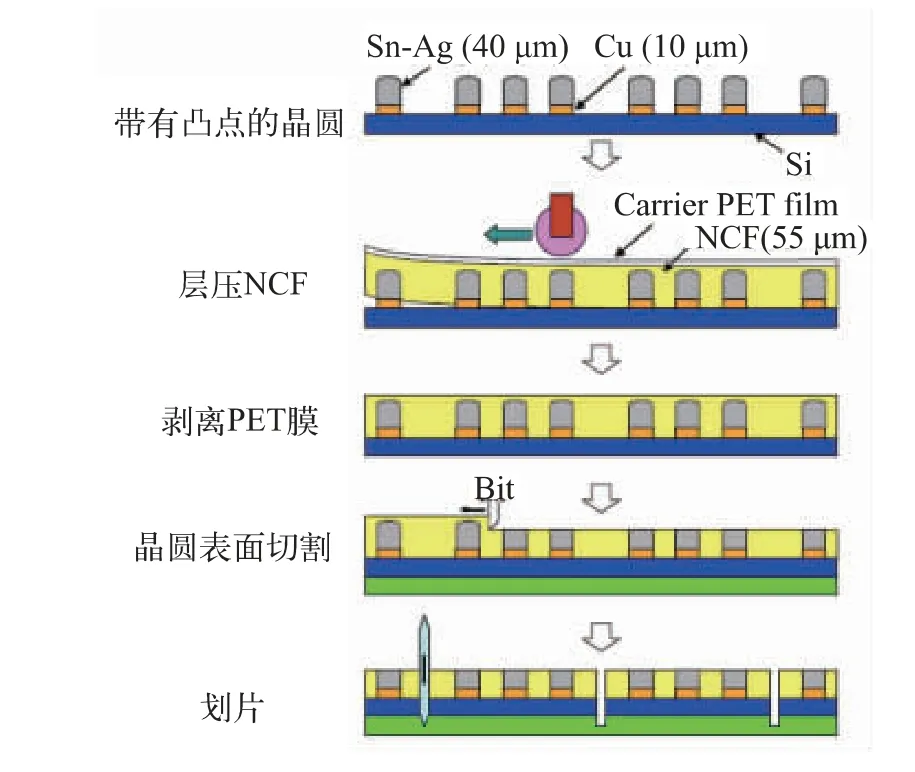

為了進一步提高生產效率,產業界在非流動底部填充技術的基礎上提出了圓片級底部填充技術。 通過旋涂或層壓的方式將底部填料施加在整個圓片上,然后將圓片劃片切成單顆的芯片,最后通過回流或熱壓鍵合來實現芯片與芯片/基板之間的凸點互連與底部填料固化。

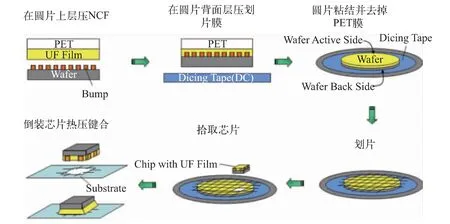

目前應用較為廣泛的圓片級底部填料是非導電薄膜(NCF),NCF 是以膜的形式存在,可以通過夾在聚對苯二甲酸乙二醇酯(PET)之類的塑料薄膜中以卷材形式使用。這種特性有利于NCF 在圓片級底部填充工藝中的應用,其工藝流程如圖5 所示[12],首先在圓片正面真空層壓NCF,然后在圓片背面貼劃片膜,通過劃片將圓片切成單顆芯片,最后倒裝芯片經過熱壓鍵合實現互連與固化成型。這種基于NCF 的圓片級底部填充技術多應用于節距為40~80 μm 的微凸點互連中。

圖5 NCF 圓片級底部填充工藝流程[12]

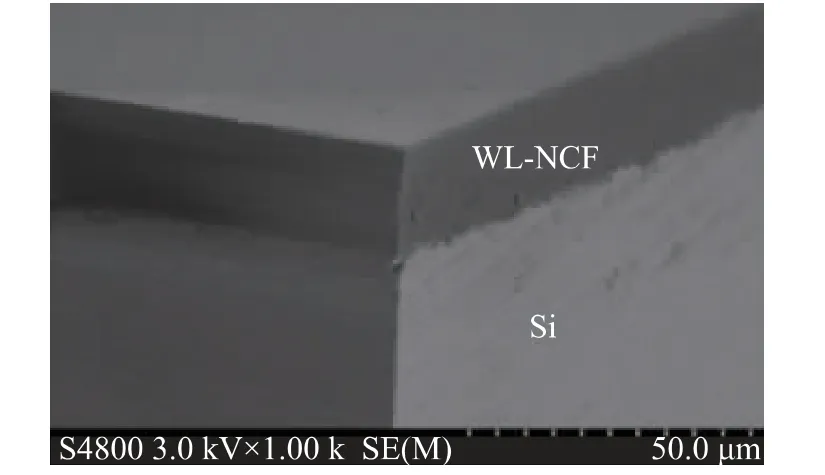

圓片級底部填充工藝成功的關鍵是要保證在劃片之前,圓片上的底部填料處于半固化狀態(B-Stage,或稱B-階), 具有足夠的機械強度和穩定性以滿足后續劃片、 儲存等的需求, 圖6 為劃片后的芯片邊緣照片,沒有發現底部填料的變形[13]。 同時處于B-階的底部填料也具有“ 可回流性”,即具有熔化和流動的能力,從而在后續互連過程中焊料帽能夠浸潤焊盤并形成焊點。 因此,對于成功的圓片級底部填充而言,保證底部填料處于B- 階以及控制后續的熱壓固化工藝是至關重要的。

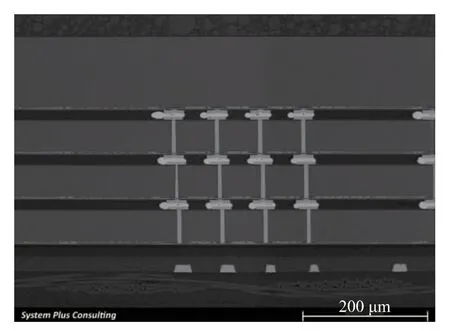

同為預成型底部填充,NCF 的生產效率要比NCP高很多,因為NCF 可以在整個圓片上進行層壓;同時NCF 工藝也較NCP 更好控制, 如熱壓過程中NCP 的溢出較難控制,限制了其在三維封裝方面的應用。 但NCF 的缺點是流動性較NCP 差, 導致互連界面殘留的底部填料較多,降低了接頭的電互連可靠性;同時它不能靈活應對具有不同凸點高度的芯片,只能考慮配以不同厚度的膜。 目前,Sanyo[14]、Hitachi[15-16]、Tohoku[17-18]、DOW[19]、Hynix[20]、KAIST/Samsung[21-22]、Amkor/Qualcomm[23]和Toray[24-26]等都對基于NCF 的圓片級底部填充技術進行了研究, 并應用于2.5D/3D 集成中。 圖7 為Samsung 在其動態隨機存儲器中應用NCF 底部填充技術的實例[15,27],它實現了基于硅通孔(TSV)的4 層存儲芯片的互連與底部填充。

圖6 涂有NCF 圓片在劃片后芯片邊緣的SEM 照片[13]

圖7 Samsung 動態隨機存儲器中應用NCF 底部填充實例[27]

NCP 和NCF 材料主要由基體膠、稀釋劑、增韌劑和其他添加劑組成。 基體膠主要有環氧樹脂、酚醛樹脂、聚酰亞胺及熱塑性塑料等;稀釋劑通常主要包括醇類、酯類稀釋劑等;增韌劑包括低分子液體改性劑等非反應性增韌劑。 NCP 材料的主要供應商有Henkel、Namics、Nagase、Hitachi、Panasonic 等,NCF 的供應商有Henkel、Hitachi、Toray、Nitto Denko、Namics、Sumitomo 等。

3 預成型底部填充技術的最新進展

目前, 利用NCP/NCF 作為底部填料的預成型底部填充技術在窄節距倒裝互連的三維堆疊存儲芯片以及圖像傳感器芯片等方面都得到了較為廣泛的研究與應用,但是在面向大規模量產和未來進一步的窄節距倒裝互連時還存在一定的技術挑戰,未來還需要在提高量產生產效率、提升電互連的可靠性以及開發納米級高熱導率填料等方向繼續發展。

3.1 提高量產生產效率

預成型底部填充技術多用于節距小于100 μm 的凸點互連, 與傳統的C4 凸點大批量回流之后進行底部填充相比,一般一次熱壓過程只能完成一個芯片的鍵合與底部填充,因此整體的生產效率較低。

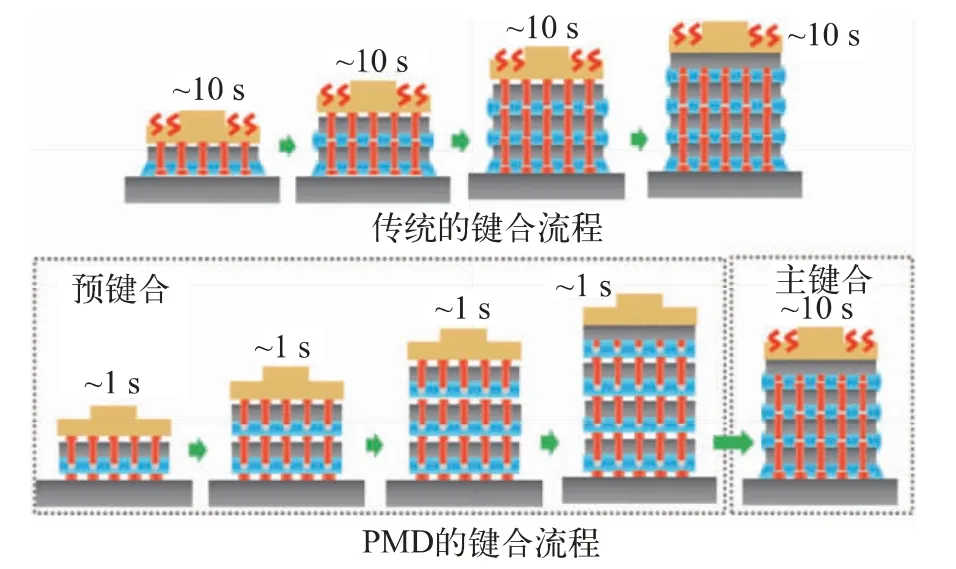

為了提高生產效率,TORAY[24]提出了將熱壓鍵合過程分為2 個過程進行:第一步是預鍵合,主要實現芯片的拾取和放置;第二步是主鍵合,通過一次熱壓過程完成多個芯片在基板上的鍵合。 這種將預鍵合和主鍵合分步(PMD)進行的方法能夠較好地提高生產效率。PMD 工藝流程如圖8(a)所示。它由A 和B 的2 個并行工序組成, 通過分步預鍵合A 和主鍵合B 的方法, 壓頭的溫度在整個過程中始終保持恒定, 如圖8(b)所示,省去了壓頭升溫和降溫的時間,從而提高了生產效率。 此外,預先施加的NCF 也能夠防止在從過程A 到過程B 的基板傳輸過程中芯片的移動。 圖8(d)展示了鍵合后的互連界面截面圖。

TORAY 這種分步鍵合的方法也可以用在芯片堆疊中以提高生產效率,如圖9 所示[26,28]。 圖10 為用這種方法鍵合后的三維芯片堆疊截面示意圖,可以看到能夠實現良好的三維堆疊互連。

3.2 提高電互連可靠性

預成型底部填充技術在實際應用中的另一個主要問題是凸點處的電互連可靠性。 由于底部填料在凸點互連之前就已經鋪展在芯片載體上了,因此在凸點互連過程中,底部填料中的SiO2填料很容易殘留在凸點之間,如圖11 所示[10],從而降低互連的導電性能和載流能力,影響在高溫/高濕或熱循環下的可靠性。

針對以上問題,很多公司及研究機構都提出了相應的解決方案,主要包括雙層工藝、兩步工藝、混合鍵合以及自組裝技術等。

佐治亞理工學院[29]、HITACHI[30]等提出了使用兩層非流動底部填料的方法。 雙層底部填充方法工藝流程如圖12 所示: 首先在基板上施加一層底部填料,這種材料具有相對較高的粘度且不含SiO2填料,然后在其上面再滴涂一層含有SiO2的底部填料,最后將芯片放置在基板上進行鍵合,實現凸點互連與底部填料的固化。已有文獻報道用含65%(質量分數)的SiO2填料的頂層底部填料可以實現100%的互連良率[29]。使用這種雙層工藝雖然可以避免SiO2顆粒的嵌入,但是在實際工藝過程中,需要對各工藝參數以及材料參數進行精確的控制,如底層材料的厚度和粘度對焊料凸點的潤濕性起至關重要的作用,鍵合過程中的壓力以及溫度直接影響了2 種材料的融合固化以及焊料凸點的互連等,因此實際生產中工藝窗口很窄。 此外,由于該工藝中使用了2 種底部填料, 大大增加了工藝步驟和工藝成本。

圖8 基于NCF 底部填充PMD 的鍵合工藝[24]

圖9 基于NCF 底部填充的分步鍵合方法應用于芯片堆疊中[26]

圖10 三維芯片堆疊鍵合截面圖[26]

圖11 底部填料中的SiO2 填料殘留在凸點的鍵合界面[10]

圖12 雙層底部填充方法[29]

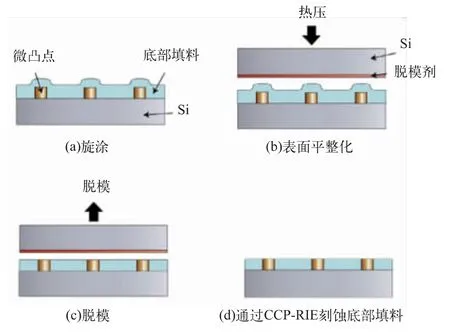

TORAY[32]、IMEC[33-36]等還提出了2 步工藝的方法解決互連可靠性問題。 即在圓片上施加NCF 之后,通過化學機械拋光(CMP)、快速切割等方法,對凸點和底部填料的表面進行處理, 一方面實現表面的平坦化,另一方面也可以去除凸點表面的底部填料,從而解決SiO2填料的嵌入問題。利用快速切割的方式去除凸點上的底部填料工藝流程如圖13 所示[32]。 圖14 展示了表面處理后的效果[33],可以看到CMP 之后凸點能夠完全暴露出來。 該方法的缺點是增加了工藝成本和工藝難度。 在化學機械拋光中,需要選擇合適的拋光液,從而同時實現Cu/Sn 凸點與底部填料的平坦化。研究表明, 對于嵌入底部填料中Sn 凸點的化學機械拋光,其對拋光液的酸堿性有很強的依賴性,選擇酸性-中性的拋光液能夠實現更加平坦的表面[33]。此外,利用快速切割的方法,容易在凸點及底部填料表面產生比較大的劃痕。 為了簡化工藝、降低成本,早稻田大學[37]提出了一種更為簡單的結合等離子刻蝕的熱壓平整化工藝,如圖15 所示,也可以達到預期的效果。

圖13 利用快速切割的方式去除凸點上的底部填料[32]

圖14 CMP 后得到的凸點/ 底部填料表面SEM 照片[33]

為了去除凸點表面的底部填料,提出了采用光敏光刻膠作為底部填料的方法[38-40]。 在完成圓片上的凸點制作之后, 先旋涂一層光敏光刻膠作為底部填料,然后利用光刻技術對光刻膠進行圖形化處理,去除凸點上的光刻膠,工藝流程如圖16 所示[38]。 由于凸點鍵合與光刻膠固化同時實現, 該方法被稱為混合鍵合。常用的光敏光刻膠有BCB、PI、SU-8 等。目前有許多研究機構都對混合鍵合技術進行了研究。 大連理工大學利用Cu-SnAg 固液擴散鍵合技術來實現凸點互連,并采用B-階干膜作為光敏光刻膠來實現底部填充,其鍵合工藝參數(溫度/ 時間/ 壓力) 為240 ℃/10 min/10 kN,最終通過控制凸點厚度與有機物厚度同時實現了凸點互連以及光刻膠的固化[39]。 臺灣交通大學也對混合鍵合進行了研究,在利用Cu-Sn 固液擴散鍵合技術實現凸點互連的基礎上,對比優化了使用不同光敏光刻膠(PI、SU-8 以及BCB)對應的最佳鍵合工藝參數[38]。清華大學采用了獨特的非對稱混合鍵合結構,即只在頂部圓片上進行光刻膠的旋涂、光刻等,而不對底部圓片進行任何工藝操作,從而保護了底部圓片上的器件結構,使其適用于MEMS 圓片鍵合中[40]。 但由于光刻膠中一般不含SiO2顆粒, 其CTE 值較常規底部填料高,因此使用混合鍵合方法對封裝體整體可靠性的影響還需深入研究。

圖15 熱壓-等離子刻蝕方法去除凸點表面的底部填料[37]

圖16 凸點/ 光刻膠混合鍵合工藝流程[38]

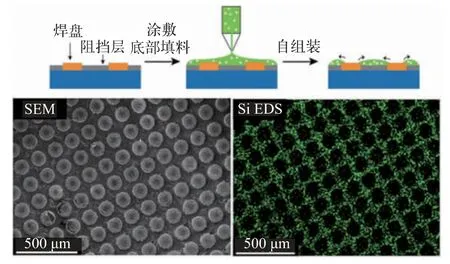

佐治亞理工學院WONG 等[41]還提出了一種新的自組裝技術來解決SiO2顆粒的嵌入問題,通過對焊盤及鈍化層的表面預處理,使銅焊盤表面疏水而鈍化層Si3N4表面親水,從而實現底部填料的自組裝,如圖17所示。 研究結果表明,表面處理后的焊盤和鈍化層表面的水接觸角差值可以達到119.9°(或底部填料接觸角差值可以達到91.6°),從而實現了自組裝,解決了凸點互連中底部填料嵌入的問題。 圖17 通過掃描電鏡及能譜測試也展示了表面處理后銅焊盤上幾乎沒有SiO2顆粒,成功地實現了底部填料的自組裝。 文中還提出該自組裝技術能夠與市場上的商業底部填充劑相容。

圖17 底部填料在銅焊盤及阻擋層表面的自組裝效應[41]

3.3 開發納米級高熱導率填料

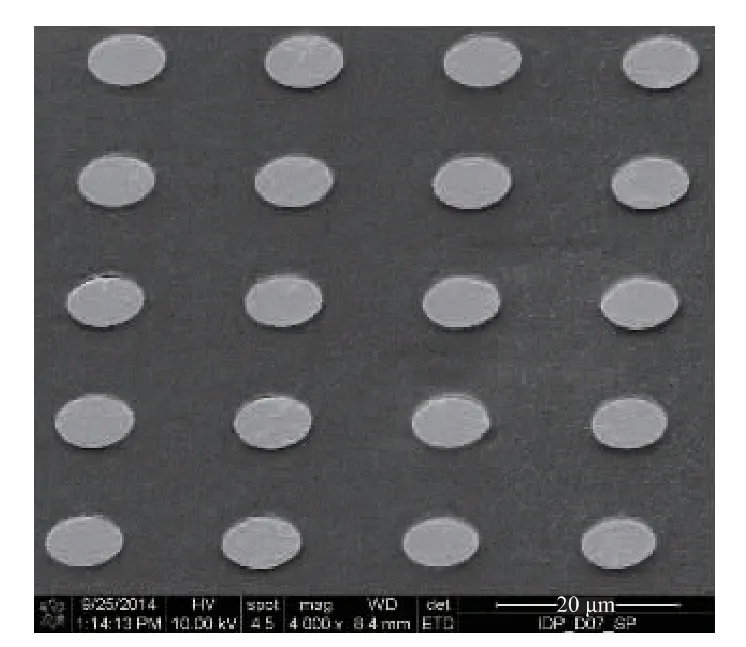

預成型底部填充技術主要應用于倒裝芯片窄節距互連中,芯片與基板之間的高度也比較小,傳統底部填料中的微米級SiO2顆粒難以滿足節距及高度不斷縮小的需要, 很容易出現孔洞, 因此利用納米級SiO2作為填料成為了新的發展趨勢[2,41-42],圖18 所示為制得的納米SiO2顆粒。市場上也開始出現了一些較為成熟的填充納米SiO2的底部填料。

圖18 納米SiO2 顆粒掃描電鏡照片

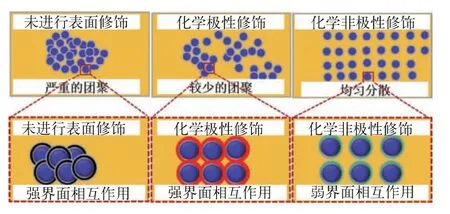

利用納米SiO2顆粒作為填料還存在一些問題:納米SiO2具有較大的比表面積和表面自由能,易于產生團聚,導致分散性較差;同時,填充納米SiO2后底部填料的粘度急劇增加,流動性變差;此外,嚴重的團聚會使填料與基體之間的界面結合變弱,降低底部填料整體的熱機械性能[42]。

研究結果表明,通過溶膠-凝膠法、化學沉淀法等制備得到的SiO2納米顆粒表面存在大量的硅烷醇,會導致底部填料的粘度增加,熱機械性和可靠性也會下降。因此,為制備得到高性能的底部填料,去除SiO2填料表面的-OH 基是非常必要的[43]。 表面改性是一種有效的方法,可消除-OH 的負面影響。 最廣泛使用的表面改性劑是硅烷偶聯劑。 由于其獨特的結構,其一端可以與SiO2填料發生物理或化學鍵合,另一端與聚合物基體實現優異的相容性,可以顯著改善SiO2在聚合物基體中的分散性和界面相容性。 按照硅烷偶聯劑的添加方法可以分為物理添加和化學改性。 物理添加是直接將填料和偶聯劑混合到環氧基質中,而化學改性是將改性后的SiO2添加到環氧基質中。 相比之下,化學表面改性可以在粘度和熱機械性能方面實現更好的改善[44]。 圖19 所示為利用化學改性方法對納米級SiO2顆粒進行表面處理后的效果[45],通過這種方法得到了分散均勻、與聚合物基體界面相容的納米SiO2填料,該復合材料的各項性能(包括粘度、CTE 等)都滿足對底部填料的需求。

圖19 化學改性方法對納米級SiO2 顆粒進行表面處理[45]

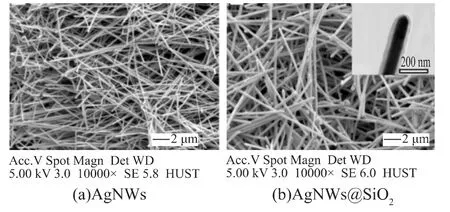

此外,隨著對底部填料導熱性能的需求進一步增加,需要開發新的材料來提高材料的熱導率。 目前的研究方向為用其他熱導率較高的材料替換SiO2顆粒作為新的填料,從而提高底部填料整體的熱導率。 有研究將具有高導熱性的陶瓷填料如氮化硼、 氮化鋁、氧化鋁和碳化硅等摻入環氧樹脂,但是因為要實現高導熱性能,往往需要填充大量的陶瓷填料,而這可能會導致底部填料的熱機械性能變差,粘度變高。 也有研究利用銀納米線(AgNWs)作為填料,但銀的導電性能太好, 因此底部填料的絕緣性無法得到嚴格的保證。有研究者提出了AgNWs@SiO2核殼結構來作為填料[46],如圖20 所示。 最終得到的AgNWs@SiO2復合環氧基底部填料既可以實現較高熱導率[大于1 W·(m·K)-1],又能滿足底部填料絕緣性、粘度小于20 Pa·s 等其他方面的性能需求。

圖20 新型底部填充材料中的填料[46]

4 結論

隨著倒裝芯片底部凸點的節距越來越小,原來的組裝后底部填充技術已不能適應100 μm 以下的窄節距工藝,為了窄節距芯片互連的需要開發了預成型底部填充技術,該技術主要包括非流動底部填充和圓片級底部填充兩大類。

以NCP 為代表的非流動底部填充和以NCF 為代表的圓片級底部填充均已成功應用于實際工業生產中。 NCP 與NCF 的材料組成基本相同, 但NCP 為液態,NCF 是以膜的形式存在,兩者工藝不同。

針對NCP/NCF 預成型底部填充技術生產效率較低、電互連可靠性以及材料性能等方面的問題,產業界提出了多種改進措施:針對提高生產效率,開發了分步鍵合的方法,該法也能用于芯片三維集成;為解決SiO2顆粒嵌入互連界面的問題,提出了采用雙層工藝、兩步工藝、混合鍵合及自組裝技術等解決方法,以去除凸點表面的底部填料從而得到更為可靠的電互連。 底部填料性能的改進主要集中在填料的選擇上:為適應窄節距互連,采用納米級SiO2填料并對易發生團聚的納米SiO2顆粒進行表面改性。 此外,還可以通過將傳統的SiO2填料替換成熱導率更高的陶瓷粉填料、氧化鋁填料、納米級AgNWs、AgNWs@SiO2等材料來獲得導熱性能和可靠性更高的底部填料,以滿足目前電子產品中更高的散熱需求。 今后窄節距倒裝芯片的底部填充技術和高性能底部填充料的改進都仍將是微電子封裝技術發展中的重要方向之一。