基于FPGA 定時刷新控制單元的應用技術研究

孫潔朋, 陳波寅, 晏慧強, 叢紅艷, 何小飛

(無錫中微億芯有限公司, 江蘇 無錫 214072)

1 引言

近年來,SRAM 型的FPGA 因其編程速度快、開發周期短等優點, 被大量應用在復雜的電子設計中,在航空航天領域的應用也越來越廣泛。 然而,在宇宙環境中,存在著大量的高能粒子,此工藝的FPGA 極易受到空間高能粒子的影響,發生單粒子翻轉(SEU)[1]。SEU 效應通常會導致FPGA 中的存儲單元發生位翻轉(即內容由0 變為1,或由1 變為0),隨之帶來的后果可能是計算結果錯誤、程序執行序列錯誤,工作異常,甚至是系統的永久失效、燒毀等[2-3],因此必須對FPGA 器件進行抗單粒子翻轉加固設計, 最大限度地預防和阻止空間輻射效應的影響,提高航天器任務的可靠性。

提高FPGA 抗單粒子翻轉的方法隨著科學技術的發展也在不斷地優化和更新。 目前主要有以下幾種方法:①采用三模冗余,利用3 個功能相同的冗余模塊和多數表決器來避免錯誤; ②回讀配置區的數據幀,與初始配置數據進行對比,對出錯幀或是整個配置幀進行刷新[4];③配置反熔絲PROM,通過編程定時刷新FPGA[5]。 三模冗余不會對出錯配置信息進行修復,當錯誤累積到一定程度,器件就會失效。 回讀刷新則一般采用反熔絲FPGA 器件控制芯片刷新,其軟硬件設計較為復雜[1]。

本文給出了一種抗輻照的低成本解決方案,該控制單元采用三模冗余加定時刷新的方法來及時修正已出現的錯誤,提高抗SEU 的能力,并通過RTL 代碼應用仿真驗證,證明該方案的各項功能滿足設計要求。

2 整體方案設計

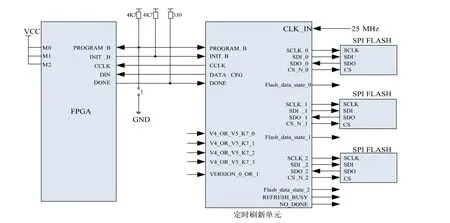

依據前面所介紹的設計需求,本文基于FPGA 定時刷新控制單元的整體設計方案如圖1 所示。

圖1 刷新電路整體設計框圖

由圖1 可知,該電路需要外接3 片SPI FLASH,工作時會對3 片SPI FLASH 中的數據進行單比特校驗,采用表決通過的數據作為正確配置信息,具有單比特糾錯的三模校驗功能, 然后通過串行端口, 配置V4、V5 和K7 類型的FPGA, 并且在配置完成后對FPGA的邏輯部分進行定時刷新[6],糾正邏輯部分因為翻轉產生的錯誤,從而達到抗輻照的目的。

市面上帶有刷新控制的芯片有不少,例如中國自主研制的BSV2 定時刷新芯片和ACTEL 公司的抗輻射反熔絲FPGA A54SX32A 芯片, 這兩款芯片都有定時刷新控制,但沒有三模冗余的功能,支持的芯片為Xilinx 公司的Virtex II,而Virtex II 系列芯片可利用的邏輯單元較少,已不能適應未來航天的發展需求。 本文中的設計采用3 片SPI FLASH 存儲配置信息,有三模冗余和定時刷新功能,同時兼容V4、V5 和K7 類型的多款FPGA 芯片, 可以滿足航天領域對抗輻照型FPGA 的使用需求。

Xilinx 公司的FPGA 芯片配置訪問接口有JTAG、SelectMap(從串)以及ICAP 3 種,本文中設計的定時刷新器件利用FPGA 的SelectMap 接口完成配置與刷新。

3 系統設計

本文中的定時刷新控制單元,是基于SPI FLASH設計實現的。SPI FLASH 容量為128 Mbit,電路設計的最高工作時鐘頻率為25 MHz,串行配置速率在1 MHz左右,刷新時間間隔可以選擇連續刷新、10 min、20 min、30 min 4 種模式。基于SPI FLASH 的抗輻射系統如圖2 所示。

FPGA 配置數據存儲在3 片SPI FLASH 芯片中,與FPGA 之間通過抗輻照定時刷新單元連接,刷新電路起到數據交換的橋梁作用, 如圖2 所示。 定時刷新電路有兩種工作模式:配置模式和刷新模式。 系統初始上電時, 定時刷新電路處于配置模式, 通過SelectMap 模式配置FPGA,系統正常工作后,刷新電路進入定時刷新模式, 按設定的時間周期性地將SPI FLASH 中的邏輯信息配置到FPGA 中,完成刷新。

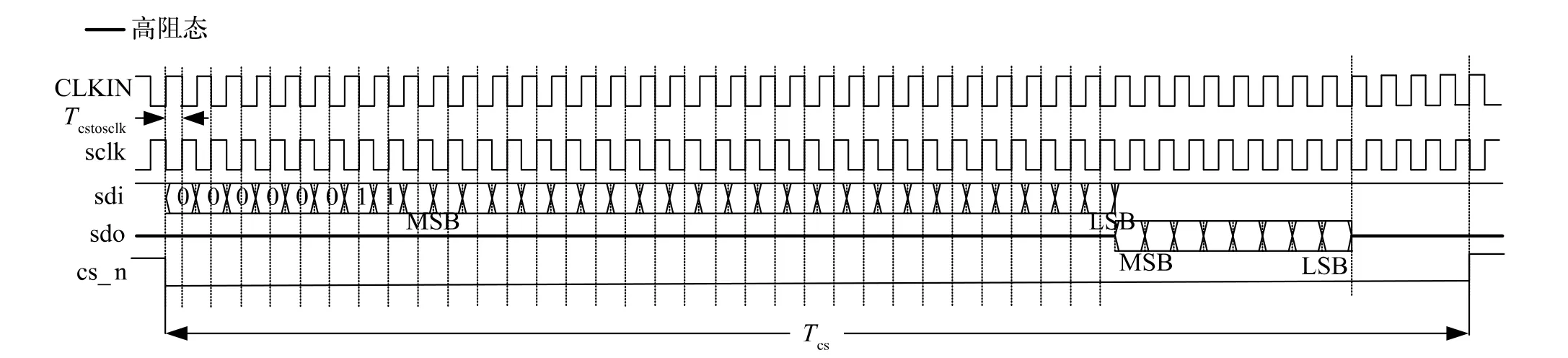

SelectMap 模式的連接方式如圖2 所示,M0、M1、M2 接電源(VCC),用于設置FPGA 的配置模式為從串模式, 即CCLK 的來源是外部。 PROGRAM_B 和INIT_B 需接4.7 kΩ 的上拉電阻,DONE 信號需接330 Ω 的上拉電阻。 對FPGA 的從串配置時序[7]如圖3所示。

定時刷新控制電路通過檢測FPGA 芯片的DONE 信號來決定進入配置模式還是刷新模式。 配置和刷新的工作流程如圖4 所示。

由圖4 可知, 定時刷新控制單元在工作過程中主要完成以下4 個功能:

1)FPGA 及刷新電路上電配置。 初始化的FPGA上電后, 將PROGRAM_B 信號至少拉低300 ns 后置高,INIT_B 會自動產生0 到1 的跳變, 若INIT_B 為高,指示FPGA 內部初始化完成,進入數據下載過程,同時等待刷新電路內部復位完成, 之后開始正常工作,若INIT_B 為低,則一直檢測該信號,直到變為高電平為止。

圖2 基于SPI FLASH 的抗輻射系統

圖3 FPGA 串行配置時序

2)ID 檢測。 刷新單元在復位完成后,首先工作是檢測3 片FLASH 的ID 信息,ID 檢測有效后開始訪問SPI FLASH 中的數據,進行后續配置下載,否則鎖死在讀ID 狀態并報警。

3) 配置FPGA 芯片。 ID 檢測有效后, 開始配置FPGA, 設置的FPGA 專用配置模式管腳M0~M2 為000,進入從串模式下載,刷新電路發送CCLK 同步時鐘給FPGA 芯片, 并將3 片FLASH 中存儲的碼流信息進行單比特校驗, 以25 MHz 為例,V4 大概需要10 ms,V5 需要45 ms,K7 需要115 ms,來完成所有配置信息的對比,然后將表決通過的數據經過DIN 引腳配置到FPGA 芯片中,圖5 為SPI 的數據讀取操作。

4)檢測DONE 狀態。 進入配置狀態后,電路會持續檢測DONE 信號,一旦超過預計完成配置的時間卻還未拉高,則意味著配置失敗,會自動在該FPGA 芯片的INIT_B 端施加復位脈沖,進行重新配置;

5)定時刷新。 當檢測到DONE 信號變高電平后,刷新控制電路會自動啟動刷新模式,按用戶需求加載不同型號芯片的頭部數據,先刷新一次,然后按選擇的時間周期性地刷新SPI FLASH 中的邏輯數據。

本文中的抗輻照定時刷新控制單元,最高工作時鐘為25 MHz 時, 支持Xilinx 公司Virtex4 系列的XC4VLX25,Virtex5 系列 的XC5VSX95T 和K7 系 列的XC7K325T,刷新時間間隔也有4 種可選,能夠滿足不同用戶的應用需求。

圖4 SPI FLASH 配置和刷新工作流程

圖5 SPI FLASH 數據讀取操作

4 應用驗證

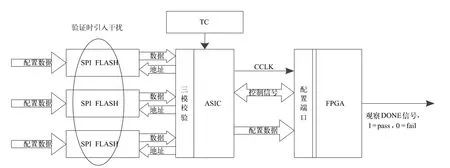

本文中的定時刷新控制單元旨在給出一種低成本的抗輻照解決方案,為了檢驗本方案能否滿足設計需求,這里給出了RTL 代碼的驗證,對定時刷新控制單元在工作過程中主要完成的4 個功能進行重點驗證,并通過應用驗證來說明該設計能夠通過三模冗余及定時刷新措施以提高抗單粒子翻轉, 滿足應用需求。 下面以Xilinx 公司的Virtex5 系列的XC5VSX95T為例,進行刷新電路的RTL 代碼的應用驗證。 定時刷新控制單元的驗證方案如圖6 所示。 利用搭建好的FPGA 芯片配置環境進行本方案中的RTL 代碼驗證,通過驗證模擬實現刷新電路工作時的各種狀態,確保設計能達到預期目標。

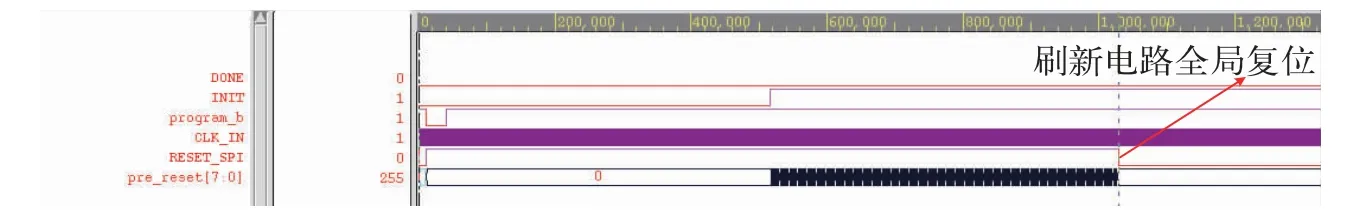

刷新電路復位管理模塊仿真如圖7 所示。 首先是上電后,刷新電路復位管理模塊的正常啟動,通過上電后FPGA 的PROGRAM_B 和INIT_B 兩個信號共同作用來控制電路的全局復位工作。

FLASH 的ID 檢測仿真如圖8 所示。 電路的全局復位正常啟動后,開始檢測FLASH 的ID,讀ID 通過,則開始訪問FLASH 中的數據,否則一直在鎖死狀態。

3 片FLASH 數據單比特校驗及FPGA 配置仿真如圖9 所示。 ID 檢測通過后, 開始接收存儲在3 片SPI FLASH 中的數據,經過單比特校驗后,將表決通過的數據配置給FPGA,通過觀察DONE 信號是否拉高來判斷配置是否正確, 超過預估時間未檢測到DONE 信號變化, 說明配置信息錯誤,INIT_B 信號會復位一次,重新配置FPGA。在驗證中加入了不同形式的干擾信息,來模擬空間環境。 flash_data_state 為3 片FLASH 數據表決狀態信號,根據這個信號可以判斷是哪片FLASH 配置信息出現問題。

圖6 定時刷新控制單元的驗證方案

圖7 刷新電路復位管理模塊仿真

圖8 FLASH 的ID 檢測仿真

圖9 3 片FLASH 數據單比特校驗及FPGA 配置仿真

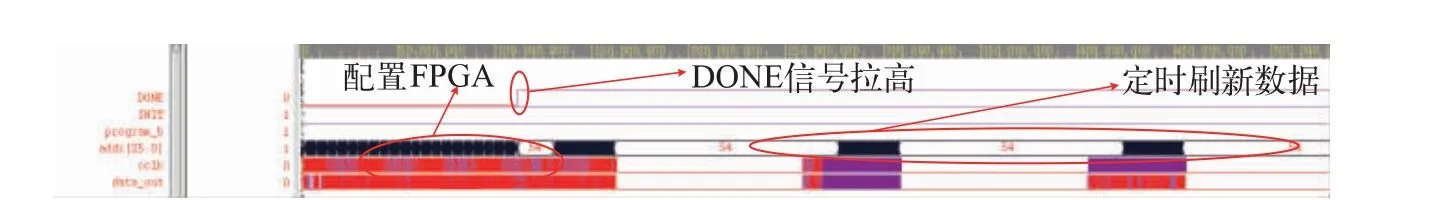

芯片刷新過程如圖10 所示。 完成FPGA 配置后,刷新電路會執行立即刷新操作,然后按設計的時間周期性刷新芯片。

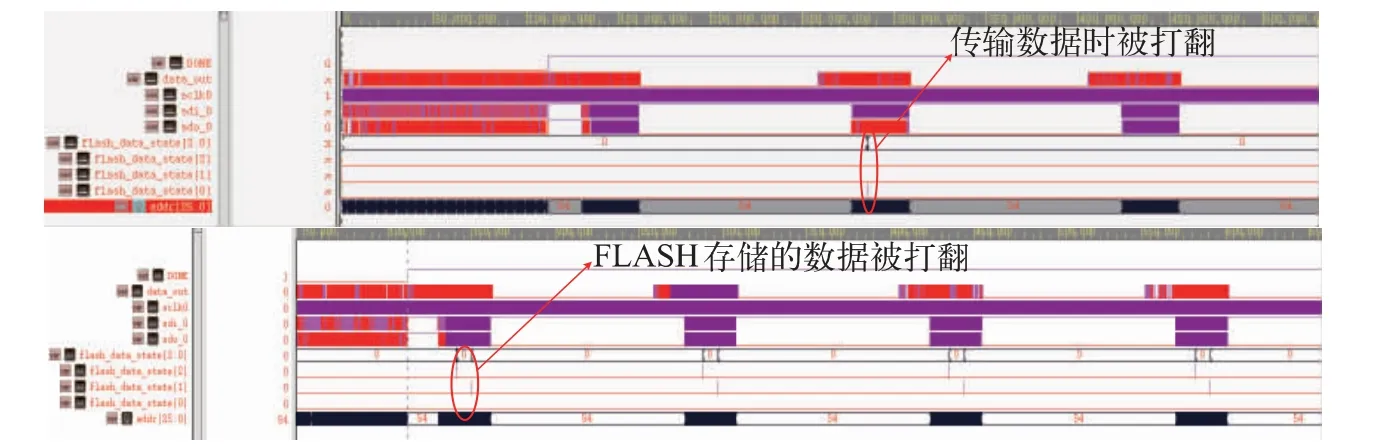

有粒子干擾時的刷新仿真如圖11 所示。 在電路定時刷新的過程中,會受到高能粒子干擾,配置信息會有概率性地發生翻轉,翻轉的類型有多種,這里給出了其中兩種, 一個是FLASH 將配置信息發送到控制單元時發生翻轉, 一個是FLASH 存儲的信息發生翻轉。

圖10 芯片刷新仿真驗證

圖11 外部干擾時芯片刷新仿真驗證

刷新電路將受干擾的配置信息進行三模冗余,然后配置到芯片中,因為是單比特檢驗,可以提高抗干擾的能力,但隨著使用時間的增長,錯誤信息累積越來越多,會在某個時刻將校驗通過的錯誤信息發送到FPGA 芯片中,從而導致功能異常,電路失效。 本文給出的方案可以延緩這個時刻的到來,增加裝備的使用壽命。 后續的技術改進可以把這個問題作為研究方向,一種方法是將FPGA 斷電,重新對FLASH 燒寫正確的碼流信息,然后上電,完成配置與刷新,其他方法有待未來進一步研究。

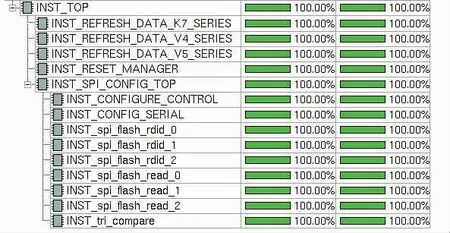

針對本方案設計所有功能驗證點,進行了如圖12所示的覆蓋率收集,所有驗證用例功能正確,覆蓋率達到100%。

上述驗證結果表明,本文提出的基于FPGA 定時刷新控制單元的設計切實可行,所設計的功能達到預期目標, 通過三模冗余與定時刷新的功能來提高抗SEU 的能力,能夠滿足應用需求。

圖12 刷新電路功能覆蓋率收集

5 結論

本文給出了一種基于抗輻照型FPGA 芯片的定時刷新控制單元的可行性設計方案,通過采用三模冗余加定時刷新相結合的加固技術, 可以有效解決SRAM 型FPGA 在空間環境應用中遇到的單粒子翻轉問題。 后續還有一些問題需要解決,比如粒子翻轉過多、影響芯片功能時,可以采用對FLASH 重新燒寫正確碼流的方法來解決這一問題,從而更好地滿足航天領域對抗輻照型FPGA 的使用需求。