航電系統(tǒng)綜合核心處理機(jī)容錯設(shè)計

何立軍 王夢凡 王生宵 秦琪 周廣飛

摘要:綜合化核心處理機(jī)作為綜合模塊化航空電子系統(tǒng)控制和管理的核心,對于實現(xiàn)航空電子系統(tǒng)的功能、性能起著決定性的作用。介紹了一種基于冗余技術(shù)的綜合核心處理機(jī)容錯設(shè)計,從供電容錯、網(wǎng)絡(luò)容錯、模塊容錯設(shè)計等進(jìn)行介紹,對產(chǎn)品可靠性進(jìn)行分析,結(jié)果表明冗余設(shè)計能夠明顯提高產(chǎn)品任務(wù)可靠性。

關(guān)鍵詞:綜合核心處理機(jī);容錯;冗余;可靠性

中圖分類號:TP311 ? 文獻(xiàn)標(biāo)識碼:A

文章編號:1009-3044(2021)35-0115-03

Fault-Tolerant Design of Integrated Core Processor for the Avionics Systems

HE Li-jun, WANG Meng-fan, WANG Sheng-xiao, QIN Qi, ZHOU Guang-fei

(Xi’an Aeronautics Computing Technique Research Institute of AVIC, Xi'an 710065, China)

Abstract: Integrated Core Processor is the control and management center of Integrated Modular Avionics System. It is crucial for the implementation of Avionics System functions and performances. A fault-tolerant ICP design, based on redundant technology, is presented as in Power Supply Fault-tolerant, Network Fault-tolerant and Module Fault-tolerant, as well as its reliability analysis, Thus Mission Reliability has been improved remarkably after a redundant product design.

Key words: integrated core processor; fault-tolerant; redundant; reliability

新一代航空電子系統(tǒng)是一種綜合化、模塊化的機(jī)載分布式系統(tǒng),綜合核心處理機(jī)是新一代航空電子系統(tǒng)的核心,它承擔(dān)著大量飛行任務(wù)的執(zhí)行、控制和飛機(jī)安全性保障等工作,核心處理平臺的可靠運(yùn)行對于實現(xiàn)航空電子系統(tǒng)的功能、性能起著決定性的作用。容錯技術(shù)是提高可靠性的有效方法,機(jī)載系統(tǒng)常采用余度設(shè)計,利用多余資源來換取系統(tǒng)可靠性的提高。該方法可有效提高機(jī)載產(chǎn)品的可靠性和安全性,實現(xiàn)產(chǎn)品一次故障工作,二次故障安全等要求。

本文首先介紹了某綜合核心處理機(jī)系統(tǒng)組成,接著分析了該核心處理機(jī)供電、網(wǎng)絡(luò)、系統(tǒng)管理、數(shù)據(jù)處理等方面所采用的余度容錯技術(shù),為機(jī)載電子設(shè)備容錯設(shè)計提供可參考的依據(jù)。

1 系統(tǒng)設(shè)計

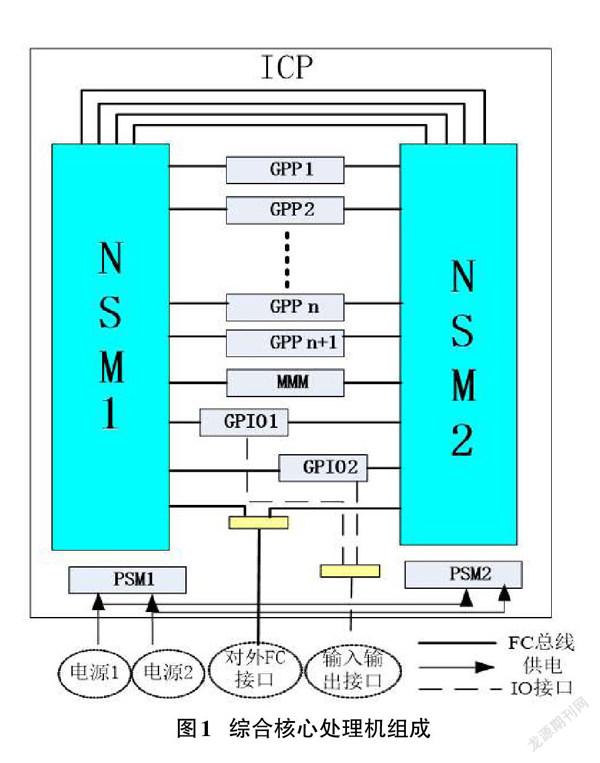

綜合核心處理機(jī)ICP作為航空電子系統(tǒng)的管理和處理中心,承擔(dān)了系統(tǒng)管理、傳感器管理和數(shù)據(jù)融合、雷達(dá)數(shù)字功能處理、電子戰(zhàn)數(shù)字脈沖功能處理、通信導(dǎo)航識別數(shù)字功能處理、紅外搜索跟蹤、分布式孔徑、數(shù)字地圖處理、戰(zhàn)場態(tài)勢處理、圖像處理、顯示控制和管理處理、音頻處理、數(shù)據(jù)管理、健康管理等多個任務(wù)。某綜合核心處理機(jī)采用符合ASAAC標(biāo)準(zhǔn)的LRM模塊,基于高性能數(shù)據(jù)處理和統(tǒng)一高速網(wǎng)絡(luò)技術(shù),設(shè)計了一種FC交換網(wǎng)絡(luò)的綜合核心處理機(jī)系統(tǒng),如圖1所示。

ICP內(nèi)部包括5種標(biāo)準(zhǔn)LRM:通用處理模塊(GPP)、通用處理及IO模塊(GPIO)、大容量存儲模塊(MMM)、網(wǎng)絡(luò)交換模塊(NSM)、電源模塊(PSM)。GPP、MMM、GPIO的FC接口連接到NSM上,從而實現(xiàn)各LRM間通過FC交換網(wǎng)絡(luò)完成數(shù)據(jù)通信。

2 容錯設(shè)計

綜合核心處理機(jī)具有綜合化、模塊化、軟件化、網(wǎng)絡(luò)化等多種特征,在結(jié)構(gòu)上進(jìn)行了高密度集成的一個實時的容錯的分布式的機(jī)群。核心處理機(jī)在綜合化航空電子系統(tǒng)中居于核心位置,是整個綜合航電的“大腦”和“神經(jīng)”。在系統(tǒng)設(shè)計過程中采用熱備份、溫備份、冷備份等技術(shù),使系統(tǒng)具有完備的容錯、重構(gòu)和冗余控制能力,能夠承擔(dān)安全級別為生存關(guān)鍵和任務(wù)關(guān)鍵的相關(guān)航電任務(wù)功能。

2.1 電源容錯

電源容錯設(shè)計如圖2所示。ICP內(nèi)部配置2塊PSM,按照并聯(lián)方式為其他所有用電LRM進(jìn)行供電。

飛機(jī)通過2根270VDC電源匯流條向ICP提供270VDC電源,2路270VDC輸入電源并聯(lián)后,經(jīng)過同一套濾波電路后分別向2塊PSM模塊提供270VDC。當(dāng)飛機(jī)供電系統(tǒng)出現(xiàn)1路270VDC供電故障時,另一路供電輸入可以支持ICP保持全狀態(tài)工作;當(dāng)出現(xiàn)2路270VDC供電故障時,由APU為ICP提供輸入電源,此時ICP按照系統(tǒng)配置為部分LRM提供電源,ICP降級工作。

2塊PSM模塊采用1+1余度供電設(shè)計,一旦某一電源發(fā)生故障,另一電源能獨立承擔(dān)對所有LRM模塊供電的能力。用電LRM模塊設(shè)計為2路并聯(lián)輸入,無論是由于某路外部供電故障或是LRM供電輸入端故障,均可確保模塊正常工作。

PSM模塊除了完成功率轉(zhuǎn)換外,還具有智能管理和開關(guān)矩陣控制處理能力,能夠?qū)╇娸斎搿⑤敵龅冗M(jìn)行檢測診斷,能夠基于監(jiān)控到的信息控制電源開關(guān)矩陣,及時對由于用電模塊發(fā)生類似短路故障造成輸出監(jiān)測異常的接口進(jìn)行關(guān)閉,提高故障隔離性,以確保系統(tǒng)在任何情況下的正常工作。

2.2 網(wǎng)絡(luò)容錯

對于FC交換網(wǎng)絡(luò),應(yīng)用中網(wǎng)絡(luò)可能出現(xiàn)的故障有NSM模塊故障、NSM模塊某交換端口故障、LRM模塊FC節(jié)點故障等幾種主要故障模式。ICP中FC網(wǎng)絡(luò)架構(gòu)在應(yīng)用層提供一定的余度容錯能力,能夠有效地避免出現(xiàn)某種故障時,ICP不降級或完成關(guān)鍵任務(wù)。網(wǎng)絡(luò)架構(gòu)詳見圖1。

ICP中共設(shè)計2個NSM,級聯(lián)后組成更大規(guī)模交換網(wǎng)絡(luò)。FC網(wǎng)絡(luò)架構(gòu)中,ICP與外部雷達(dá)、電子戰(zhàn)、CNI等子系統(tǒng)之間的數(shù)據(jù)通道均在應(yīng)用級提供備份FC接口;在ICP內(nèi)部,所有LRM模塊對外均包含2路FC節(jié)點接口,同時連接到2個NSM模塊。當(dāng)網(wǎng)絡(luò)出現(xiàn)某種故障(或網(wǎng)絡(luò)接口或交換機(jī)或通信電纜)時,網(wǎng)絡(luò)數(shù)據(jù)可通過另一路FC接口進(jìn)行通信。當(dāng)鏈路中2個網(wǎng)絡(luò)接口設(shè)計為備份工作模式,故障時ICP可正常工作;當(dāng)鏈路中2個網(wǎng)絡(luò)接口設(shè)計為同時使用,故障時ICP可使用1路接口降級工作,完成關(guān)鍵任務(wù)執(zhí)行。

2.3 模塊容錯

模塊級容錯主要通過各個主要功能模塊的冗余備份及系統(tǒng)容錯重構(gòu)管理軟件來實現(xiàn)。

ICP中的通用處理模塊(GPP)主要承擔(dān)ICP中的數(shù)據(jù)處理與部分信號處理功能,用于完成ICP中雷達(dá)數(shù)據(jù)處理、電子戰(zhàn)信號處理與數(shù)據(jù)處理、光電控制與目標(biāo)解算等任務(wù)。GPP模塊設(shè)計為n+1備份工作模式,提供熱備份、溫備份、冷備份方式,GPP模塊可預(yù)先駐留所有功能模塊程序,當(dāng)某一功能模塊失效,通過系統(tǒng)配置預(yù)案方式用備份的GPP模塊代替故障失效模塊或動態(tài)地在處理器資源使用率較低的模塊上分配執(zhí)行。

ICP中的通用處理及輸入輸出模塊(GPIO)主要承擔(dān)PHM、火控解算等任務(wù),以及ICP的系統(tǒng)控制與管理功能。ICP是一個多處理機(jī)、多任務(wù)系統(tǒng),所有任務(wù)將在系統(tǒng)控制器的統(tǒng)一控制與管理下協(xié)同工作。系統(tǒng)控制器任務(wù)由GPIO承擔(dān)。ICP中一共有2塊GPIO,它們工作在1+1熱備份方式下。在初始化時競爭控制權(quán),沒有競爭上的GPIO模塊作為主控制器的熱備份,在運(yùn)行過程中系統(tǒng)的主控制器發(fā)生故障時,系統(tǒng)自動切換到備份模塊。2塊GPIO模塊之間設(shè)計2路用于控制器搶權(quán)的離散量接口,1路為輸出離散量,1路為輸入離散量,如圖3所示,輸出離散量用來表示自己是否取得系統(tǒng)控制權(quán),當(dāng)輸出為1時表示取得控制權(quán),輸出為0時表示未取得。系統(tǒng)控制器搶權(quán)過程如下:

1)系統(tǒng)識別到該模塊為GPIO1時,設(shè)置為系統(tǒng)控制器,輸出離散量設(shè)置為“1”;

2) GPIO2模塊檢測到輸入為“1”時,設(shè)置自身輸出離散量為“0”,作為備份模塊;

3) 如系統(tǒng)控制器GPIO1發(fā)生故障,輸出離散量狀態(tài)由“1”變?yōu)椤?”;

4) GPIO2監(jiān)測到輸入為“0”時,判斷系統(tǒng)控制器故障,設(shè)置自身輸出離散量為“1”,GPIO2負(fù)責(zé)實現(xiàn)ICP主控制器相關(guān)功能。

GPIO模塊除完成相應(yīng)的計算處理功能外,還負(fù)責(zé)對外IO接口,互為備份的2塊GPIO模塊,它們都能訪問外部I/O接口,但系統(tǒng)控制器在數(shù)據(jù)處理、接收控制指令、系統(tǒng)控制等方面起著決定性的作用;備份模塊執(zhí)行診斷和監(jiān)視系統(tǒng)控制器工作狀態(tài)的好壞,通過查詢運(yùn)行中的系統(tǒng)控制器的工作狀態(tài),可接收外部輸入進(jìn)行處理,同系統(tǒng)控制器執(zhí)行同樣的處理、操作,但不執(zhí)行輸出控制,不進(jìn)行系統(tǒng)控制。備控模塊能夠?qū)崟r保存最新的系統(tǒng)控制數(shù)據(jù),以便在主/備模式切換時保證系統(tǒng)工作的無縫連接。IO功能接口設(shè)計如圖4所示,對于外部輸入信號,同時輸入到2塊GPIO模塊中,進(jìn)行同樣的處理,對于輸出信號,2塊GPIO模塊輸出接口并聯(lián)后輸出到外部接口,但使用搶權(quán)輸出離散量作為使能控制信號,僅作為系統(tǒng)控制器的GPIO模塊可以輸出,備份模塊禁止輸出,這樣控制邏輯保證一個時刻只有一個通道對外打開,提高系統(tǒng)工作的穩(wěn)定性,避免兩個處理器競爭搶占外部接口共同控制的情形。

3 可靠性分析

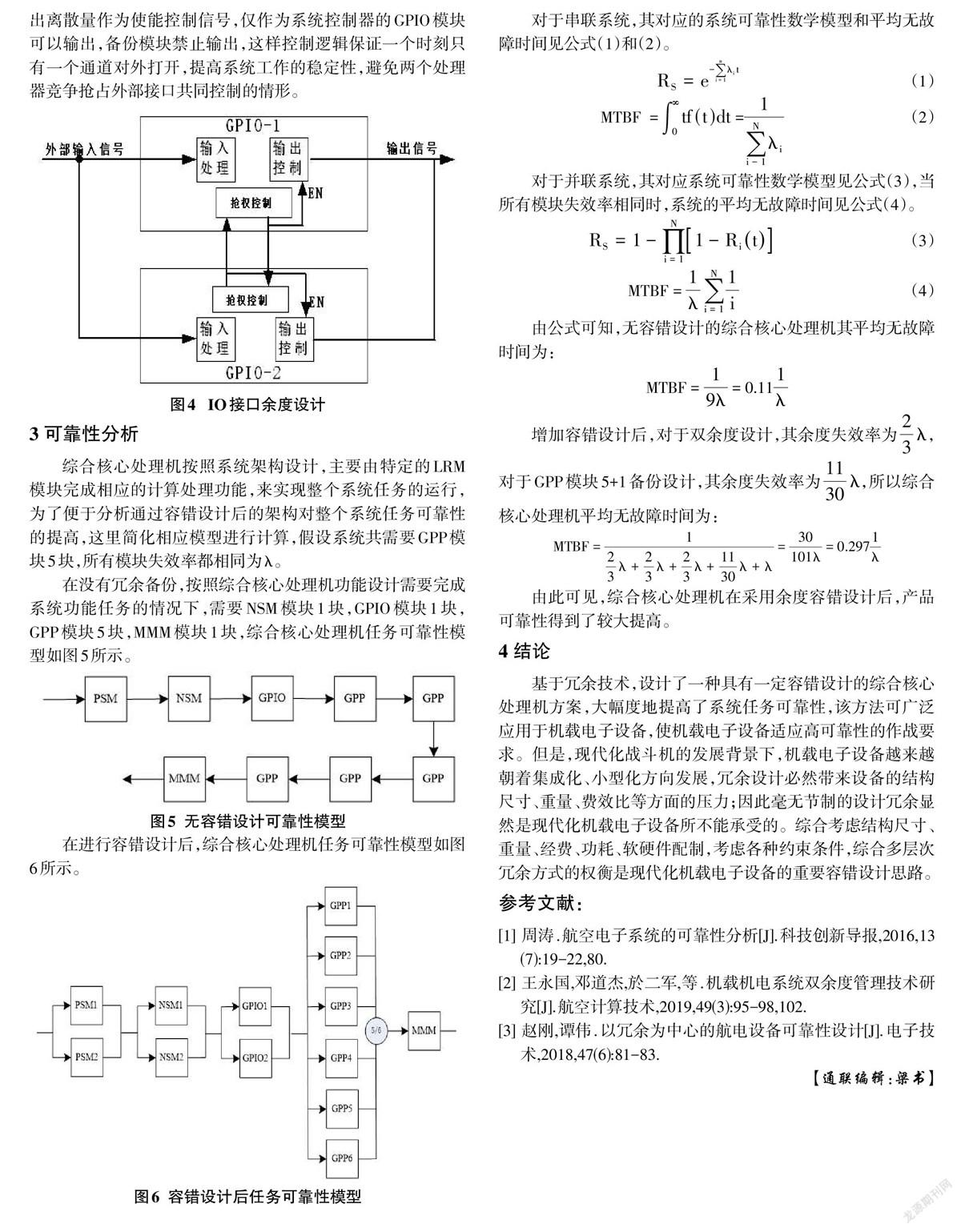

綜合核心處理機(jī)按照系統(tǒng)架構(gòu)設(shè)計,主要由特定的LRM模塊完成相應(yīng)的計算處理功能,來實現(xiàn)整個系統(tǒng)任務(wù)的運(yùn)行,為了便于分析通過容錯設(shè)計后的架構(gòu)對整個系統(tǒng)任務(wù)可靠性的提高,這里簡化相應(yīng)模型進(jìn)行計算,假設(shè)系統(tǒng)共需要GPP模塊5塊,所有模塊失效率都相同為λ。

在沒有冗余備份,按照綜合核心處理機(jī)功能設(shè)計需要完成系統(tǒng)功能任務(wù)的情況下,需要NSM模塊1塊,GPIO模塊1塊,GPP模塊5塊,MMM模塊1塊,綜合核心處理機(jī)任務(wù)可靠性模型如圖5所示。

在進(jìn)行容錯設(shè)計后,綜合核心處理機(jī)任務(wù)可靠性模型如圖6所示。

對于串聯(lián)系統(tǒng),其對應(yīng)的系統(tǒng)可靠性數(shù)學(xué)模型和平均無故障時間見公式(1)和(2)。

[RS=e-i=1nλit] ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(1)

MTBF ?= [0∞tf(t)dt] =[1i-1Nλi] ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? (2)

對于并聯(lián)系統(tǒng),其對應(yīng)系統(tǒng)可靠性數(shù)學(xué)模型見公式(3),當(dāng)所有模塊失效率相同時,系統(tǒng)的平均無故障時間見公式(4)。

[RS=1-i=1N1-Rit] ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(3)

MTBF = [1λi=1N1i] ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(4)

由公式可知,無容錯設(shè)計的綜合核心處理機(jī)其平均無故障時間為:

MTBF = [19λ] = 0.11[1λ]

增加容錯設(shè)計后,對于雙余度設(shè)計,其余度失效率為[23λ],對于GPP模塊5+1備份設(shè)計,其余度失效率為[1130λ],所以綜合核心處理機(jī)平均無故障時間為:

MTBF = [123λ+23λ+23λ+1130λ+λ] = [30101λ] = 0.297[1λ]

由此可見,綜合核心處理機(jī)在采用余度容錯設(shè)計后,產(chǎn)品可靠性得到了較大提高。

4 結(jié)論

基于冗余技術(shù),設(shè)計了一種具有一定容錯設(shè)計的綜合核心處理機(jī)方案,大幅度地提高了系統(tǒng)任務(wù)可靠性,該方法可廣泛應(yīng)用于機(jī)載電子設(shè)備,使機(jī)載電子設(shè)備適應(yīng)高可靠性的作戰(zhàn)要求。但是,現(xiàn)代化戰(zhàn)斗機(jī)的發(fā)展背景下,機(jī)載電子設(shè)備越來越朝著集成化、小型化方向發(fā)展,冗余設(shè)計必然帶來設(shè)備的結(jié)構(gòu)尺寸、重量、費效比等方面的壓力;因此毫無節(jié)制的設(shè)計冗余顯然是現(xiàn)代化機(jī)載電子設(shè)備所不能承受的。綜合考慮結(jié)構(gòu)尺寸、重量、經(jīng)費、功耗、軟硬件配制,考慮各種約束條件,綜合多層次冗余方式的權(quán)衡是現(xiàn)代化機(jī)載電子設(shè)備的重要容錯設(shè)計思路。

參考文獻(xiàn):

[1] 周濤.航空電子系統(tǒng)的可靠性分析[J].科技創(chuàng)新導(dǎo)報,2016,13(7):19-22,80.

[2] 王永國,鄧道杰,於二軍,等.機(jī)載機(jī)電系統(tǒng)雙余度管理技術(shù)研究[J].航空計算技術(shù),2019,49(3):95-98,102.

[3] 趙剛,譚偉.以冗余為中心的航電設(shè)備可靠性設(shè)計[J].電子技術(shù),2018,47(6):81-83.

【通聯(lián)編輯:梁書】