基于FPGA的兩級冗余編碼系統

李圣昆,郝少帥,楊玉華,王淑琴,李 金

(1.中北大學儀器科學與動態測試教育部重點實驗室,山西 太原 030051;2.上海航天電子技術研究所,上海 201109)

0 引言

測試人員不便直接測試的極端環境(如高溫、高空、強磁等)往往需要將測試數據遠距離傳輸到地面接收設備。目前常用的傳輸方式包括并行傳輸和串行傳輸。由于數據線接口過多,并行總線傳輸方式在電磁干擾較大的環境中,數據傳輸的可靠性下降嚴重;串行總線包括PECL、RS422、RS485、HOTLink以及LVDS等。PECL的接口電平邏輯不兼容標準邏輯[1];傳統的串行通信如RS232、RS422和RS485的傳輸速率太低,不能滿足實時監測的需求。相同環境條件下,LVDS總線相較HOTLink具有更高的傳輸速率和更遠的傳輸距離,因此采編設備和地面測試設備的通信總線選為LVDS總線。

LVDS是一種低振幅差分傳輸技術,由于傳輸電壓僅為350 mV,在沒有任何補償電路的情況下,LVDS信號僅能在幾米內實現無誤碼傳輸[2];當傳輸距離超過10 m后,傳輸信號就會由于電纜損耗等問題,變得無法識別。當下,現有的優化方案主要有硬件電路和軟件設計兩方面,硬件電路中,添加驅動器和均衡器,LVDS信號的無誤碼傳輸距離增加到了70 m[3],但是仍然無法達到150 m回傳的任務要求。本文針對惡劣條件下數據遠距離傳輸中可靠性不高的問題,提出了基于FPGA的兩級冗余編碼系統。

1 系統的硬件優化

信號在電纜中傳輸時,受到趨膚效應以及介質損耗的影響會產生傳輸衰減[4],趨膚效應產生傳輸衰減與傳輸頻率的平方成正比關系,介質損耗產生的衰減與傳輸速率也是正比關系[5],電纜過長和速率變大都會導致傳輸衰減的增大,衰減過大時便會產生誤碼[6]。為了實現數據的無誤碼傳輸,文章通過對傳輸信號使用了均衡以及預加重技術[7],補償傳輸過程中的信號衰減,從而實現遠距離傳輸。

整個傳輸系統如圖1所示,由采編存儲器、測試臺和屏蔽雙絞線組成。采編存儲器將采集到的信號高速回傳給測試臺進行處理;測試臺接收采編存儲器的數據同時發送指令控制整個采集過程;屏蔽雙絞線連接測試臺和采編存儲器實現數據交互。

圖1 系統總體設計框圖Fig.1 Overall design block diagram of the system

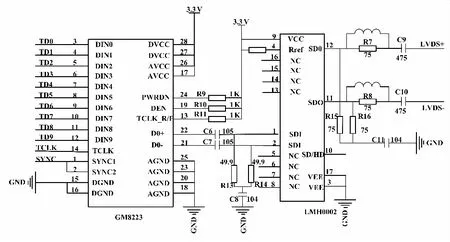

1.1 LVDS發送接口

LVDS發送模塊電路如圖2所示,編碼器選用成都振芯公司的GM8223,電纜驅動器選用TI公司的LMH0002,編碼器的傳輸速率最高為到660 Mb/s,而電纜驅動器的速率超過1 Gb/s,都可以實現高速傳輸的任務要求,發送模塊工作時編碼器會將接收到的時鐘嵌入數據流中,再轉化成串行數據流發送至LMH0002,電纜驅動器對接收到數據流信號進行預加重,把差分輸出電壓拉高到2.5 V后輸出,補償信號在傳輸時的衰減,提高數據傳輸的距離。

圖2 LVDS發送模塊電路Fig.2 LVDS transmission module circuit

圖2中590 Ω的R12用來控制驅動器的輸出電壓為2.5 V。為了降低由于連接器而引起的回波損耗,用電阻和電感構建了損耗網絡[8]。同時為了降低終端反射引起的信號衰減,R13和R14用于阻抗匹配。

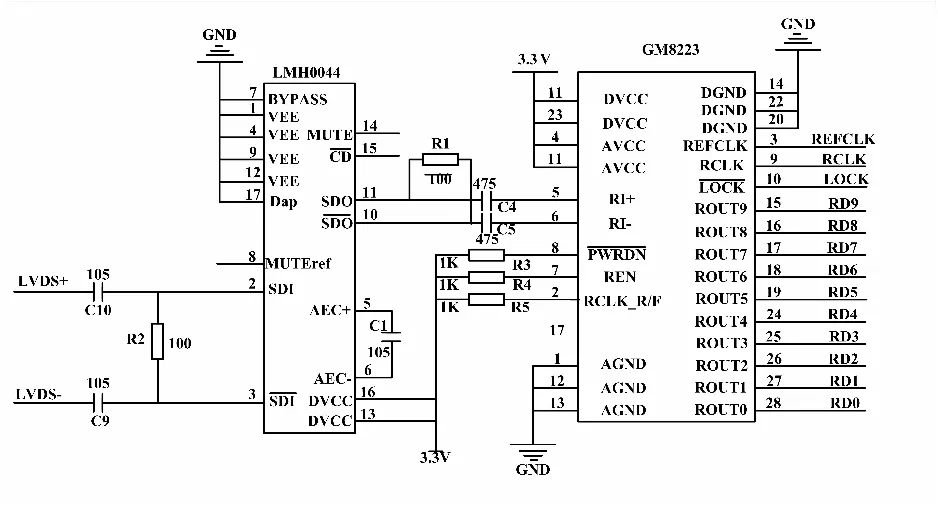

1.2 LVDS接收接口

LVDS接收模塊電路如圖3所示,解碼器同樣選用成都振芯公司的GM8224,均衡器選用TI公司的LMH0044,解碼器的傳輸速率與編碼器相同,可以實現高速數據接收,接收模塊工作時均衡器LMH0044會對從電纜中接收到的衰減數據流進行濾波,再通過恢復電路完成信號的重建,重建后將串行數據流發送至GM8224進行解碼,解碼后恢復為十位數據和一位時鐘。和發送模塊相同,R1和R2也是用于用于降低終端發射阻抗匹配電阻[9]。

圖3 LVDS接收模塊電路Fig.3 LVDS receiving module circuit

2 軟件邏輯優化

各種校驗碼的糾錯能力如表1所示。

表1 校驗碼特性表

文章的軟件優化采用兩級冗余編碼的方式,由表1可知,漢明碼加奇偶校和BCH碼加奇偶校驗在糾錯能力上都大于單一的奇偶校驗、漢明碼和BCH碼,但是漢明碼的實現比BCH碼簡單,所以文章采用漢明碼校驗加偶校驗的編碼方式,實現高糾錯編碼[10]。

2.1 一級冗余編碼

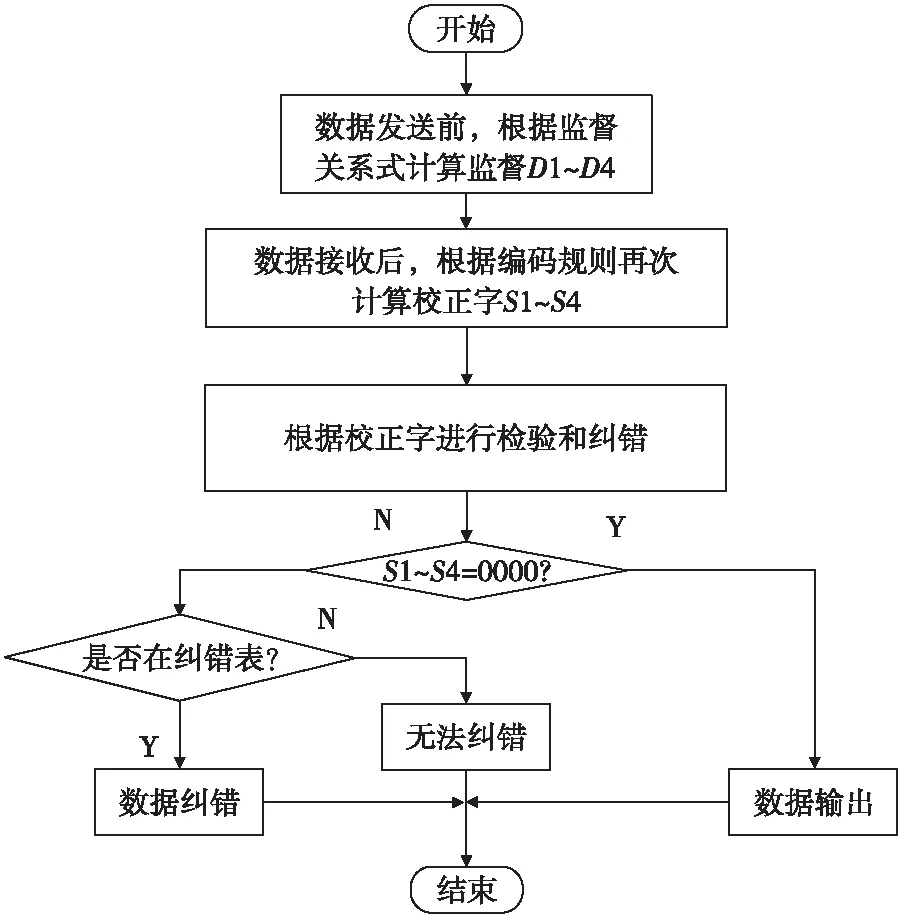

一級冗余編碼采用一位糾錯的漢明碼,該碼不僅算法簡單,易于硬件電路實現,而且編碼效率極高,在數據傳輸、存儲領域應用廣泛[11],漢明碼校驗流程圖如圖4所示。

圖4 明碼編碼流程圖Fig.4 Flow chart of clear code coding

數據傳輸過程中按字節發送,所以線性分組碼中(n,k)中的碼長n為8,為了保證監督位可以指示一位錯碼的所有可能,監督位r必須大于等于3[12],采集到的有效數據都是按字節存儲傳輸,故信息位k取4,則監督位也為4。數據傳輸時,每字節的有效數據都分成高4 bit、低4 bit,然后依次放入分組碼(8,4)編碼模塊進行編碼,根據分組碼構造關系,設計冗余位與監督關系,如表2所示。

表2 冗余位與監督關系構造表

根據表2可知,監督關系式為:

S1=D4⊕D6⊕D7⊕D8

(1)

S2=D3⊕D5⊕D7⊕D8

(2)

S3=D2⊕D5⊕D6⊕D8

(3)

S4=D1⊕D5⊕D6⊕D7

(4)

其中,D5、D6、D7、D8為數據位,D1、D2、D3、D4為校驗位,令S1、S2、S3、S4為0,便可以得到下式:

D1=D5⊕D6⊕D7

(5)

D2=D5⊕D6⊕D8

(6)

D3=D5⊕D7⊕D8

(7)

D4=D6⊕D7⊕D8

(8)

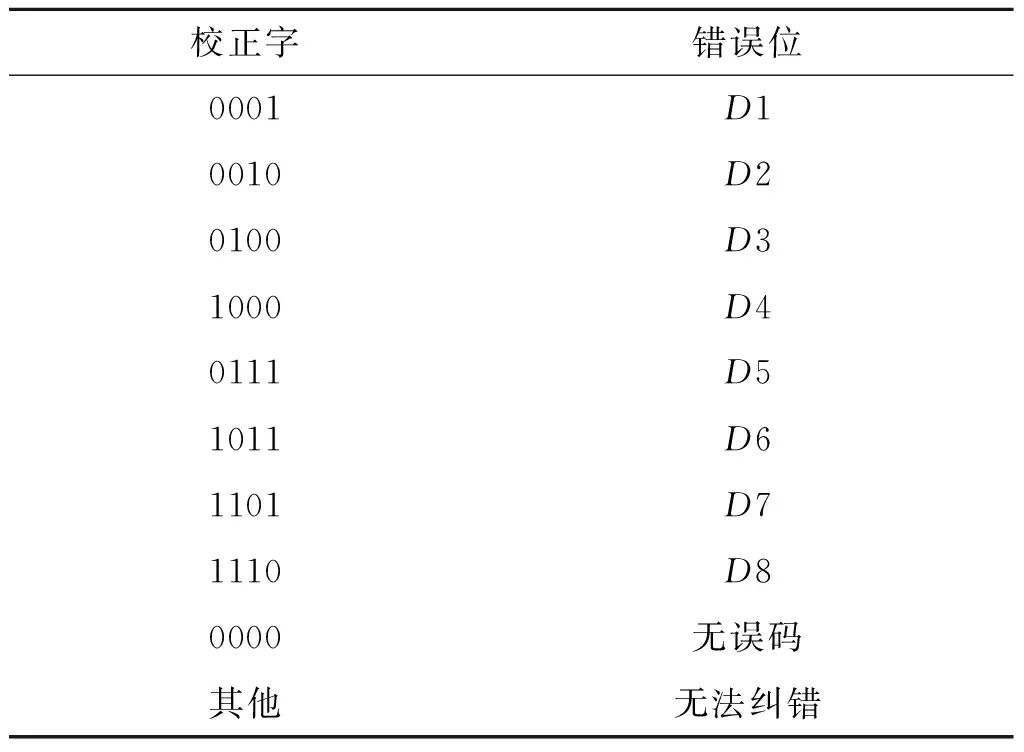

數據接收端接收數據后,根據監督關系式計算得到校正子S1、S2、S3、S4,若接收數據中僅存在一位錯誤數據,對照表3即可完成字內糾錯[13]。為了提高效率,一位糾錯時,僅對數據位糾錯即可。若錯誤位數超過兩位,則漢明碼無法完成糾錯,轉入二級冗余碼進行糾錯。

表3 錯碼查詢表

2.2 二級冗余編碼

數據傳輸過程中的錯誤大都小于等于1位,一級編碼就能解決糾錯,針對少部分的多位出錯,如果選擇復雜的校驗方式,不僅會進一步降低數據傳輸的有效帶寬,而且會占用過多的FPGA資源,降低系統工作效率,故二級校驗選用僅占一位校驗位的奇偶校驗。二級冗余編碼表如表4所示。

傳統的奇偶校驗僅能判斷奇數個錯誤,且不具備糾錯功能[14],然而文章中,處于二級冗余編碼的奇偶校驗,由于已經確定了誤碼位置和誤碼個數,使得奇偶校驗具備了糾錯的能力。

表4 二級冗余編碼表

根據表4可知,dj 為d1、d2、d3、d4的二級校驗,其中D8J、D7J、D6J、D5J是d1、d2、d3、d4數據位的偶校驗位,D8J作為D81、D82、D83、D84四位數據的校驗位,可以通過異或求得,同理也可求得D7J、D6J、D5J。同時為了保證四位偶校驗在傳輸過程中的準確性,對四位偶校驗數據也同樣進行字內的一級冗余編碼。

D8j=D81⊕D82⊕D83⊕D84

(9)

D7j=D71⊕D72⊕D73⊕D74

(10)

D6j=D61⊕D62⊕D63⊕D64

(11)

D5j=D51⊕D52⊕D53⊕D54

(12)

解碼時,首先進行字內漢明碼糾錯,如果錯誤位數超過兩位時,就要啟動字間的偶校驗進行二級糾錯,首先需要利用dj內的一級糾錯碼對二級冗余數據先行校驗,以防由于檢驗碼錯誤引起的誤糾現象發生。例如d1的數據位錯誤超過兩位時,可通過下式進行糾錯:

D81=D8j⊕D82⊕D83⊕D84

(13)

D71=D7j⊕D72⊕D73⊕D74

(14)

D61=D6j⊕D62⊕D63⊕D64

(15)

D51=D5j⊕D52⊕D53⊕D54

(16)

通過式(9)—式(12),便可完全恢復出d1的數據位,即實現對d1的四位錯誤數據的糾錯,同理也可對d2、d3、d4的多位糾錯。

當兩組內多位出錯時,如d1中的D81、D82出錯,而d2中的D62、D52出錯時,也可通過偶校驗對d1、d2兩組數據進行糾錯。

兩級冗余編碼完成后,由于LVDS編譯碼器可對10位并行數據完成串并轉化,為了有效利用硬件資源,同時應對傳輸過程中的碼間干擾,對發送數據流再進行直流平衡的8 bit/10 bit編碼。

3 可靠性驗證

為了驗證兩級冗余編碼能否提高數據傳輸系統的可靠性,可以先搭建試驗平臺,同時模擬測試環境,進行試驗驗證。測試平臺由地面測試設備、電纜網、采編器三部分組成。電纜網主要由240 m的屏蔽雙絞線構成,實現采編器數據的高速回傳。

實驗中,將采編器和電纜置于高低溫箱中,設置高低溫循環來模擬溫度環境,用函數發生器驅動場源發生器,產生空間磁場,模擬電磁環境。數據回傳到地面測試設備后,利用上位機嵌入的數據處理軟件,對回傳數據進行解包處理,分析傳輸過程中是否出現誤碼、丟數的現象。上位機接收的數據如圖5所示,其中“EB 90”為數據幀尾,“00 0F 9F EA~00 0F 9F F9”是幀計數,數據是F9~00的自減數。

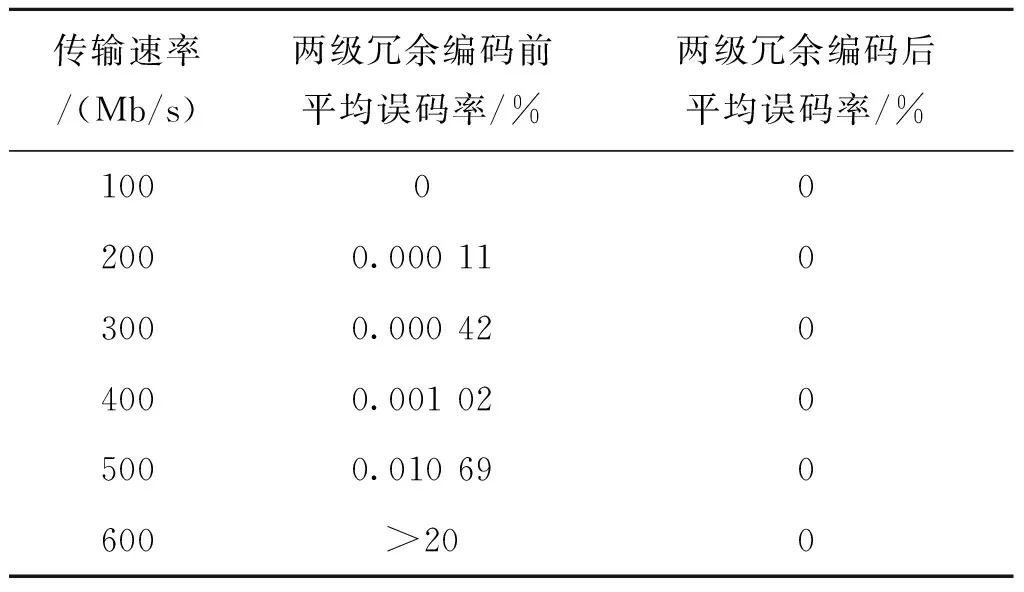

對照表5中的傳輸速率修改FPGA程序,依次測試每種傳輸速率的平均誤碼率,每個速率都進行60 次測試,每次測試傳輸的數據量約為32 GB,測試結果見表5。

圖5 上位機接收原始數據Fig.5 Upper computer receiving original data

表5 兩級冗余編碼測試結果表

根據表5可得,未進行冗余編碼時,僅憑硬件補償電路,可以使LVDS信號在240 m雙絞線中以100 Mb/s的速率無誤碼傳輸,隨著傳輸速率的增大,誤碼率會迅速增大。然而進行兩級冗余編碼后,可以明顯看出傳輸速率不斷增加時,平均誤碼率仍然為0。

通過對比兩級冗余編碼前后的試驗結果,可以發現在傳輸速率低于100 Mb/s時,編碼前后的平均誤碼率均為0,即冗余編碼不僅沒有提高數據傳輸的可靠性,還占用了部分有效帶寬。當傳輸速率位于100~600 Mb/s之間時,兩級冗余編碼明顯地降低了數據傳輸的誤碼率,提高了傳輸系統的可靠性。

根據表5的測試結果可知,應該根據傳輸速率和傳輸距離合理選用編碼方式。針對文章中惡劣環境中的遠距離高速的傳輸條件,選用冗余編碼實現了240 m屏蔽雙絞線上的600 Mb/s的無誤碼傳輸。

4 結論

本文提出了基于FPGA的兩級冗余編碼系統,該系統通過硬件優化和軟件優化相結合的方式,來提高數據傳輸過程中的穩定性。在硬件電路中,通過添加驅動器和均衡器,增強信號的傳輸能力;在軟件邏輯方面,通過兩級嵌套編碼,字內編碼實現字內的一位糾錯,字間編碼實現字內的多位糾錯,字內糾錯和字間糾錯相結合的編碼方式,來實現對數據傳輸過程的糾錯。環境試驗結果表明,在240 m的雙絞線上,兩級冗余編碼的傳輸系統可以以600 Mb/s的速率正確傳輸。該系統已成功應用于遠距離傳輸設備上。