TMS320C6678平臺軟件設計優化策略綜述

杭州應用聲學研究所 徐雅南 李恒光 范澤亞

德州儀器公司2010年推出的8核DSP芯片TMS320C6678是目前商用市場上計算性能最高的DSP之一,已在圖像處理、無線電通信基站、雷達和聲納等領域得到了一定范圍的應用。相比上一代被廣泛應用的TS201芯片,其優點是硬件規模大、工作主頻高、對外傳輸能力強和大容量外部存儲空間,缺點是平均內存小、架構復雜、共享資源競爭激烈和調度復雜。隨著芯片使用的日益頻繁,如何有效優化軟件架構,降低經濟成本,受到了軟件設計人員的廣泛關注。針對該問題,提出了一系列針對TMS320C6678的編程優化策略,為實現資源利用最大化提供了技術支撐。

TMS320C6678是德州儀器公司2010年推出的8核處理芯片,理論上單核具有128Gb/s(@1GHz)的單精度計算能力,是目前商用市場上計算性能最高的DSP(Digital Signal Processer)之一,已在圖像處理、無線電通信基站、雷達和聲納等領域得到廣泛應用。作為上一代被廣泛應用的TS201芯片的替代產品,TMS320C6678芯片的優缺點明顯,其優點是硬件規模大、集成度高,工作主頻高、操作數寬度大,對外傳輸能力強和大容量外部存儲空間,缺點是平均內存小,架構復雜,共享資源競爭激烈、調度復雜以及程序復雜度高。盡管TMS320C6678(4片)的理論運算能力約是TS201(6片)的16倍,但是不合理的軟件架構往往使得處理性能得不到有效發揮。針對該問題,本文提出了一系列編程優化策略,為實現資源利用最大化提供技術支持。

1 TMS320C6678簡介

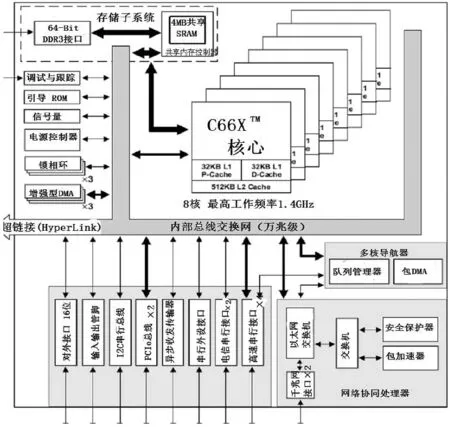

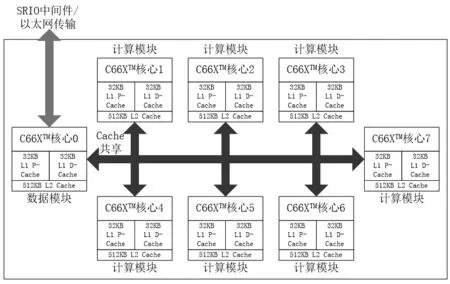

圖1 C6678處理器架構示意圖

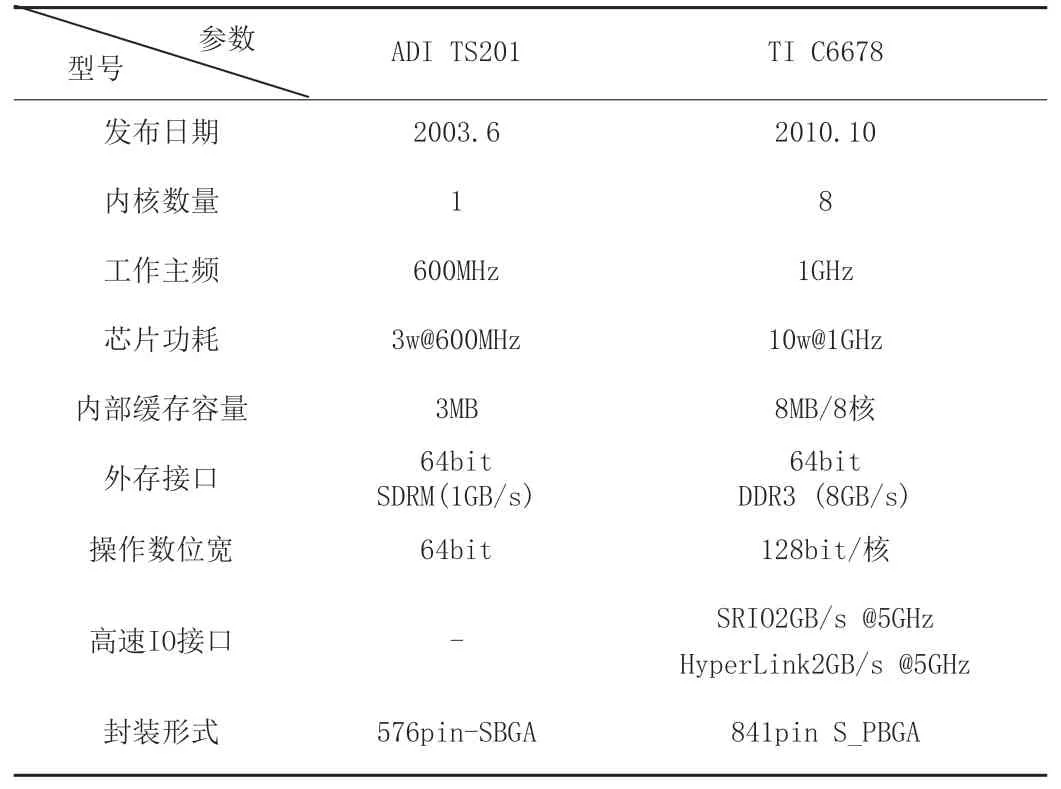

TMS320C6678(以下簡稱C6678)是TI公司的8核高速數字信號處理器之一,支持高速定點和浮點計算,單核主頻高達1GHz,擁有獨立的操作系統和L2SRAM空間,支持通過GPIO響應硬件中斷,外部通過EMIF和SRIO實現高速通信,核間通過消息隊列和共享內存進行同步和數據共享。C6678架構圖和工業用信號處理板分別如圖1所示,包括:32KB一級內存(Cache,L1D,L1P),512KB二級內存(本地內存,L2)、4MB三級內存(共享內存,MSMC)和2GB DDR3外掛存儲空間,3個EDMA控制器(10個通道)用于片內傳輸,4個SRIO快速串行輸入/輸出接口用于片間傳輸。C6678和TS201的主要參數對比見表1所示。目前工業上比較主流的C6678軟件開發環境(帶操作系統)主要以中電32所的銳華Rede和中科海訊的HaixunIDE為主,兩者雖然風格不同,但均滿足同一行業標準,核心能力和傳輸方式一致。

2 軟件設計優化策略

2.1 基礎優化策略

(1)合理使用MSMC區

C6678芯片8核共享4MB內存MSMC區別于外存DDR3,合理控制EDMA與CPU的訪問方式,可以實現MSM與L2之間數據傳輸的零開銷。建議將頻繁操作的全局變量定義在MSMC,以提高運算速度。

注意,兩兩變量做運算時,MSMC區變量的運算速度≥分別位于MSMC和DDR3的運算速度≥DDR3區變量的運算速度,但是不合理的使用會弱化MSMC的計算性能。

(2)優先使用“向量”

建議優先使用“向量”,不建議執行單點、跨步或轉置等操作,原因是C6678執行Cache刷新的基本單位為“塊”,單點、跨步或轉置等操作均會增加Cache開銷。此外,TI官方提供的基礎數學函數庫包含一系列向量操作函數,可顯著提高運算速度。

表1 C6678和TS201主要參數對比

(3)優化操作順序

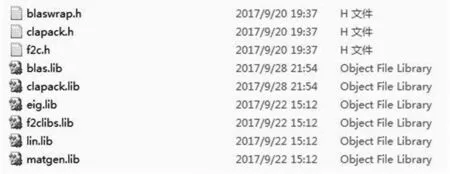

圖2 CLAPACK函數庫列表

圖3 并行計算架構示意圖

建議優化操作順序,減少多余Cache開銷。當CPU操作不同變量時,先將原Cache變量刷回原地址,再將后操作變量刷進Cache,因此,盡可能減少反復的變量切換操作可有效減少多余Cache操作。如:執行A、B、C、D求和,執行(((A+B)+C)+D)相比執行((A+B)+(C+D)),其Cache開銷更少,相應地運算性能更高。

2.2 使用CLAPACK等開源數學核心庫

Intel、AMD等公司針對自己的硬件處理器,Pentium、Xeon、Itanum開發了諸如BLAS和LAPACK等線性代數功能、離散傅里葉變化(DFT)以及向量超越函數(向量數學庫/VML),向量統計函數(VSL)。MATLAB之所以擁有強大的矩陣運算能力,主要是使用了BLAS、LAPACK和MKL等高度優化的數學矩陣運算庫。截止目前比較出名的核心數學庫以OpenBLAS、LAPACK和MKL為主。其中,LAPACK提供了Fortran和C語言兩個版本,本文主要是移植了一套適用C6678處理板的LAPACK的C語言版本——CLAPACK,結合編譯器O2優化選項(軟件排流水,刪除全局共有的表達式),有效提高C6678的數學運算效率。

首先,通過開源環境下載CLAPACK,解壓獲得/SRC、/BALS、/F2CLIBS、/LIB、/INCLUDE、TESTING和/INSTALL目次。再根據C6678底層宏定義對CLAPCK宏定義稍作修改。最后,利用REDE等開發環境自帶的交叉編譯器封裝形成blas.lib、clapack.lib、eig.lib、f2clibs.lib、lin.lib和matgen.lib共6項lib函數庫,如圖2所示。CLAPACK函數庫支持多級多類型向量、矩陣運算和向量矩陣等上千種復雜運算,彌補了C6678自身高性能函數庫缺乏的短板,其運算速度是普通函數運算的2到5倍。

2.3 軟件架構設計

C6678是一種典型的8核并行計算處理器。以下給出2種典型的軟件架構:

(1)并行計算架構。受8核共享數據總線和存儲空間限制,當并線計算開銷接近飽和時,8核并線計算無法將運算提高8倍(實測運算速度為6至7倍),此時建議采用如圖3所示軟件架構:單核作為對外數據傳輸模塊,負責片間數據傳輸及片內數據共享(Cache),其余7核作為核心計算模塊,負責片內并行計算并由單核匯總計算結果。由于單核同時負責內外部傳輸,一般建議單核啟用多線程,分別負責外部數據接收、內部數據共享和結果信息發送,其中外部數據接收、內部數據共享可以共用一個線程。

圖4 流水線架構示意圖

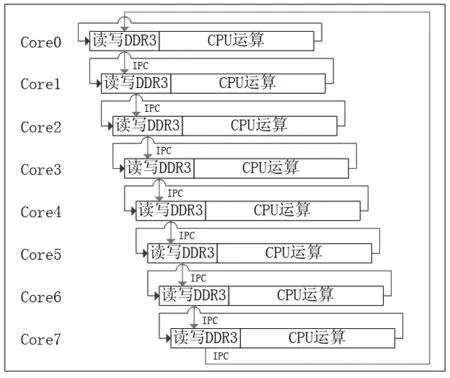

(2)多核流水線架構。通過控制8核流水線訪問DDR3外存,可以避開外存總線競爭,實現外存數據的全帶寬讀取與運算的并行,示意圖如圖4。

結束語:本文論述了TMS320C6678的編程優化策略,給出了通用軟件設計優化手段,為實現資源利用最大化提供了技術支撐。