高計數率氣體探測器讀出電子學原型機研制

孫志朋,佘乾順,趙紅赟,千 奕,*,孔 潔,蒲天磊,蘇 弘,袁江月

(1.中國科學院 近代物理研究所,甘肅 蘭州 730000;2.中國科學院大學 核科學與技術學院,北京 100049)

低溫高密核物質測量譜儀(CEE)是適用于蘭州重離子研究裝置-冷卻儲存環(HIRFL-CSR)能區[1]重離子碰撞和質子-重離子碰撞測量的帶電粒子譜儀,該譜儀由若干子探測器系統組成。高計數率(10 kHz)、高接受度的大型時間投影室(TPC)探測器是其中之一,包含有15 000個讀出通道。該探測器被用來鑒別帶電粒子,并測量輕帶電粒子的三維徑跡,其測量的主要反應產物包括π、p、d、t、3He、4He。由于探測器計數率高、通道多等特點,目前的讀出電子學無法滿足需求,因此迫切需研制適用于高計數率,且具有高集成度、低功耗、高分辨的新型讀出電子學。本文引進前端讀出專用集成電路(ASIC)芯片SAMPA[2-3],研制高計數率氣體探測器讀出電子學原型機,可解決HIRFL-CSR能區重離子碰撞和質子-重離子碰撞實驗中的帶電粒子譜儀計數率、功耗、串擾、堆積等問題,實現對高計數率TPC探測器信號的讀出。

1 原型機系統設計與實現

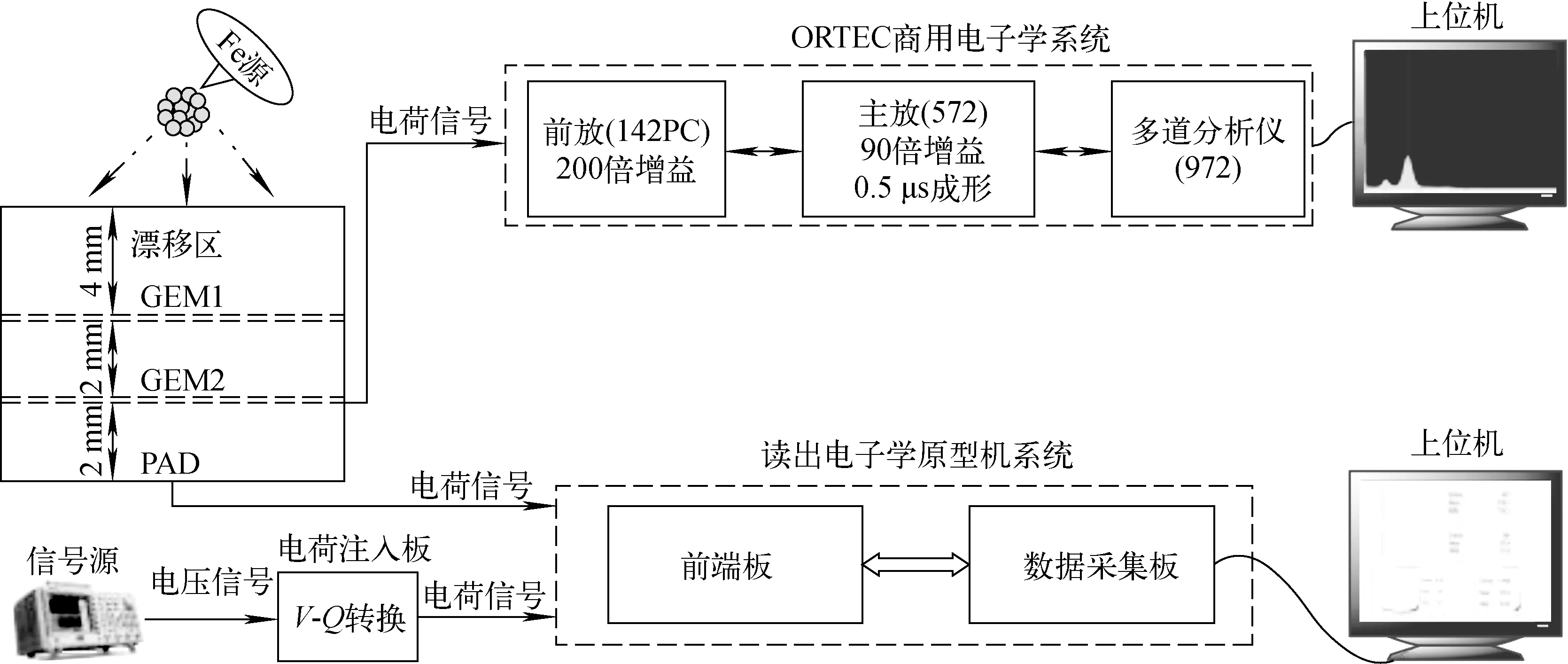

讀出電子學原型機系統主要由前端板、數據采集(DAQ)板和上位機構成,如圖1所示。

圖1 讀出電子學原型機系統Fig.1 Readout electronics prototype system

1.1 前端板設計

前端板負責接收來自探測器輸出的微弱電荷信號,并實現對電荷信號的積分、整形、模數轉換、數據壓縮及打包等功能。本工作兼顧功能、功耗和集成度等需求,在前端板的設計中采用一款前端讀出芯片SAMPA。前端板電路結構如圖2所示,其主要包括SAMPA芯片、過壓保護電路、電源管理模塊、適配網絡、芯片地址配置模塊、內部時鐘配置模塊、外圍濾波網絡、輸入高速連接器、輸出高速連接器和JTAG測試接口。過壓保護電路用來防止因TPC探測器打火而產生的大信號對前端電路造成破壞;電源管理模塊由低壓線性穩壓器(LDO)及其外圍電路組成,可提供前端板上各電路模塊所需的低噪聲的供電電壓和參考電壓;適配網絡可實現低壓差分信號(LVDS)到可擴展低壓信號(SLVS)的電平轉換并增強信號驅動能力,由于SAMPA芯片的輸入輸出信號均基于SLVS電平標準[4-5],而DAQ板上的Cyclone V型FPGA[6-8]的I/O管腳中,僅輸入管腳支持基于SLVS電平的信號,輸出管腳不支持基于SLVS電平的信號,因此從DAQ板上的FPGA輸出給SAMPA芯片的控制、時鐘、觸發等信號均基于LVDS電平標準,需通過適配網絡進行電平轉換;芯片地址配置模塊可實現對芯片硬件地址的配置;內部時鐘配置模塊用于配置片內時鐘管理單元產生SAMPA芯片內部所需的各種時鐘信號;外圍濾波網絡由濾波電容組成,實現對芯片各管腳的濾波,從而消除噪聲干擾;JTAG測試接口用于實現SAMPA芯片自帶的JTAG測試功能。

圖2 前端板電路結構Fig.2 Circuit structure of front-end board

SAMPA芯片是專門為TPC讀出研發的一款大規模的模擬數字混合芯片[9-12],具有高計數率、高集成度、低功耗等特點,其主要性能指標參數列于表1,SAMPA芯片內部結構如圖3所示。單片SAMPA集成32路輸入通道和11條輸出鏈路,單通道內包含電荷靈敏前放(CSA)、成形電路(Shaper)、驅動電路(Non-Inverting stage)、10 bit精度的模數轉換器(ADC)、功能復雜的數字信號處理器(DSP)、慢控模塊和接口電路等。

圖3 SAMPA芯片內部結構Fig.3 Internal structure of SAMPA chip

表1 SAMPA芯片參數Table 1 Parameter of SAMPA chip

前端板接收到探測器輸出的電荷信號后,被SAMPA芯片中的CSA放大并轉換為電壓信號,然后通過Shaper整形為準高斯電壓信號,再送入10 MHz采樣率的ADC進行數字化。DSP包含3級基線修正,可對數字化后的信號進行實時處理,從而消除信號擾動、脈沖波形的畸變及由于溫度變化帶來的信號基線變化[13]。經過基線處理后,DSP中的壓縮級對數據進行壓縮,并將壓縮后的數據送入數據打包級打包后暫存,最終通過11條鏈路輸出到后端的DAQ板[14]。

1.2 DAQ板固件設計及上位機

DAQ板以Cyclone V SX型FPGA芯片為核心,搭載1片1 GB的DDR3芯片,并配置有USB慢控接口和千兆以太網接口。Cyclone V SX型FPGA的輸入端口支持SLVS標準,可直接接收SAMPA芯片異步輸出的速度高達320 Mbps的SLVS信號;FPGA帶有片上處理器系統,其內部由可編程邏輯(PL)和內嵌硬核處理器(HPS)兩部分構成,PL端和HPS端通過Avalon總線進行交互[15]。圖4為DAQ板固件結構示意圖,DAQ板的固件可劃分為3大模塊,分別為數據處理模塊、指令控制模塊和數據傳輸模塊。其中,數據處理模塊和指令控制模塊在PL端實現,數據傳輸模塊在HPS端實現。數據處理模塊負責接收來自SAMPA芯片的數據,并進行一系列在線處理,然后將有效數據通過Avalon總線傳輸到HPS端;HPS端的數據傳輸模塊通過千兆以太網將數據傳輸到上位機后進行存儲;上位機通過USB-UART下發的控制指令到達DAQ固件后,指令控制模塊根據指令完成前端板上各芯片的參數配置、觸發處理、狀態監測等操作。

圖4 DAQ板固件結構示意圖Fig.4 Scheme of DAQ system firmware

數據處理模塊內部包括同步子模塊、串并轉換子模塊、在線判選子模塊、FIFO子模塊和輪詢子模塊。同步子模塊負責監測SAMPA的11條輸出鏈路狀態,并異步接收芯片輸出的數據。串并轉換子模塊將接收到的串行數據轉換為適合于后端操作系統處理的64 bit寬度的數據。在線判選子模塊對接收到的數據包進行判選,丟棄無效包,將有效數據包寫入FIFO進行緩存。輪詢子模塊將11條鏈路對應的11個緩存FIFO分為4組,分別以輪詢的方式進行可靠讀出,在讀出的過程中監測并丟棄因FIFO溢出而導致的不完整包,之后通過4個Avalon總線端口將數據傳輸到HPS端,進行DDR緩存處理并最終上傳。HPS端利用外掛DDR芯片進行內存映射,用于緩存數據并運行Linux操作系統,數據傳輸模塊是1個運行在Linux操作系統下的代碼模塊,該模塊建立基于TCP/IP傳輸協議的傳輸鏈路并監測以太網狀態,將數據流進行可靠傳輸。

上位機通過USB-UART下發的指令流經過Avalon總線的橋接送到指令控制模塊,該模塊含有IIC驅動、觸發處理和SAMPA管腳控制3個子模塊。IIC驅動子模塊根據收到的指令參數,產生滿足IIC時序的信號,設置前端板上SAMPA芯片內部的寄存器參數;觸發處理子模塊接收來自外部的觸發信號并處理為SAMPA芯片可識別的信號,輸出給前端板并觸發SAMPA芯片開始工作;管腳控制子模塊通過控制SAMPA芯片的部分管腳,選擇芯片的工作模式并對部分參數進行設置。

2 測試與討論

2.1 實驗室性能測試

電子學系統基線穩定性、通道積分非線性和通道能量分辨是判定系統性能的關鍵指標。本工作利用信號源注入信號對讀出電子學原型機系統的性能指標進行了測試。在測試過程中,電子學原型機系統被置于屏蔽盒內,以屏蔽外部干擾。

1) 原型機系統基線穩定性

在無輸入的情況下,采集原型機系統32個通道的基線噪聲信號,在對共計超過35萬個數據包進行分析后,得到的結果列于表2。可看出,系統所有通道的基線變化穩定,均方根(RMS)均小于0.95個ADC道(對應0.1 fC電荷量),滿足CEE TPC系統對讀出電子學提出的低噪聲需求。

表2 基線噪聲測試結果Table 2 Baseline noise test result

2) 原型機系統能量分辨及積分非線性

設定信號源輸出頻率為10 kHz的指數衰減信號,通過電荷注入板轉換為電荷信號后輸入到SAMPA芯片中,進行能量分辨及積分非線性測試。設置SAMPA芯片的CSA增益為20 mV/fC,整形級達峰時間為160 ns,給定輸入電荷量為66 fC時,對輸出信號采集超過10 000個數據包。經波形擬合和數據分析處理,得到信號的能譜如圖5所示。其中系統的能量分辨為1.4個ADC道(對應電荷量為0.14 fC)。

圖5 輸出信號能譜Fig.5 Energy spectrum of output signal

改變信號幅度,在2.2~99 fC范圍內,共給出10個輸入電荷量,每個輸入對應的輸出波形被ADC采集超過10 000個數據包。對輸出的波形進行擬合得到其對應的最大幅度信息并進行分析,進而得到系統在輸入動態范圍內的積分非線性。選取通道0的分析結果進行展示,該通道輸出電壓(ADC道值)的線性擬合結果如圖6a所示,積分非線性好于0.24%;殘差分布如圖6b所示,其變化小于±2ADC道(對應電荷量為±0.2 fC)。

a——線性擬合結果;b——擬合殘差分布圖6 讀出電子學原型機系統積分線性Fig.6 Linearity of readout electronics prototype system

2.2 與GEM-TPC探測器聯合測試

本文利用55Fe放射源對原型機系統和商用電子學系統進行了能量分辨率、計數率等指標的對比測試,測試系統結構如圖7所示,包括基于雙層氣體電子倍增器(GEM)的TPC探測器、讀出電子學原型機系統、ORTEC商用電子學系統。

圖7 測試系統結構Fig.7 Structure of test system

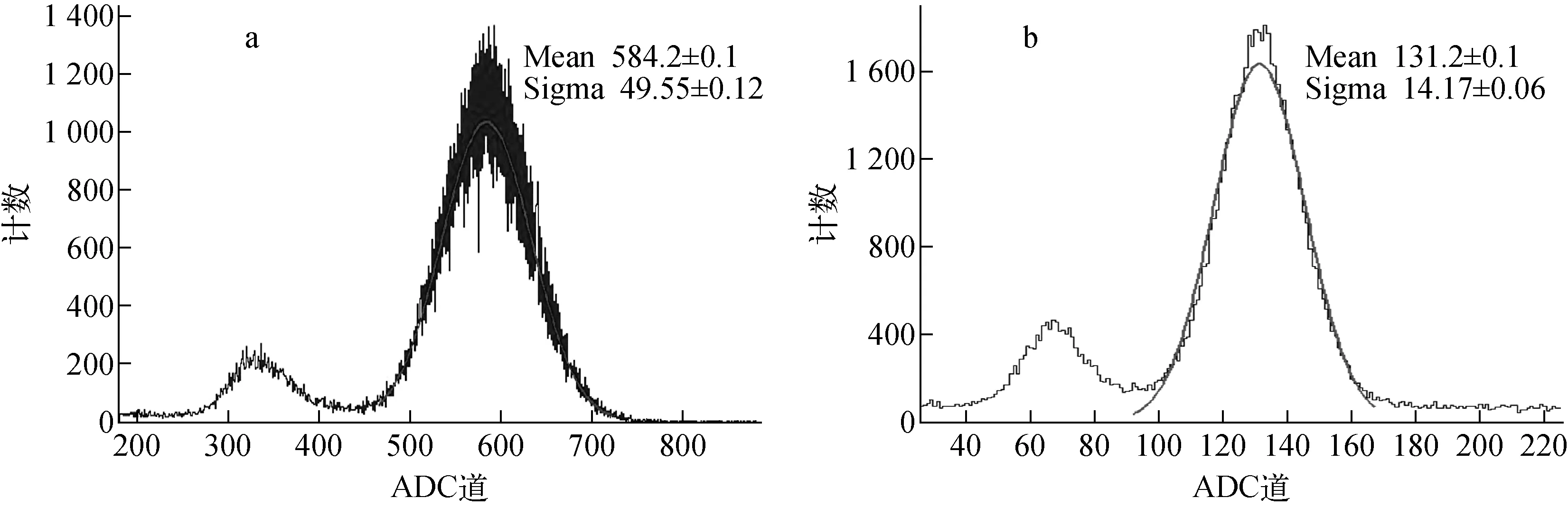

2.3 能量分辨率測試結果

測試前,利用定標器測得55Fe放射源事件率約為11 kHz。讀出電子學原型機系統和ORTEC商用電子學系統同時測試,讀出電子學原型機系統通道0的測試結果如圖8a所示。利用式(1)計算得到電子學的能量分辨率R1為23.52%;在相同條件下商用電子學系統測試結果如圖8b所示,由于商用電子學系統基線接近0,可忽略不計,利用式(2)求得ORTEC商用電子學系統的能量分辨率R2為25.49%。測試結果表明,在相同條件下,讀出電子學原型機系統的能量分辨率優于商用電子學系統。

(1)

(2)

其中:Baseline為原型機系統基線噪聲值;Mean為電子學測得的能譜經高斯擬合后得到的中心值。

a——讀出電子學原型機系統;b——ORTEC商用電子學系統圖8 55Fe放射源測試能譜Fig.8 Energy spectrum obtained by 55Fe source

調整55Fe放射源的位置,利用定標器測得事例率約為23 kHz,讀出電子學原型機系統測得的能譜如圖9所示。利用式(1)計算求得原型機系統的能量分辨率R3為22.79%,在計數率增加1倍的情況下,原型機系統的能量分辨率沒有變差,說明系統可適用于計數率高于20 kHz的GEM-TPC探測器的讀出。

圖9 讀出電子學原型機系統能譜Fig.9 Energy spectrum of readout electronics prototype system

3 結論

本文介紹了一套適用于高計數率TPC探測器的讀出電子學原型機系統的設計與實現。利用構建的測試系統對原型機的基線噪聲、積分非線性、能量分辨及高計數率下的工作性能進行了測試,結果表明系統具有良好的性能。通過與探測器進行聯合測試,驗證了電子學系統在實際工作中的性能指標良好,能滿足CEE中TPC探測器的讀出需求。該系統結構緊湊,通用靈活,指標先進,為后續CEE中TPC探測器前端電子學的設計提供了技術參考,也為CEE中TPC實驗探測系統的建造提供了重要技術保障。

感謝挪威Bergen大學和法國IPN Orsay實驗室對本工作提供的技術支持。