基于FPGA 的頻譜分析儀設計

張亞周,張家運,孫艷麗

(1.海軍航空大學 航空基礎學院,山東 煙臺 264001;2.海軍航空大學 學員4 隊,山東 煙臺 264001)

頻譜分析儀是測量高頻信號常用的儀表,主要測試失真、交調、寄生、噪聲邊帶等參數[1-3]。當前實現方式主要有3 種:1)采用通用數字信號處理芯片實現;2)采用專用TFT 芯片和數字信號處理芯片相結合;3)采用FPGA 實現[3-4]。采用數字信號處理芯片,通常對速度要求較高,或受數字濾波器影響無法實現高頻率和高速率[5-6]。而FPGA 具有邏輯時序控制以及強大運算能力,能夠解決上述問題[7-8]。文中設計的模擬式頻譜分析儀以FPGA 為核心,主要包括振蕩器、混頻、濾波以及顯示部分。其中本振源模塊主要采用MHC830 芯片設計鎖相環的信號發生器;混頻模塊利用AD835 乘法器將輸入信號與本振信號進行混頻得到中頻信號;混頻后的中頻信號經過信號處理模塊以中心頻率為10 MHz 進行濾波;頻譜圖顯示模塊對輸出信號進行編碼以及在顯示器上顯示。這種方法的優點是掃頻范圍大,硬件成本低廉,主要用于測量穩態信號的頻率幅度。

1 鎖相環本振源工作原理

鎖相環電路主要包括晶振、鑒相器、分頻器、壓控振蕩器、低通濾波器,并留有數據控制接口[9-10]。晶振產生由自身決定的固定頻率(Fref)信號,經分頻器進行R分頻后輸入到鑒相器,在鑒相器中將該信號與壓控振蕩器輸出頻率(Fout)信號進行N分頻后的信號進行比較,將比較的相位差以模擬信號方式輸出,并通過LFP 濾波加到壓控振蕩器的調制端,從而控制鑒相器兩輸入頻率相等。電路的計算公式:

輸出信號頻率與N和R密切相關,因此設置合適的參數即可將鎖相環電路作為本振源。

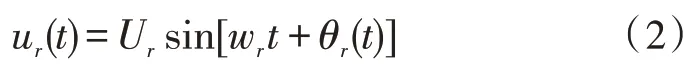

設輸入信號為:

式(2)中,Ur、wr分別為輸入信號的幅值和頻率,θr(t)是以載波相位為基準的瞬時相位,如果載波信號是未調載波,則θr(t)=θr,為常數。

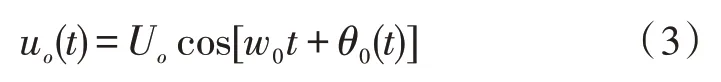

設輸出信號為:

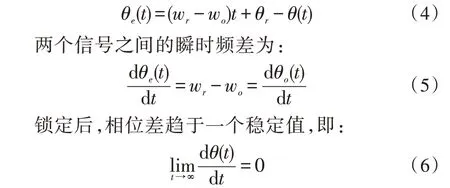

式中,uo、w0分別為輸出信號的幅值和壓控振蕩器輸出頻率,θ0(t)是輸出信號的瞬時相位,其初始值是常數,在VCO 受到控制時就與時間相關。兩個信號的瞬時差為:

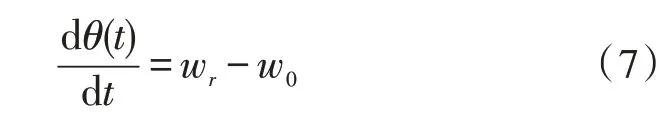

此時,輸出信號的頻率已經偏移原來的自由振蕩頻率w0,偏移量表示為:

其輸出信號的工作頻率為:

由式(8)可見,基于鎖相環的跟蹤特性,輸出信號頻率等于輸入信號頻率,從而達到同步且相位差恒定。

2 超外差頻譜儀工作原理

超外差就是將由本地振蕩器產生的信號與輸入混頻,從而將輸入信號的頻率設置為某設定的頻率(由差頻的作用產生),然后再進行放大和檢波。

2.1 混頻器工作原理

混頻就是制造—個振蕩電波(即本振源),使該信號與外來已調波同時送到非線性器件進行混合,由于晶體管的非線性特性,使得輸出產生一個新的頻率信號[11]。外差作用產生出來的差頻,習慣上采用易于控制的一種頻率,它比高頻較低,但比音頻高,這就是常說的中間頻率,簡稱中頻。混頻器產生的中頻信號等于兩輸入信號頻率之和、差或其他組合的變化頻率,通常由非線性元件和選頻回路構成[12-13]。將混頻器輸出的中頻信號通過中頻放大器放大后,進行峰值檢波。混頻的作用就是將已調波的頻譜不失真地由高頻搬移到中頻的位置上。該設計中綜合考慮到功耗、失真、誤差、電路的增益、設計及調試等因素,選取TI 公司生產的模擬乘法器(AD835)混頻。

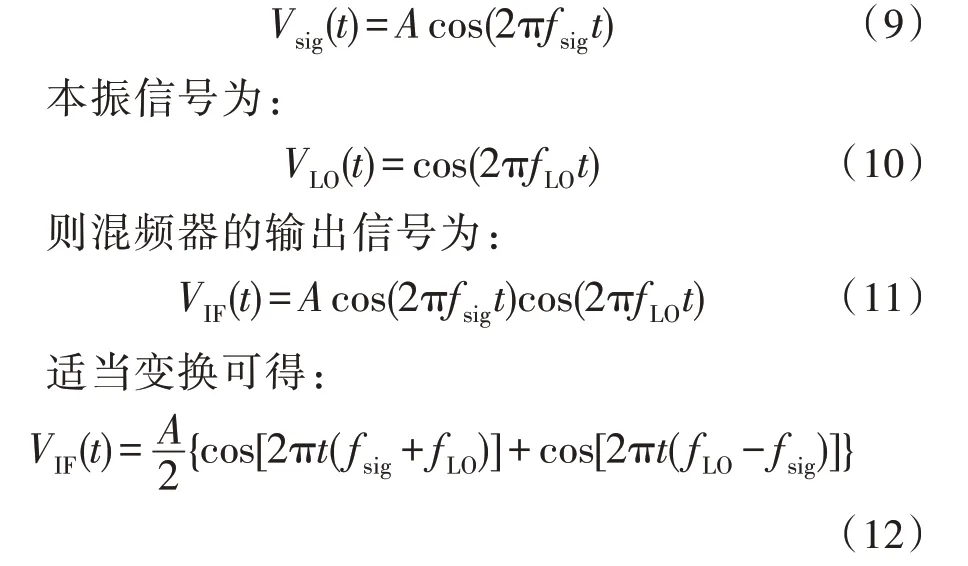

在理想情況下,假定輸入信號為:

式中,fsig為輸入信號頻率,fLO為本振信號頻率。可知混頻器輸出頻率是本振信號和輸入信號頻率之和與之差,實現頻譜搬移。

2.2 包絡檢波器原理

包絡檢波器是一種基于濾波檢波的振動信號處理方法[14-16],它可以對輸入信號進行處理,把中頻信號轉換成視頻信號,以便顯示并測量輸出信號。包絡檢波通常是先采用二極管進行單向過濾,然后再進行低通濾波,如果不采用二極管而直接進行低通濾波,則會抵消正、負包絡線,從而無法檢出低頻信號。ADL5513 是一款解調包絡(對數)檢波器,響應時間短、穩定性好、功耗小、測量精確度高、誤差小,故本次設計選取ADL5513 作為檢波器。

3 電路的設計

3.1 硬件系統框圖

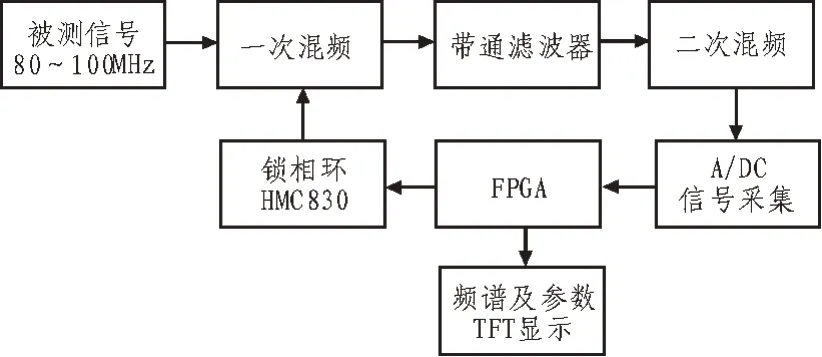

為了實現在80~110 MHz 頻率范圍,時間1~5 s之間的不同掃頻速度和步進100 kHz 的頻譜分辨率,系統采用了一次下混頻、濾波結構和模擬濾波法,選取HMC830 作為鎖相環芯片充當本振源,選用了AD835 模擬乘法器混頻和ADL5513 對數檢波器檢波,并選取了AD 采樣電路。系統框圖如圖1 所示。

圖1 硬件系統框圖

3.2 鎖相環本振源及相位鎖定電路設計

HMC830LP6GE 具有精度高、寬帶寬的優點,文中設計使用該鎖相環芯片充當本振源,它集成了小數分頻的VCO、PFD、分頻器,芯片內部集成可控信號輸出功能,滿足輸出電壓10~100 mV 的要求,同時該芯片提供了相位鎖定指示,通過FPGA 及相關信號處理即可。

3.3 一次/二次混頻器設計

AD835是一款性能優異的模擬乘法器,帶寬可以達到250 MHz,滿足該設計最大110 MHz 輸入信號的要求。若是一次混頻后,差頻為10.7 MHz,對后端電路處理帶來難度,因此采用10.235 MHz 的頻率源對信號進行下變頻處理,將信號頻率變到465 kHz。

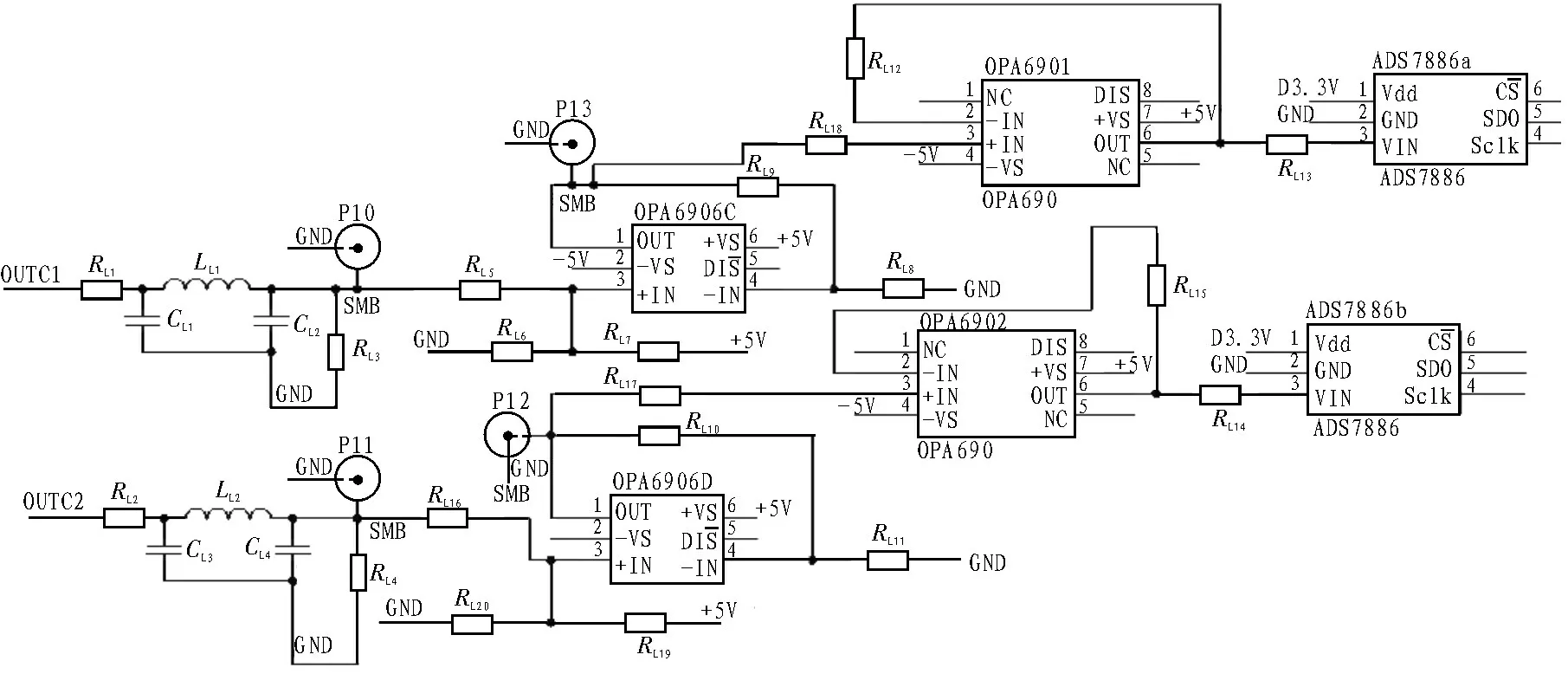

實際測試過程中發現隨輸入頻率變化,AD835輸出信號幅度會出現一定程度的衰減,為了保證混頻器正常工作,使用OPA690 作為基礎芯片設計制作了增益調理模塊。經測試,在80~110 MHz 的頻率帶寬下,幅度和相位不會出現明顯失真,符合系統對混頻器的要求,加入增益放大模塊后電路可以正常工作。

3.4 AD608電路設計

AD608 內部包含混頻器、限幅器,具有接收信號強度指示功能。此次設計,使用該芯片及其外圍電路作為輔助驗證系統,電路原理以及電路設計圖如圖2 所示。

圖2 AD608電路設計圖

4 程序設計

4.1 程序設計思路

超外差頻譜分析儀調節本振源的頻率步進輸出,同時采集不同頻點信號的幅度,將兩者記錄后得到幅度隨頻率變化的曲線,即為頻譜分析的結果。該設計中利用FPGA 調節HMC830 本振源的頻率,同時對中頻A/DC 采集的信號強度進行記錄,最后在TFT 彩色屏上顯示被測信號的頻譜。

4.2 信號頻譜顯示及雜散計算

需要顯示的頻譜圖由201 個頻率點組成,對應VGA 顯示屏的201 列,同時將信號強度分別放置到不同行使用不同顏色顯示。

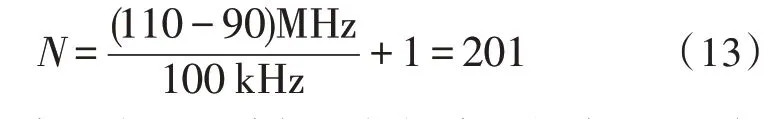

當頻譜分辨率為100 kHz 時,頻率范圍為90~110 MHz,則頻率調節點個數為:

設主頻分量為A0,則大于主頻分量幅度2%的雜散頻率個數S的計算方法為:

5 測試結果及分析

5.1 鎖相環本振源測試結果分析

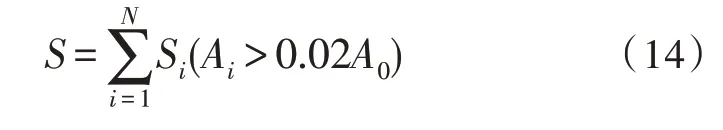

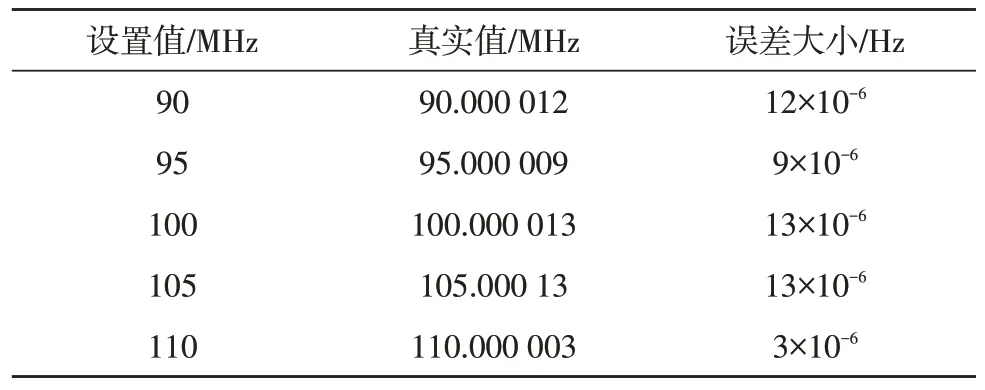

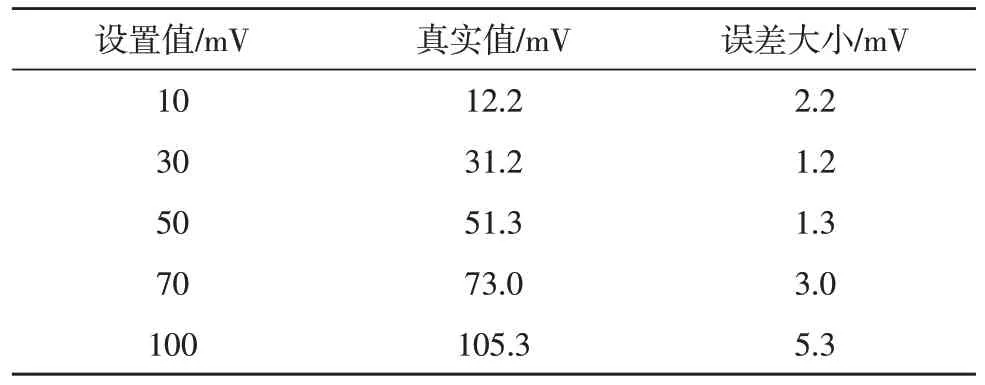

頻率測試和幅度測試結果分別如表1、表2 所示。由表1 和表2 可以看出,在所選測量點處,頻率測試誤差均小于13×10-6MHz,而幅度測試誤差小于5.3 mV,可以滿足信號的測試要求。

表1 頻率測試

表2 幅度測試

5.2 頻譜分析儀測試結果分析

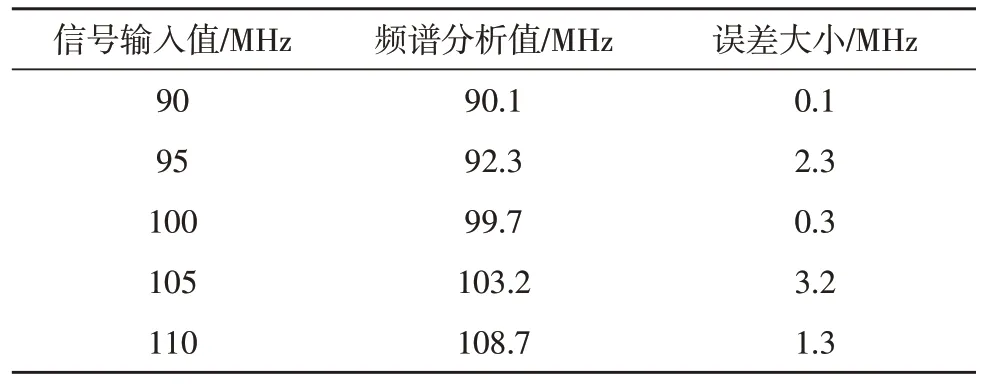

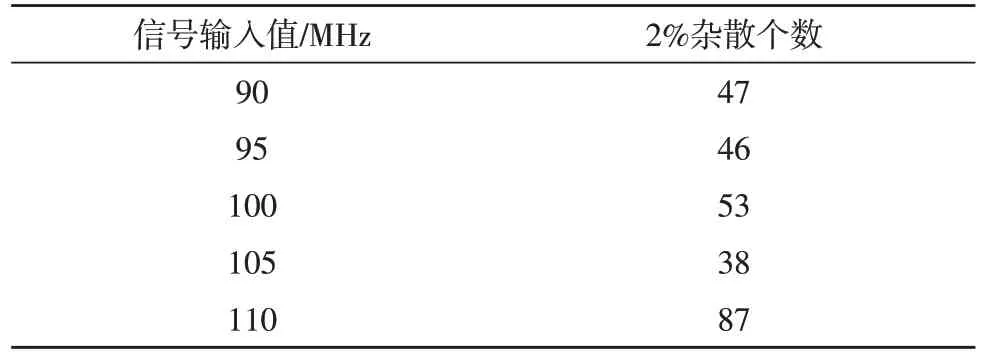

頻率分析和雜散測試結果分別如表3、表4 所示。由表3 和表4 可以看出,頻率分析的相對誤差均小于3.1%,且可以準確測試雜散頻率個數,測試性能良好。

表3 頻率分析

表4 雜散測試

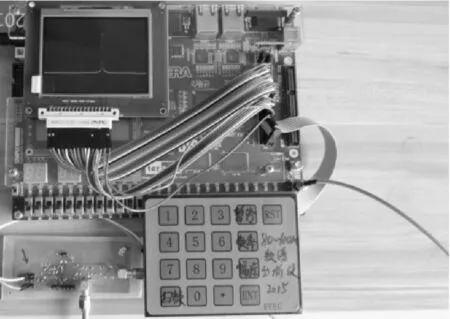

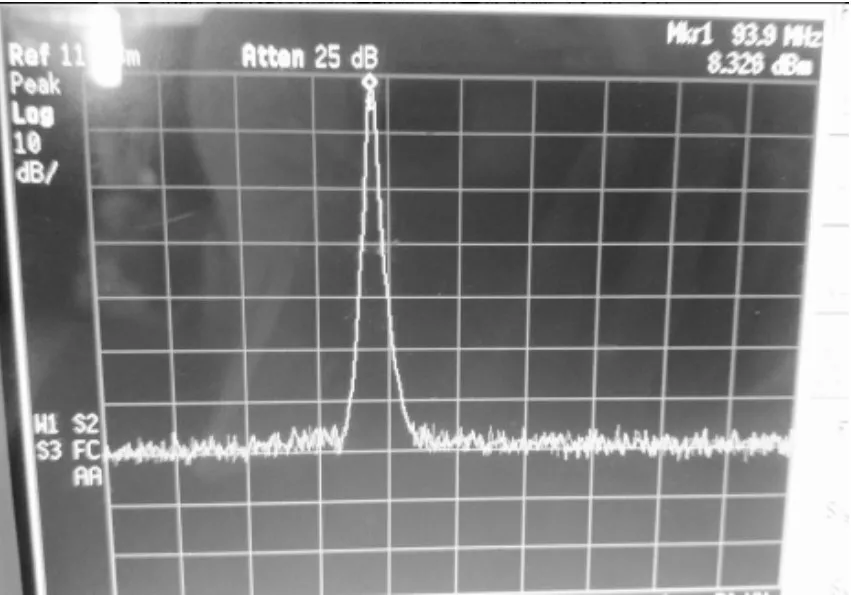

設計作品實物圖和示波器顯示鎖相環輸出調試圖分別如圖3、圖4 所示。

圖3 實物圖

圖4 鎖相環輸出調試圖

6 結論

該系統根據設計要求基于超外差式原理,并結合高速可編程邏輯器件FPGA 設計而成。通過測試與分析,系統整體指標良好,可在80~110 MHz 頻段內掃描并顯示信號頻譜和對應幅度最大的信號頻率,輸出電壓幅度為10~100 mV分辨率達到了100 kHz,還能夠測試在全頻段內的雜散率個數。并且在整個頻率范圍內可自動掃描,掃描時間在1~5 s 之間可調,具有良好的人機接口,操作非常方便,整機便于攜帶,解決了傳統示波器價格昂貴問題,適合高校的課程設計或電子創新實踐活動。