片上多通道低電容系統級靜電防護電路設計

許建蓉,汪西虎,劉 偉,李 晶

(西安郵電大學 電子工程學院,陜西 西安 710121)

USB Type-C 是目前電子設備中使用最多的接口類型,在數據傳輸方面,每個通道的傳輸速率可以達到10 Gbps;在物理結構上,采用雙面對稱結構,支持正反插;在功能方面,能夠集數據傳輸、音頻傳輸、功率傳輸于一體;在應用方面,涉及手機、商務筆記本電腦、顯示器等多個領域[1-2]。由于Type-C 接口的工作特性及應用環境需要其支持熱插拔動作,導致接口容易受到靜電放電的影響,因此需要為接口提供系統級靜電保護[3]。目前,絕大多數Type-C 接口采用片外放置瞬態電壓抑制二極管(Transient Voltage Suppressor,TVS)器件的方案達到系統級靜電要求,不利于芯片的小型化,而且Type-C 接口對數據傳輸的容錯率有嚴格要求,因此需要根據Type-C 接口的防護需求及實際工作環境在單芯片上集成多通道的系統級靜電防護電路,同時保證端口的低電容特性,提高接口的可靠性。

Type-C 接口中,兩組D+、D-引腳用于傳輸USB2.0 的數據信號;CC1 和CC2 作為配置通道,配置不同的模式;SBU1 和SBU2 作為邊帶通道,用來傳送輔助信號[1-3]。芯片正常工作時D+、D-引腳的最高電壓為5.5 V,將其定義為低壓端口;CC1、CC2、SBU1 和SBU2 引腳的最高電壓能夠達到24 V,將其定義為高壓端口。為保證接口的可靠性,對ESD(靜電放電)端口防護電路提出相關可靠性指標:抗靜電能力達到IEC61000-4-2 接觸放電±8 kV;D+、D-端口電容需小于2 pF,CCX 端口電容需小于100 pF,SBUX 端口電容需小于10 pF。因此需要針對8 個端口提供相應的低電容、系統級靜電防護方案。文獻[4]提出一種襯底改造的GGNMOS,該結構具有較低的觸發電壓,但是由于其增加了額外的電源軌控制PMOS輔助觸發襯底部分,使整體電路的版圖面積和寄生電容有所增加,不適用于多通道低電容的ESD 防護;文獻[5]針對可控硅整流器(SCR)防護結構觸發電壓較高問題,提出利用PMOS 器件觸發的SCR 結構,降低了觸發電壓,但其容易造成閂鎖問題;文獻[6]對GGNMOS 結構進行改良,提出一種GGNMOS+RC NMOS 的ESD 防護結構,使電路防護能力達到IEC61000-4-2 接觸放電±2 kV。以上文獻中的方案只能滿足部分要求,并不能同時滿足多通道、低電容和系統級靜電防護的要求。鑒于此,本文提出基于導流二極管與ZCNMOS 結構構建的系統級靜電放電保護架構,通過ZCNMOS 結構泄放ESD 大電流,利用導流二極管隔離靜電泄放器件的大電容,保證端口信號完整性。

1 電路設計

1.1 靜電防護架構設計

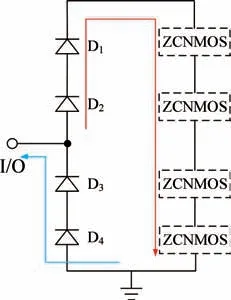

本設計分別針對低壓端口和高壓端口提出靜電防護方案,圖1 所示為基于ZCNMOS 結構的低壓端口防護電路,通過導流二極管D1-D4可降低端口電容。當正向ESD 脈沖來臨時,導流二極管D1和D3導通,將電流導向ZCNMOS 結構,再經ZCNMOS 結構將電流泄放至地,則I/O 端口的鉗位電壓約為D1正向導通電壓Vbe與ZCNMOS 結構上的壓降之和,同時需要保證正向脈沖來臨時,二極管D2的耐壓值高于I/O 端口鉗位電壓,防止其被反向擊穿;當反向ESD 脈沖來臨時,導流二極管D2和D4導通,泄放自地至I/O 端口的靜電,則I/O 端口電壓被D2或D4鉗位在正向導通電壓Vbe左右,同時需要保證二極管D2和D4具有較高的泄流能力。D+、D-兩個引腳共用一個ZCNMOS 結構,可將低壓端口ESD 防護電路的版圖面積縮減至原來的1/2。

圖1 低壓端口防護電路Fig.1 Protection circuit of low-voltage port

基于ZCNMOS 結構的高壓端口防護電路如圖2 所示,采用ZCNMOS 結構級聯方式提高觸發電壓,大電流泄放通路與低壓端口相同。由文獻[7]可知,當芯片發生熱插拔事件時,由于振鈴效應,高壓端口的瞬態電壓峰值約為最高電壓的1.8 倍,即44 V 左右,因此二極管D1、D4的反向擊穿電壓必須高于44 V;由于反向擊穿電壓高的二極管正向放電能力較弱,為保證過流能力,二極管的結面積必然較大,不易滿足低電容的要求。為此,通過串聯低擊穿電壓、低電容的二極管D2和D3將I/O 端口與ZCNMOS 結構中靜電泄放器件的大電容進行隔離,從而降低端口電容。CC1、CC2、SBU1 和SBU2 引腳共用一個ZCNMOS 結構,可將高壓端口ESD 防護電路的版圖面積縮減至原來的1/4,減少整體版圖面積。

圖2 高壓端口防護電路Fig.2 Protection circuit of high-voltage port

1.2 ZCNMOS 結構設計

GGNMOS 結構在ESD 防護電路中應用非常廣泛,為了保證較大的襯底電流,MOS 管采用叉指結構,導致MOS 管中寄生雙極性晶體管出現不均勻導通的現象,有可能只有2~3 根叉指優先導通。此時,ESD 防護能力相當于2~3 根叉指的防護能力,導致ESD 防護能力降低[8-9],這也是ESD 設計的瓶頸所在。因此,本文對 GGNMOS 進行優化,設計柵極耦合的ZCNMOS 結構進行靜電防護。

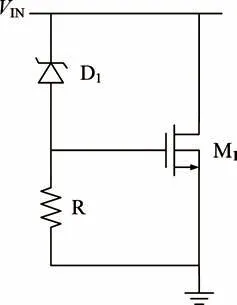

ZCNMOS 結構如圖3 所示,M1表示高壓隔離型5 V 靜電泄放器件,為了保證過流能力,采用叉指結構,D1為穩壓二極管,電阻R 用來限制流過D1的電流,防止MOS 管M1柵氧擊穿。當端口發生ESD 事件時,二極管D1反向擊穿,使電阻R 上產生一定的壓降,M1的柵極在應力作用下被瞬時上拉[10]。當柵極電壓達到閾值電壓之后,MOS 管M1導通,隨著電流的增加,電流向下走并從襯底流出,使P 阱電阻上的壓降達到0.7 V,則寄生晶體管NPN 導通,開始泄放ESD 大電流。與GGNMOS 相比,ZCNMOS 結構利用二極管與電阻在MOS 管M1的柵極耦合一定的電壓,使MOS 管M1導通,代替GGNMOS 中PN 結擊穿產生的襯底電流,因此具有更低的觸發電壓,而且會產生更高的襯底電流,有利于雙極晶體管的導通,從而保證叉指器件均勻開啟[11]。

圖3 ZCNMOS 結構Fig.3 Structure of ZCNMOS

根據芯片的設計要求,當芯片正常工作時,為了保證防護電路不被誤觸發,ZCNMOS 結構必須具有一定的耐壓值。當端口發生ESD 事件時,穩壓二極管被擊穿,并且隨著VIN的不斷升高,M1的柵極電壓達到其閾值電壓VTH(1.5 V)時,M1管完全導通,泄放大電流,通過穩壓二極管D1和MOS 管M1的作用,使ZCNMOS 結構的單級鉗位電壓約為二極管穩壓值(6 V左右)與MOS 管柵源電壓VGS之和,即7.5 V 左右。為了設計安全考慮,應保留10%的設計余量,因此M1管的漏端和源端的Vds耐壓值至少需要高于8.5 V,由于本設計采用的是5 V 的MOS 管,通過增大漏端到柵端的距離提高耐壓值,從而保證芯片正常工作時,防護電路關閉。

2 器件設計

Type-C 接口保護芯片采用0.25 μm 的BCD 工藝,其中主體電路采用了自對準硅化物(Silicide)和低摻雜漏(Lightly-Doped Drain,LDD)工藝技術。這些先進工藝改善了器件性能,但同時給ESD 防護電路帶來了新的問題,因此需要對工藝進行改進,消除這些不利因素。

2.1 靜電泄放器件優化

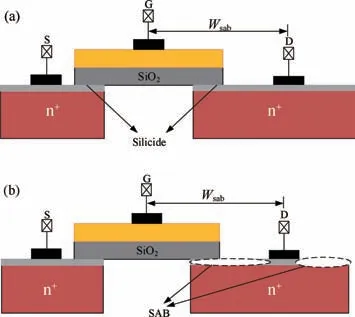

圖4(a)表示Silicide 結構,通常使用Ti、W、Co等耐高溫材料的金屬硅化物覆蓋MOS 器件的源極和漏極,形成低阻的硅化物薄膜,以降低其方塊電阻和接觸電阻,改善器件性能。但是當ESD 發生時,由于硅化物薄膜電阻小,使電流首先沿著有源區表面流動,導致器件發生熱擊穿而損壞,大幅度降低了ESD 防護性能[9]。為了解決Silicide 結構引起的ESD 防護性能降低的問題,本文在Silicide 結構的漏端采用金屬硅化物阻擋(Silicide Blocking,SAB)技術,如圖4(b)所示,在Silicide 結構的基礎上增加一張掩膜版來阻擋金屬硅化物,在漏端形成有效的鎮流電阻,使ESD 電流分布更均勻。圖4 中Wsab表示漏端到柵端的距離,本設計通過調整Wsab的大小保證器件的耐壓值。

圖4 器件結構優化。(a)Silicide 結構;(b) SAB 結構Fig.4 Optimization of device structure.(a) Structure of Silicide;(b) Structure of SAB

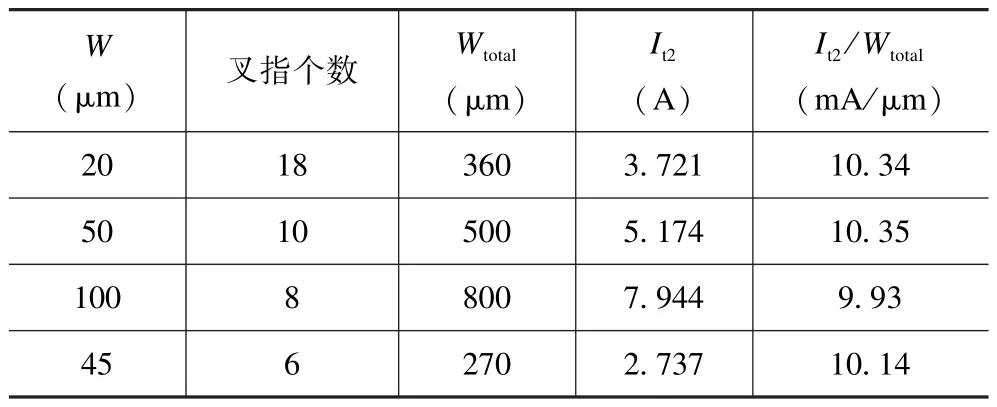

圖5(a)表示LDD 結構,該結構能夠緩解源漏兩側溝道處的強電場,抑制熱載流子效應。但是由于LDD 結構結深只有約0.02 μm,這相當于在源極和漏極兩端形成兩個尖端,在靜電放電過程中,較高的熱量集中在這兩個尖端,使其極易在高溫下熔融,造成器件漏端與體、源端的短路,易在靜電放電中發生燒毀。為了克服因LDD 結構造成ESD 防護能力下降的問題,本設計對器件工藝進行優化,如圖5(b)所示,在源漏區注入之前,通過大角度離子注入(Electro-Static Discharge Implant,ESD_IMP)技術消除LDD 結構,降低觸發電壓,消除尖端放電現象,提高ESD 防護能力。工藝優化后的器件如圖5(c)所示,并且對優化后柵長L為1.2 μm 的器件過流能力進行測試,結果如表1 所示,其中W表示柵寬,Wtotal表示總體柵寬,It2表示過流能力。從表1 可以發現器件過流能力由優化前的4 mA/μm 提高到10 mA/μm,提升了1.5 倍。

表1 工藝優化后器件的過流能力Tab.1 Overcurrent capability of the device after process optimization

圖5 器件工藝優化。(a)LDD 結構;(b)工藝優化流程;(c)加入ESD_IMP 的NMOS 結構圖Fig.5 Optimization of device process.(a) Structure of LDD;(b) Steps of process optimization;(c) NMOS structure diagram with ESD_IMP added

2.2 導流二極管優化

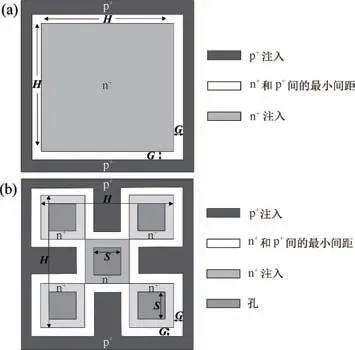

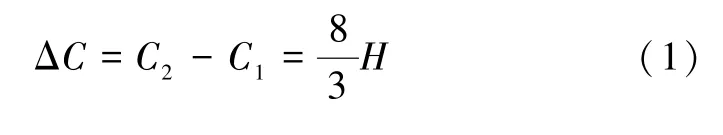

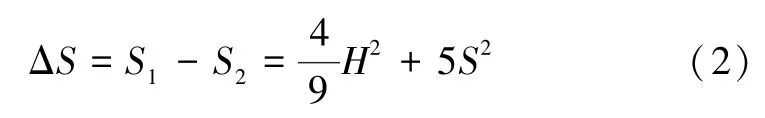

對于導流二極管而言,需要考慮其正向導通時的過流能力、反向擊穿電壓和電容。在本設計中,所有導流二極管的過流能力都必須大于25 A。對于低壓端口防護電路中的D1-D4和高壓端口防護電路中的D2、D3二極管,均采用低擊穿電壓和低電容的二極管,選擇p+/Nwell 二極管用于高端導流二極管,n+/Pwell 二極管用于低端導流二極管,對于高壓端口防護電路而言,二極管D1和D4的反向擊穿電壓必須高于44 V。為了減少結電容,對二極管的版圖進行優化,文獻[12]中已證明,隨著二極管PN 結周長的增加,二極管的失效電流基本成比例增加,而且隨著二極管PN結面積的減小,二極管的寄生電容減小,因此本文通過提高二極管PN 結的周長面積比來減少寄生電容[13]。優化前后n+/Pwell 二極管的版圖如圖6 所示,在n+注入區掏孔以減少PN 結電容,圖中,H表示n+注入區的邊長,G表示n+注入區和p+注入區的最小間距,S表示孔的邊長。則優化后二極管PN 結周長表示為:C2=H ×4×5,與優化前二極管PN 結周長C1=4H相比,增加了:

圖6 導流二極管版圖。(a)優化前二極管版圖;(b)優化后二極管版圖Fig.6 Layout of diversion diode.(a) Diode layout before optimization;(b) Diode layout after optimization

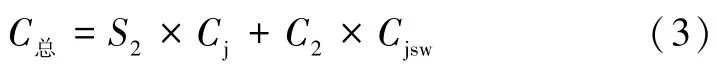

優化后二極管PN 結面積表示為S2=5×與優化前二極管PN 結面積S1=H2相比,減少了:

則優化后二極管的寄生電容表示為:

式中:Cj為二極管單位面積寄生電容;Cjsw為二極管側壁單位長度寄生電容。由式(1)~(3)可知,在保證二極管失效電流的情況下,適當減小PN 結面積,能夠減小二極管的寄生電容,達到低電容的設計要求。

3 測試結果與討論

采用TLP(Transmission-Line-Pulsing)和靜電槍兩種方法對防護電路進行測試,TLP 測試是將方波測試脈沖加到待測器件的兩腳之間進行測試,能夠得到較為準確的I-V曲線,而且波形噪聲分量低,測試結果較穩定[14];靜電槍測試是直接對芯片引腳進行接觸放電或氣隙放電,受環境因素影響較大,一般用于得到被測器件的損傷閾值電壓[15]。

3.1 TLP 測試

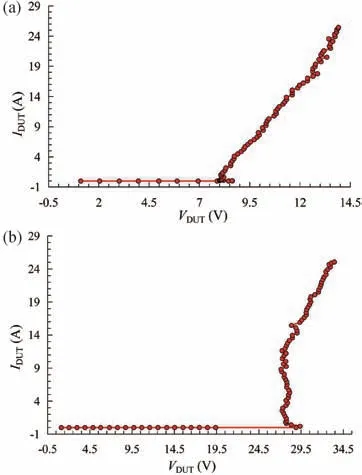

利用TLP 系統對芯片的低壓端口和高壓端口進行測試,得到的I-V曲線如圖7 所示。對低壓端口D+、D-而言,正常工作電壓不超過5.5 V,從圖7(a)的測試結果可以看出,低壓端口防護電路的觸發電壓為8.6 V,維持電壓為8 V,大于D+、D-端口的最大工作電壓;對高壓端口CC1、CC2、SBU1 和SBU2 而言,最大電壓為24 V,從圖7(b)的測試結果可以看出,高壓端口防護電路的觸發電壓為29.5 V,維持電壓為27.5 V,大于端口的最大電壓。而且兩者的二次失效電流均大于25 A,表明ESD 性能能夠達到IEC61000-4-2 接觸放電±8 kV,氣隙放電±15 kV,即低壓端口和高壓端口電路均滿足系統級靜電防護要求。

圖7 端口TLP 測試結果。(a)低壓端口;(b)高壓端口Fig.7 TLP test results of the ports.(a) The low-voltage port;(b) The high-voltage port

3.2 靜電槍測試

采用靜電槍對芯片C_CCX 和C_SBUX 引腳進行接觸放電±8 kV,觀察CCX 和SBUX 引腳的波形,C_CCX引腳接觸放電±8 kV 的結果如圖8 所示。從圖8(b)和(d)可以發現,由于靜電槍注入波形不穩定,而且受到環境因素及測試線、鍵合絲上寄生電阻的影響,使得CC1 端口接觸放電±8 kV 的鉗位電壓分別為372 V 和-362 V。由文獻[16]可知,靜電槍測試方法受測試環境影響因素較大,導致測試結果存在一定的誤差,靜電槍測試完成后,再對該芯片其他性能進行測試,結果表明各參數指標正常,由此說明防護電路能夠達到接觸放電±8 kV 的耐壓能力。

圖8 CC1 IEC 61000-4-2 ±8 kV 響應波形。(a) C_CC1 +8 kV;(b) CC1 +8 kV;(c) C_CC1 -8 kV;(d) CC1 -8 kVFig.8 Response waveform of the CC1 IEC 61000-4-2 ±8 kV.(a) C_ CC1 +8 kV;(b) CC1 +8 kV;(c) C_ CC1 -8 kV;(d) CC1 -8 kV

4 結論

本文提出了基于導流二極管與ZCNMOS 結構構建的靜電放電保護架構,通過ZCNMOS 結構改善了GGNMOS 結構中電流分布不均勻的現象。針對靜電泄放器件,采用SAB 技術和ESD_IMP 技術,提高了ESD 防護性能;對二極管版圖進行優化,減少了寄生電容。測試結果表明,ESD 防護電路能夠滿足系統級IEC61000-4-2 接觸放電±8 kV,氣隙放電±15 kV 的靜電防護要求,CCX 端口、SBUX 端口和D+、D-端口電容分別為74,6 和1.7 pF,滿足低電容要求,電路結構簡單、利于集成,具有良好的應用前景。