一種低功耗無運放結構的基準電壓源設計

黃祥林,李富華,宋愛武

(蘇州大學電子信息學院,江蘇蘇州215000)

1 引言

基準電壓源一直都是模擬集成電路中不可或缺的電路單元之一,一個理想的基準電壓源應該具有良好的溫度系數、高電源抑制比、低功耗以及低輸出噪聲,具體指標的取舍由具體應用環境而定,例如,線性穩壓器(Low Dropout Regulator,LDO)芯片需要基準電壓有較高的電源抑制比,基準電壓的電源抑制比將直接影響LDO輸出電壓的電源抑制比;在模數轉換芯片中,一般要求帶隙基準輸出的噪聲盡可能低;在某些低功耗的集成電路中,可能還會要求基準電壓具有低壓啟動的功能。

在便攜式電子產品普及的今天,人們對設備的續航能力提出了越來越高的要求,基準電壓源是每個集成芯片中幾乎必不可少的電路單元之一,因此,基準電壓電路低功耗的實現成為了一直以來研究的熱點。近些年,一些學者也對低功耗的帶隙基準進行了大量的研究。文獻[1]使用工作在亞閾值區的MOS管代替三極管,結構簡單,但電路整體功耗很高,電源抑制比很低,不能滿足設計要求,文獻[2]使用工作在線性電阻區的MOS管代替電阻產生正溫度系數(Proportional to Absolute Temperature,PTAT)電流,實現了全MOS結構的帶隙基準,但是該結構電源抑制比較低,而且用MOS管代替電阻,阻值不容易控制,溫度系數也不理想;文獻[3]也是全MOS結構的帶隙基準,其中的電路結構復雜,而且需要嚴格設計MOS管的寬長比來調出一個與溫度無關的電壓;文獻[4]提出的基準電壓結構簡單,溫度系數良好,但是需要比較高的電壓才能建立起穩定的輸出,電源效率低,電源抑制比也有待提高。為了對低功耗的基準電壓源性能做更進一步的優化,本文在現有的研究基礎上,設計出了一種結構簡單、功耗低、電源抑制比高、電源利用率高的基準電壓電路。

2 帶隙基準原理分析

帶隙基準源的基本思想是通過兩個分別呈正、負溫度系數的電壓之和來得到一個與溫度無關的基準電壓:

其中V1與V2有著相反的溫度系數,通過調節α1與α2的值,當式(1)滿足時,Vref視為幾乎不受溫度的影響。

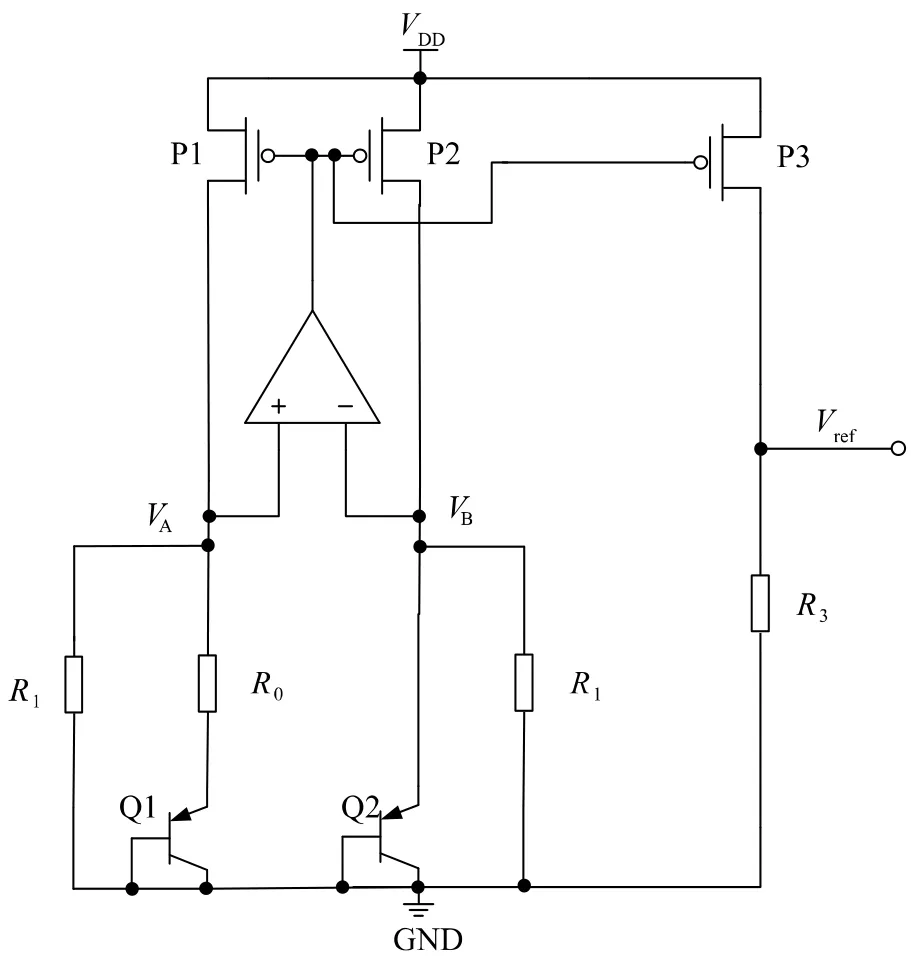

傳統的電流模型帶隙基準源的結構如圖1所示,此電路最大的優點是輸出的基準電壓值可調以及可以輸出一個幾乎與溫度無關的基準電流。其中運用到了一個工作在深度負反饋的運放,使得VA=VB,從而可以產生一路與溫度呈正相關的電流,增加了兩路電阻R1,可以產生一路與溫度呈負相關的電流,這兩路電流之和為一個與溫度無關的基準電流,通過調節R0、R1和R3的阻值,可以輸出一個與溫度無關的基準電壓。P1與P2的寬長比一致,三極管Q1與Q2發射極面積之比為N∶1,流過P3管的電流表達式為:

圖1 傳統電流模結構的帶隙基準電路

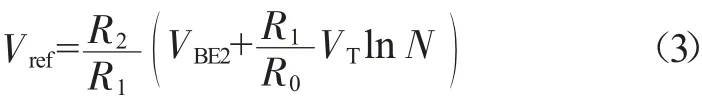

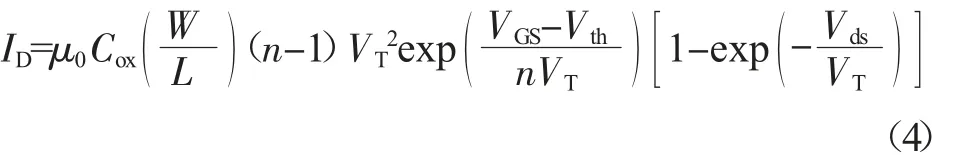

其中VBE2為三極管Q2的基極與發射極之間的電壓,VT為熱電壓,室溫下約等于26 mV。因此,基準電壓的輸出表達式為:

從式(3)可知,調節電阻R1與R0的比值,可以用于補償VBE的負溫度特性,調節電阻R1與R2的比值,可以輸出一個任意大小的基準電壓。然而,如果需要實現低功耗,傳統帶隙結構存在眾多缺陷:①運放的加入會消耗許多電流;②運放失調電壓會使得理論計算產生一定偏差,從而電阻R的值不能很好地確定;③低功耗需要比較小的正溫度系數電流,因此電阻R0、R1的阻值必然會很大;④基準電壓直接在P3管的漏端輸出,電源抑制比不理想。所以,需要提出新的電路結構,來解決實現低功耗過程中存在的諸多問題。

3 本文提出的基準電壓源

傳統的帶隙結構使用三極管來產生正溫度系數的電流和一路負溫度系數的電流,由于三極管在流過納安級別電流的情況下,VBE也可以達到500 mV以上,為了使R1上的電流也為納安級別,R1的阻值將需要幾兆歐姆,這樣的大電阻會占用很大的版圖面積。為此,本文提出了一種無三極管結構、無需運放的低功耗基準電壓,電路原理如圖2所示。

圖2 本文提出的基準電壓電路

3.1 啟動電路

本文所使用的電流基準電路存在簡并點,簡并點會使得PM3管的柵極一直處于高電平,NM6的柵極一直處于低電平,如果電路穩定在這種狀態,那么電路基準電路將不能輸出一個設計者所需要的偏置電流,為了消除這種隱患,需要加入啟動電路,使電路脫離簡并點。設置NM1、PM1的尺寸,使得工作在亞閾值區的NM1產生的電流小于也工作在亞閾值區PM1的電流,因此,在啟動階段時,PM0的柵極為低電平,PM0被導通,NM3有電流流過,NM4的漏極被拉至低電平,電流基準電路脫離簡并點正常工作;當基準電壓電路啟動完畢時,由于PM2沒有電流通路,PM0柵極最終會被拉至高電平,PM0截止,NM3、NM4也截止,啟動電路不消耗額外的靜態電流。

3.2 基準電流產生電路

基準電流產生電路產生的電流給基準電壓產生電路提供電流偏置,該結構增加了PM3所在的支路,不僅能在電阻R0阻值盡可能小的情況下產生納安級的偏置電流,還具有增加環路穩定性的作用。電路中的NM6、NM7都工作在亞閾值區,工作在亞閾值區的MOS管電流表達式為:

其中μ0為載流子遷移率,Cox為單位面積柵氧電容,n=1+CD/Cox,CD為襯底與溝道之間的耗盡層電容,n的取值一般為1~2,W/L為MOS管的寬長比。當Vds>4VT時,由于e-4≈0.018315,式(4)可以簡化為:

由式(5)可知,工作在亞閾值區的MOS管的柵極與源極之間的電壓VGS可表示為:

加在電阻R上的電壓為VGS_NM7-VGS_NM6,VGS_NM7為NM7的柵極與源極之間的電壓,VGS_NM6為NM6的柵極與源極之間的電壓,電路中流過PM3、PM5、PM7的電流之比為K∶1∶1,NM7、NM6的寬長比為1∶N,故可以求出流過NM7的最小基準電流I為:

3.3 基準電壓產生電路

該基準電壓產生電路的核心是使用工作在亞閾值區的增強型和耗盡型的NMOS管,運用兩個NMOS管的VGS之差來產生一個與溫度近似無關的基準電壓。NM11管為增強型的NMOS管,NM12管為耗盡型的NMOS管,它們的唯一區別是:增強型的NMOS管閾值電壓Vth為正值,耗盡型的NMOS管的閾值電壓Vth為負值。兩個不同類型的NMOS管的VGS之差可以表示為:

式(8)中,第一項為負溫度特性的電壓,第二項為正溫度特性的電壓,可以調節流過NM11和NM12管的電流以及它們的寬長比來修正Vth11和|Vth12|在溫度系數上的偏差,使兩個NMOS管的VGS之差為一個與溫度幾乎無關的基準電壓Vref。

為了提高基準電壓電路對電源電壓的抗干擾能力,在耗盡管NM13的上方加入了一個同為耗盡型、隔離型的NMOS管NM14,使得NM13的漏極不直接接在電源電壓上,起到隔離作用,同時NM13、NM14構成共源共柵結構,使得電源上的擾動在基準的輸出端得到衰減。由式(8)可知,建立一個穩定的基準電壓與ID6和ID8的大小并無關系,只要電路中電流鏡正常工作即可,又由于NM13為耗盡管,其柵極電壓始終小于源極電壓,在電源電壓上電過程中,NM13的柵極只需上升至Vref-|VGS_PM13|,就可以輸出一個Vref了,所以,本文提出的基準電壓電路的壓差非常小,大大提高了電源利用率。

4 仿真結果與分析

采用0.18 μm CMOS工藝,使用5 V電源電壓供電,在TT工藝下,對此基準電壓電路進行溫度系數仿真,仿真的溫度范圍為-40~125℃,仿真結果如圖3所示,可以看到在全溫度范圍內,輸出電壓僅變化了1.6 mV,溫度系數為9.56×10-6/℃,該結果表明,在穩定輸出1.03 V電壓的同時,此基準電壓電路還具有良好的溫度系數。

圖3 溫度系數仿真結果

為了驗證此基準電壓電路的抗電源紋波干擾能力,對其電源抑制比進行仿真。圖4為電源抑制比的仿真結果,可以看到電源紋波頻率在100 Hz時,電源抑制比可達-72.11 dB,電源紋波頻率為1 kHz時,電源抑制比仍可保持在-67.70 dB,相對于傳統的帶隙基準結構,本文提出的基準電壓電路電源抑制比有所提高。

圖4 電源抑制比仿真結果

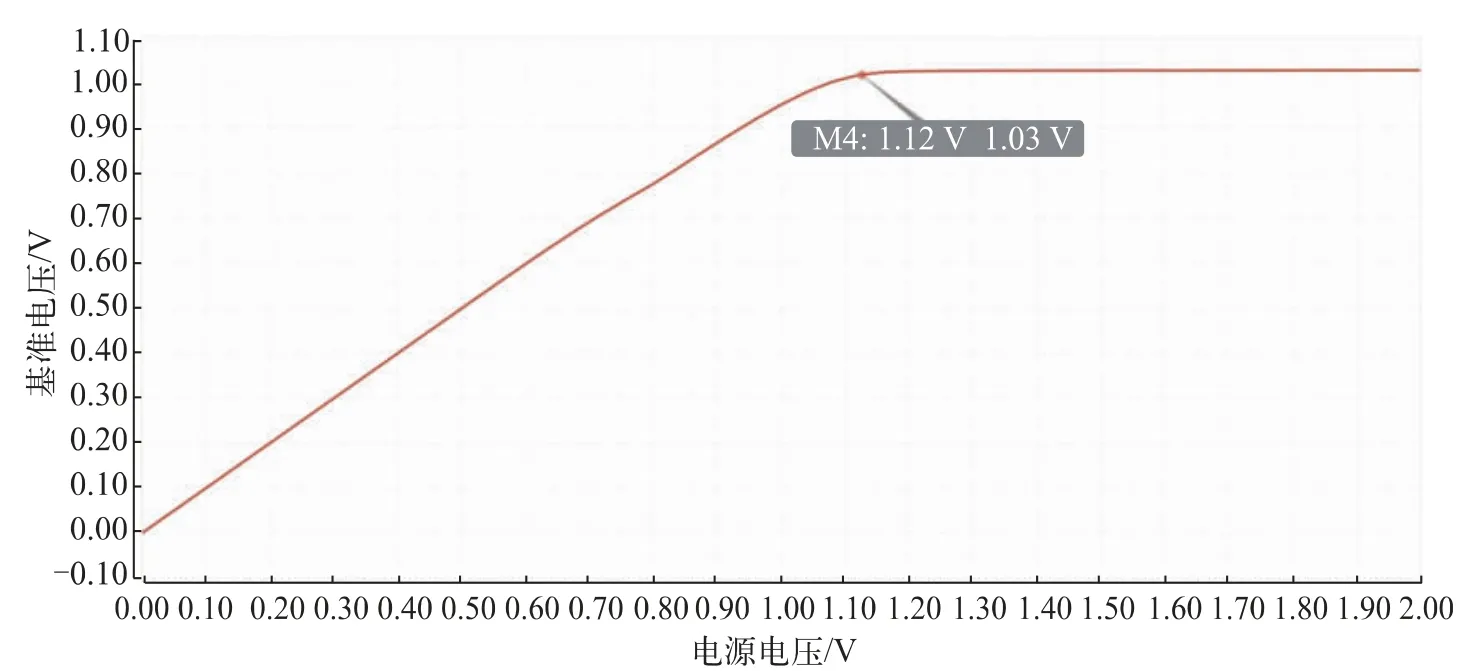

通過DC掃描電源電壓VDD從0.00至5.00 V的變化,得到的仿真結果如圖5所示(2 V后基準電壓保持不變,圖中省略),當VDD上升至1.12 V時,即可輸出一個1.03 V的基準電壓,壓差為92 mV,故該基準電壓電路的電源利用效率很高。

圖5 壓差仿真結果

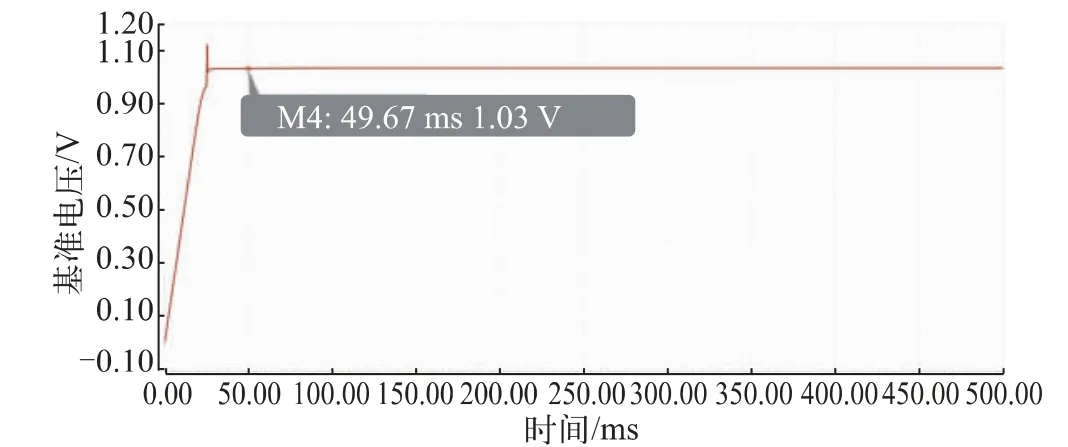

對電源電壓從0上升至5 V(1 μs電源快上電與100 ms慢上電兩種情況下)進行Tran仿真,觀察最后基準電壓源是否能夠穩定建立起來,仿真結果如圖6、7所示,結果表明,在兩種情況下,基準電壓都能夠穩定輸出大約1.03 V的電壓。

圖6 1 μs電源快上電過程Tran仿真結果

圖7 100 ms慢上電過程Tran仿真結果

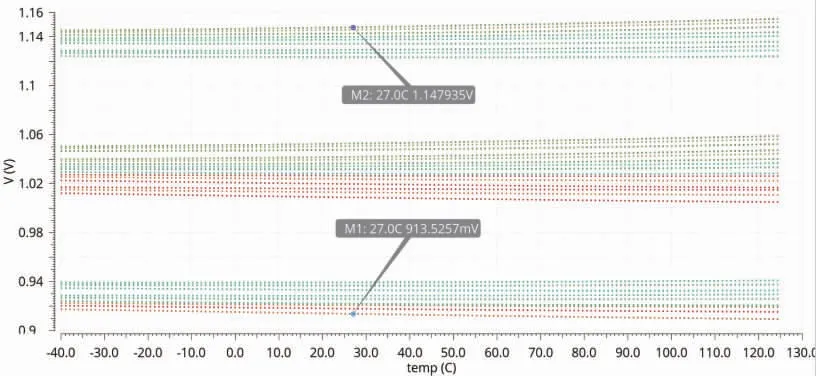

最后,在TT、FF、SS、SF、FS幾種工藝的組合下,對此基準電壓的溫度系數、整體的電流消耗進行了仿真,仿真結果如圖8、9所示。結果顯示,該基準電壓電路可以穩定工作,在考慮極端條件下,基準電壓最高為1.1479 V,最低為0.9135 V,可以作為修調的參考范圍,基準電壓變化最小913.9 μV,最大為11.65 mV,電源抑制比在最壞時,整體的電流消耗在常溫的TT工藝下只有164.8 nA,最壞時,電流消耗也僅有214.9 nA。

圖8 不同工藝下的溫度系數仿真結果

表1 給出了本文與參考文獻中各電路性能的對比,可以明顯看出,本文解決了文獻[1]中電路功耗大的問題,電源抑制比也高得多;相對于文獻[2],電路在實現低功耗的同時,溫度系數和電源抑制比也得到了很好的改善;同時,本文提出電路的結構也比文獻[3-4]有更好的溫度系數和更高的電源抑制比。

表1 參考文獻與本文提出的電路性能對比

5 結論

本文使用了兩種不同類型且工作在亞閾值區的NMOS管,通過調節流過它們的電流以及寬長比,得到了一個溫度系數良好的基準電壓源,該基準電壓電路不僅結構簡單,且具有很高的電源抑制比,仿真結果顯示,該電路可以穩定地輸出一個1.03 V的基準電壓,整體只消耗了164.8 nA的電流,在5 V電源供電下,功耗僅為0.824 μW,低頻電源抑制比可達-72.11 dB,滿足了業界對基準電路低功耗高電源抑制比的設計要求。

圖9 不同工藝下的整體電流消耗仿真結果