應用于有源巴倫的新型幅度相位間接糾正技術

李世元

(天津大學 天津市成像與感知微電子技術重點實驗室,天津 300072)

在無線通信應用領域中,相較于單端系統,差分系統具有消除串擾、抑制噪聲與偶次諧波失真的優點。其中,巴倫結構作為將單端信號轉為差分信號的重要射頻組件,應用極為廣泛。

為了解決上述問題,在毫米波頻段下實現對幅度與相位誤差的同時糾正,提出了一種應用于有源巴倫的新型幅度相位間接糾正技術。該技術將輸入信號間的幅度與相位誤差轉換為內部固有誤差,并通過減小內部誤差實現間接糾正。

1 傳統相位糾正技術基本原理

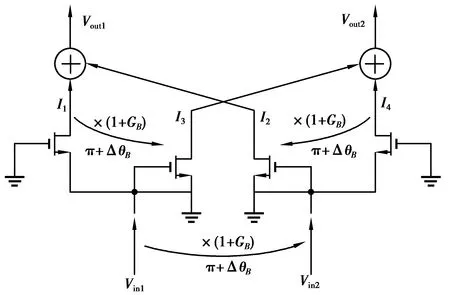

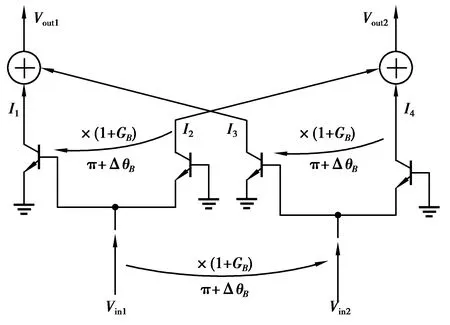

由于共源結構對信號反相放大而共柵結構對信號同相放大的工作特性,共源共柵結構可作為巴倫實現信號的單端轉差分。圖1為傳統相位糾正技術原理圖,包含了2個相同的共源共柵結構。為方便起見,將輸入端口間相位誤差表示為ΔθA,幅度誤差表示為GA。由于寄生效應的影響,內部糾正電路中的共源共柵結構也會引入新的幅度與相位誤差,因此將該部分相位誤差表示為ΔθB,幅度誤差表示為GB。

圖1 傳統相位糾正技術原理圖Fig. 1 Conventional phase-correction technique

糾正電路將輸入信號分配成4條支路電流,各支路電流表示為

(1)

4條支路的電流信號在輸出端重新組合,產生一對新的差分信號,表示為

(2)

(3)

比較式(2)和式(3)中各項可知,輸出信號間相位完全相同,而幅度存在一定差異,如式中下劃線標注,該差異主要是由實數值2、GA與GB組成的幅度項“2+GA+GB+GAGB”與“2+GA+GB”之間的差異引起的。當GA、GB與實數值2相比較小時,GA、GB在幅度項中占比重較小,“2+GA+GB+GAGB”與“2+GA+GB”近似相等,因此輸出信號的幅度誤差較小,Vout1與Vout2為一對差分信號。在這種情況下,傳統相位糾正技術可以對相位誤差進行有效抑制。

然而,當GA、GB與實數值2可比擬時,輸出信號Vout1與Vout2之間存在不可忽略的幅度誤差,這意味著傳統相位糾正技術不能對較大的幅度誤差進行限制和糾正。隨著頻率的提高,由于寄生效應的影響,糾正電路所引入的相位誤差ΔθB與幅度誤差GB隨之變大,造成輸出端口間的幅度誤差進一步變大。因此,傳統相位糾正技術不能夠同時糾正幅度與相位誤差,且隨著工作頻率提高,糾正能力有所下降。

2 新型幅度相位間接糾正技術

2.1 新型幅度相位間接糾正技術的工作原理

文章在傳統相位糾正技術的基礎上進行改進,提出了新型幅度相位間接糾正技術。該技術巧妙地改變了輸入信號在糾正電路中的分配與重組路徑,同時將原幅度相位誤差轉換為新的內部誤差,并通過減小內部誤差繼而實現間接糾正。

圖2 新型幅度相位間接糾正技術原理圖Fig. 2 Proposed magnitude and phase indirect regularization technique

需要特別注意,ΔθA僅表示輸入信號間的相對相位誤差,而不是絕對相位差。將輸入信號間的絕對相位差表示為θA,那么對于差分系統來說,ΔθA與θA滿足

θA=π+ΔθA。

(4)

糾正電路將輸入信號分為4條支路電流,各支路電流表示為

(5)

4條支路的電流信號在輸出端重新組合,產生一對新的差分信號,表示為

(6)

(7)

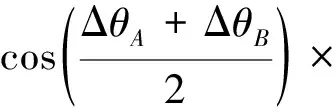

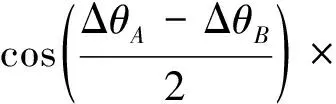

通過對比式(6)和式(7)中各項的系數和初相位,可以觀察到在新產生的輸出信號,即Vout1與Vout2之間,存在4處不同,如式(6)中下劃線所示。這意味著對于新型幅度相位間接糾正技術,其輸出端口間仍存在幅度與相位誤差。

由于不同的輸入差分信號之間存在著不同的幅度與相位誤差,可將輸入誤差GA和ΔθA視為未知的變量誤差。在設計過程中,一旦內部糾正電路的結構與參數確定,其所引入的額外誤差隨之確定,可將內部誤差視為已知的固有誤差。由于該技術最終得到的輸出誤差僅取決于GB和ΔθB,與GA和ΔθA無關,因此,該技術可將輸入信號間的未知變量誤差轉換為內部糾正電路中的已知固有誤差。

2.2 內部糾正電路的設計與優化

通過以上分析可知,內部糾正電路所引入的額外誤差越小,新型幅度相位間接糾正技術的糾正能力越強。為了減小輸出端口間的幅度與相位失配,只需要減小固有誤差GB和ΔθB。

因此,針對內部糾正電路進行優化設計,提高該技術在高頻下的糾正能力。

傳統內部糾正電路與優化后的內部糾正電路結構如圖3所示。

圖3 傳統內部糾正電路與優化后結構對比 Fig. 3 Comparison of traditional internal correction circuit with the optimized structure

在傳統內部糾正電路中,共射共基結構的不同路徑上寄生參數不同。高頻下的寄生效應導致輸出端口間存在較大的幅度與相位誤差,即內部糾正電路所引入的固有誤差變大,繼而降低了幅度與相位糾正電路性能。

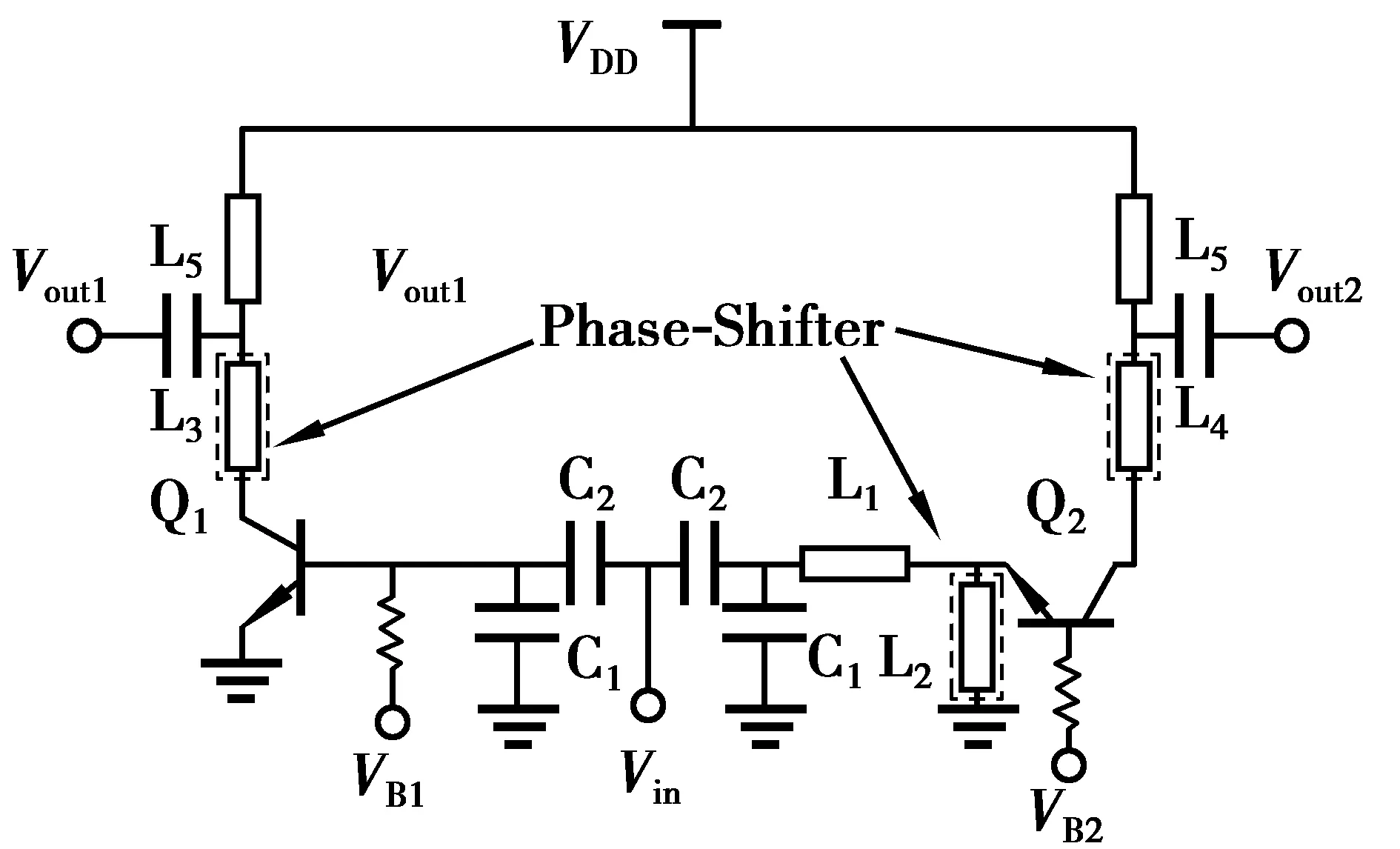

為解決傳統內部糾正電路所引入的固有誤差較大的問題,對其進行優化設計。在傳統內部糾正電路的輸入與輸出端分別添加額外的移相網絡,從而補償共射共基結構的相位誤差;通過適當調節共射管與共基管的參數大小,以減小傳統內部糾正電路所引入的幅度誤差。具體優化方案如圖4所示。

圖4 所提出的內部糾正電路原理圖Fig. 4 Proposed internal correction circuit

整個內部糾正電路包含3部分,分別為輸入匹配網絡,輸出匹配網絡與移相網絡。其中,輸入匹配網絡包括MIM電容C1和C2,輸出匹配網絡包括傳輸線L5與輸出端節點電容。傳輸線L2構成共基結構的直流回路,同時通過優化L2來改善輸入回波損耗。移相網絡由2部分組成,分別為輸入端移相網絡L2和輸出端移相網絡L3、L4。通過適當調整共射管Q1與共基管Q2的發射極長度和并聯個數來減小糾正電路的幅度誤差,并通過調節輸入和輸出移相網絡L2~L4的長度,減小相位誤差,繼而在輸出端得到一對幅度接近一致,相位相差180°的差分信號。因此,適當改變晶體管參數和添加無源移相網絡,可以有效地減小內部糾正電路所引入的額外幅度和相位誤差,提高該技術在高頻下的糾正性能。

與傳統相位糾正技術相比,該間接糾正技術能夠同時將幅度誤差與相位誤差限制在一定閾值范圍內,從而達到幅度與相位同時糾正的目的。由于該技術獨立于輸入信號,輸入信號的不平衡程度越大,該技術的糾正能力越強。

3 利用電路仿真驗證間接糾正理論

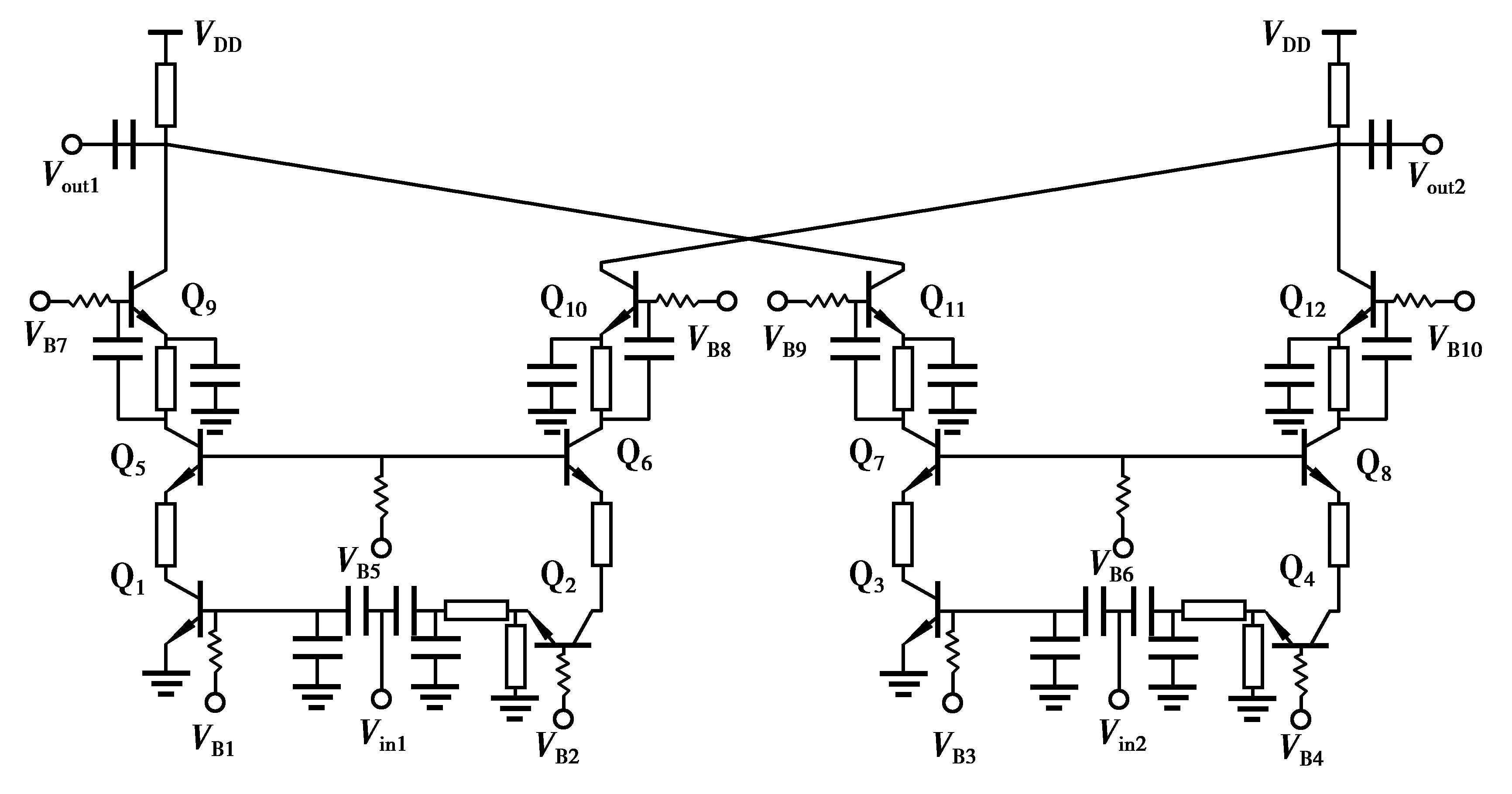

在ADS仿真平臺中,基于0.13μm SiGe BiCMOS工藝搭建新型幅度相位間接糾正電路,如圖5所示。

圖5 新型幅度相位間接糾正電路原理圖Fig. 5 Schematic of the magnitude and phase indirect correction circuit

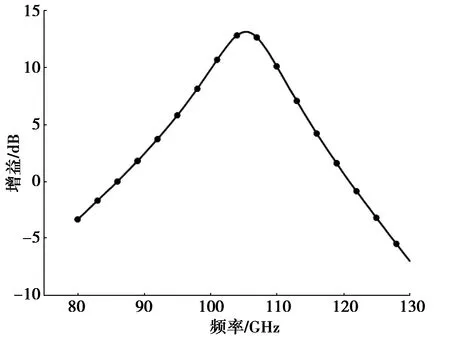

糾正電路的增益性能如圖6所示,在中心頻率105 GHz下,最大增益為12.7 dB,電路的3 dB帶寬為96~113 GHz。

圖6 糾正電路的增益仿真結果 Fig. 6 The simulated gain of the correction circuit

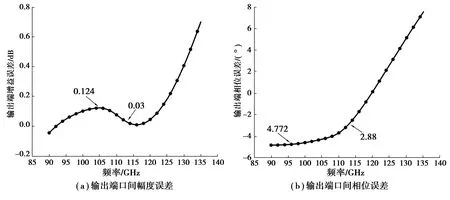

糾正電路輸出端口間的幅度與相位誤差隨頻率變化曲線如圖7所示。在96~113 GHz的帶寬范圍內,輸出端口的最小幅度誤差為0.03 dB,最大幅度誤差為0.124 dB;最小相位誤差為2.88°,最大相位誤差為4.772°。在毫米波頻段下,糾正電路的輸出端口間誤差較小,平衡性良好。

圖7 在不同頻率下,輸出端口間的幅度與相位誤差Fig. 7 Output phase-error and gain-error versus frequency

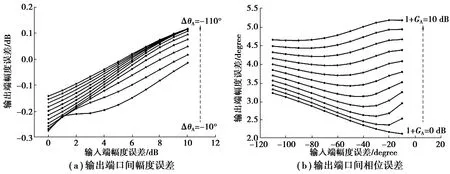

為了驗證新型幅度相位間接糾正技術在不同輸入誤差下的適用性與魯棒性,改變輸入信號間的幅度與相位誤差,重復進行仿真。假定輸入信號間的幅度誤差在0~10 dB、相位誤差在10°~100°范圍內取值,糾正后的輸出端口間幅度與相位誤差如圖8所示。

圖8 在不同輸入誤差下,輸出端口間誤差結果Fig. 8 Output phase-error and gain-error versus input phase-error and gain-error

經電路仿真驗證可得,當輸入信號間幅度誤差在0~10 dB、相位誤差在10°~100°范圍內任意取值時,輸出端口間幅度與相位誤差發生改變。當輸入幅度誤差為5 dB,相位誤差為110°時,輸出端口間幅度誤差取得最小值0 dB,此時輸出相位誤差為4°;當輸入幅度誤差為0 dB,相位誤差為10°時,輸出端口間相位誤差取得最小值2.1°,此時輸出幅度誤差為0.27 dB。在整個帶寬范圍內,輸出端口的幅度誤差均小于0.3 dB,相位誤差均小于5.3°,電路最大增益為12.7 dB,功耗為54 mW。

在毫米波頻段下,對于不同的輸入幅度與相位誤差,新型幅度相位間接糾正技術均展現出良好的幅度相位糾正性能,具有較強的適用性與魯棒性。

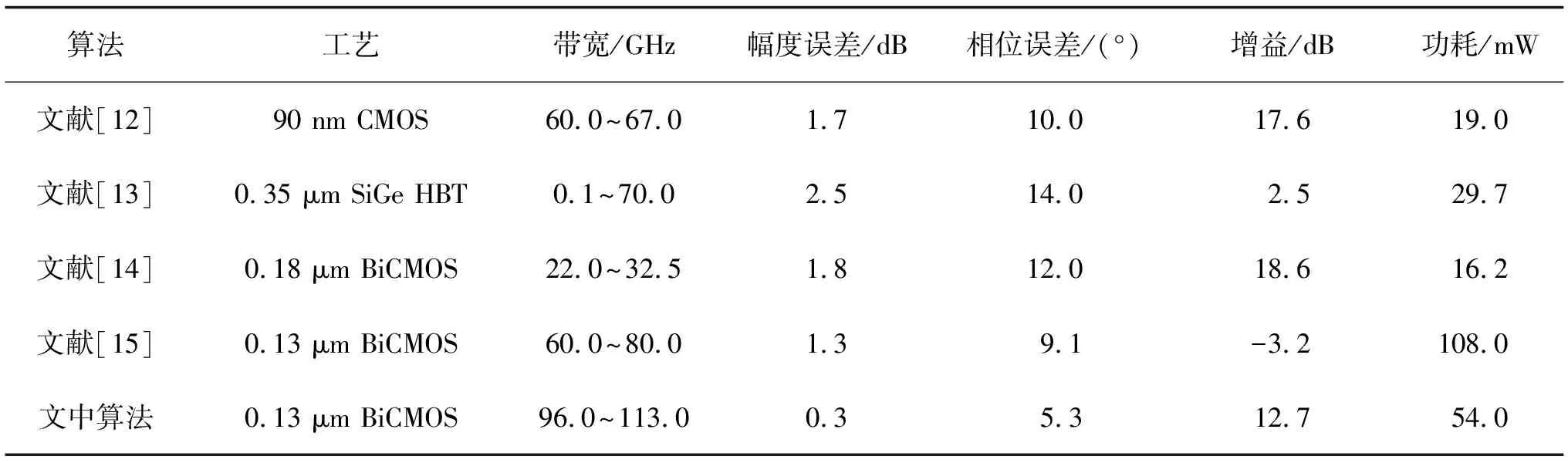

將文中算法應用于有源巴倫的糾正電路,其性能參數與其他文獻進行比較,結果如表1所示。

表1 文中電路與其他參考文獻的參數對比

4 結 論