星地高速數(shù)傳系統(tǒng)低復(fù)雜度可重構(gòu)LDPC編碼器設(shè)計(jì)

康 婧 安軍社 王冰冰②

①(中國(guó)科學(xué)院國(guó)家空間科學(xué)中心 北京 100190)

②(中國(guó)科學(xué)院大學(xué) 北京 100049)

1 引言

空間探測(cè)任務(wù)中,近地軌道(Low Earth Orbit,LEO)衛(wèi)星因具有發(fā)射成本低、通信時(shí)延小和覆蓋范圍廣等優(yōu)勢(shì)而被廣泛應(yīng)用。隨著空間探測(cè)任務(wù)需求愈加復(fù)雜、衛(wèi)星有效載荷傳感器精度不斷提高,星地鏈路傳輸數(shù)據(jù)量大大增加[1],如何在星上硬件資源、帶寬和功率受限的情況下實(shí)現(xiàn)高速數(shù)據(jù)傳輸已成為我國(guó)目前航天器發(fā)展需要解決的核心難題。良好的信道糾錯(cuò)編碼對(duì)于提高數(shù)傳的抗干擾性、傳輸可靠性和傳輸功率受限情況下的數(shù)據(jù)傳輸容量十分重要,與高階數(shù)字調(diào)制技術(shù)相結(jié)合還可以解決帶寬受限問(wèn)題[2],因此探索一種合適的信道編碼方案對(duì)當(dāng)前空間通信的發(fā)展具有重要意義。

低密度奇偶校驗(yàn)(Low Density Parity Check,LDPC)碼由Gallager[3]于1962年在其博士論文中提出,是一種糾錯(cuò)性能逼近Shannon極限的信道編碼技術(shù),具有譯碼復(fù)雜度低、誤碼平層低等優(yōu)勢(shì),已廣泛應(yīng)用于多種通信標(biāo)準(zhǔn),如DVB-S2, CCSDS,IEEE 802.11n等。針對(duì)航天通信應(yīng)用,國(guó)際空間數(shù)據(jù)系統(tǒng)咨詢(xún)委員會(huì)(Consultative Committee for Space Data Systems, CCSDS)制定了《131.0-B-2遙測(cè)同步及信道編碼》標(biāo)準(zhǔn)[4],規(guī)定了近地衛(wèi)星通信應(yīng)用和深空通信應(yīng)用的兩套LDPC碼字,其中近地衛(wèi)星通信部分采用了碼率為7/8的準(zhǔn)循環(huán)(8176,7154) LDPC碼。

CCSDS標(biāo)準(zhǔn)規(guī)定的(8176, 7154)LDPC碼是一種準(zhǔn)循環(huán)LDPC(Quasi-Cyclic, QC-LDPC)碼,可利用循環(huán)移位寄存器實(shí)現(xiàn)線性復(fù)雜度的編碼[5,6]。文獻(xiàn)[7]實(shí)現(xiàn)了滿足航天應(yīng)用需求的串行編碼電路,其實(shí)現(xiàn)復(fù)雜度低,但所需編碼時(shí)鐘周期數(shù)和信息比特位數(shù)成正比,碼長(zhǎng)較長(zhǎng)時(shí)編碼數(shù)據(jù)吞吐率不能滿足高速數(shù)傳需求。文獻(xiàn)[8]提出了一種高效低功耗低并行度的編碼方案,文獻(xiàn)[9-12]實(shí)現(xiàn)了并行度更高的編碼器。并行編碼電路可以滿足高編碼數(shù)據(jù)吞吐率要求,但其硬件資源消耗大,功耗高。文獻(xiàn)[13-15]提出了可重構(gòu)設(shè)計(jì)思想,以改善系統(tǒng)性能。本文面向LEO衛(wèi)星星地高速數(shù)傳系統(tǒng),針對(duì)CCSDS近地衛(wèi)星通信標(biāo)準(zhǔn)提出了一種低復(fù)雜度可重構(gòu)LDPC編碼器設(shè)計(jì)方案,并進(jìn)行了硬件實(shí)現(xiàn)驗(yàn)證。

2 LDPC編碼算法

2.1 CCSDS標(biāo)準(zhǔn)LDPC編碼算法

LDPC 碼的編碼算法可以分為兩類(lèi):基于生成矩陣的編碼算法和基于校驗(yàn)矩陣的編碼算法[16]。基于生成矩陣的編碼算法直接將生成矩陣與信息比特進(jìn)行矩陣運(yùn)算,這種編碼算法簡(jiǎn)單且易于實(shí)現(xiàn),但編碼復(fù)雜度高,正比于碼長(zhǎng)的平方。而CCSDS近地衛(wèi)星通信標(biāo)準(zhǔn)采用的是碼率為7/8的(8176,7154)LDPC碼,該碼是一種QC-LDPC碼,可以利用移位寄存器實(shí)現(xiàn)線性復(fù)雜度的編碼,其生成矩陣G是大小為7154× 8176的矩陣

基于生成矩陣的編碼算法為

2.2 并行編碼算法

為縮短編碼周期,提高編碼數(shù)據(jù)吞吐率,在CCSDS標(biāo)準(zhǔn)LDPC編碼算法基礎(chǔ)上,通過(guò)對(duì)輸入信息比特進(jìn)行插0處理和拆分循環(huán)矩陣,可以實(shí)現(xiàn)并行編碼算法。具體步驟如下:

(1)以循環(huán)矩陣Bi,j的階數(shù)511為一段,將輸入信息比特u分割為14個(gè)長(zhǎng)度為511 bit的子向量

3 低復(fù)雜度可重構(gòu)LDPC編碼器

3.1 整體結(jié)構(gòu)

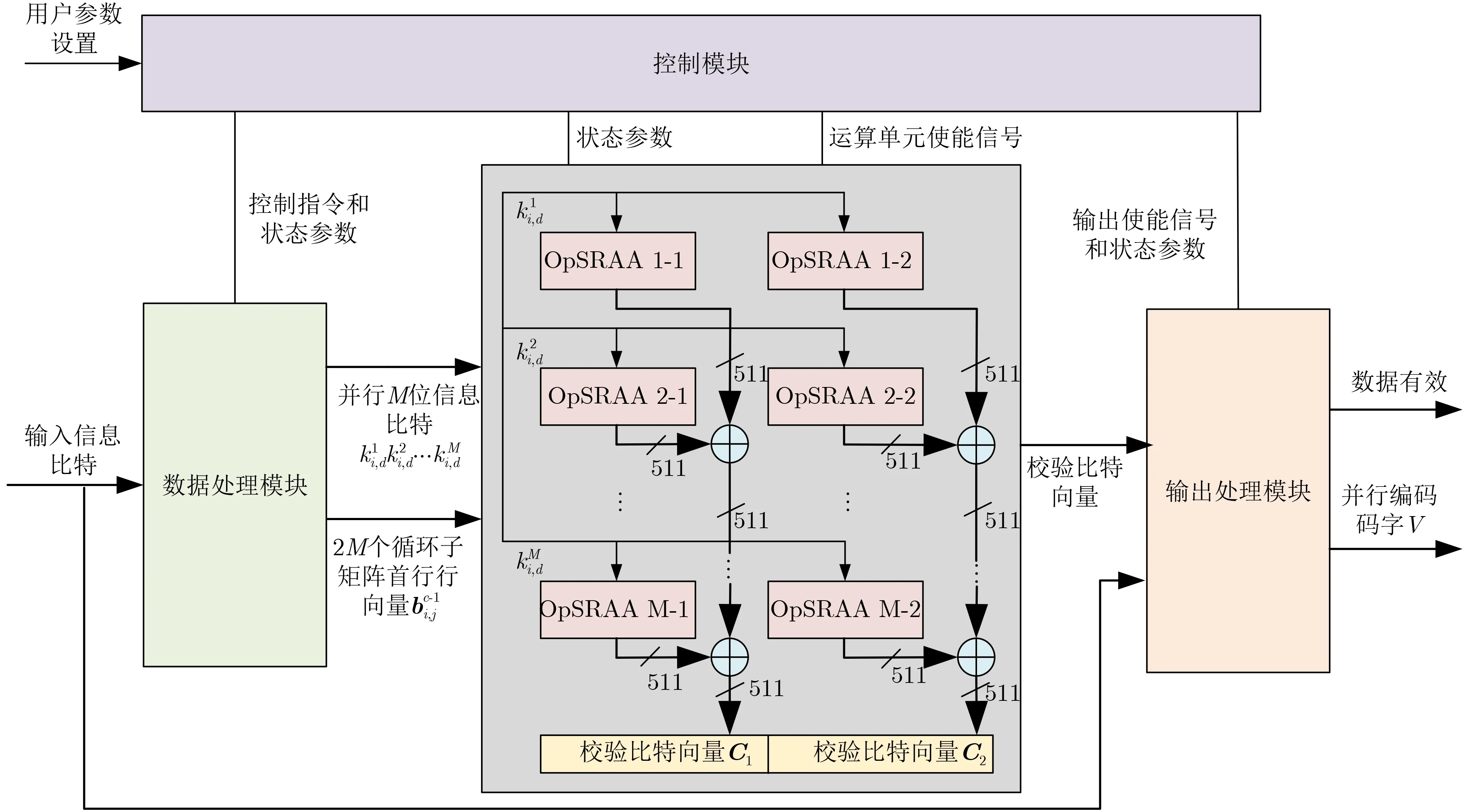

在對(duì)資源、編碼數(shù)據(jù)吞吐率要求苛刻的星地?cái)?shù)傳系統(tǒng)中,應(yīng)根據(jù)實(shí)際應(yīng)用需求選擇合適的編碼并行度M,并行度過(guò)高,會(huì)占用大量硬件資源,并行度太低,則不能滿足編碼數(shù)據(jù)吞吐率要求,大多數(shù)文獻(xiàn)中的編碼器僅支持單一的編碼并行度,靈活性較差。另一方面,當(dāng)今飛行器和地面系統(tǒng)通常只能處理32 bit倍數(shù)結(jié)構(gòu)的數(shù)據(jù),(8176, 7154)碼并不滿足這個(gè)條件,為在實(shí)際空間通信系統(tǒng)中獲得應(yīng)用,需將(8176, 7154)碼縮短和調(diào)整為(8160, 7136)碼并在編碼時(shí)進(jìn)行添加32 bit幀頭、加擾等操作[4]。針對(duì)上述需求,設(shè)計(jì)了如圖1所示的低復(fù)雜度可重構(gòu)LDPC編碼器。包括控制模塊、數(shù)據(jù)處理模塊、并行編碼模塊和輸出處理模塊。

圖1 低復(fù)雜度可重構(gòu)LDPC編碼器

3.2 低復(fù)雜度設(shè)計(jì)

圖2 低復(fù)雜度可重構(gòu)LDPC編碼器工作流程

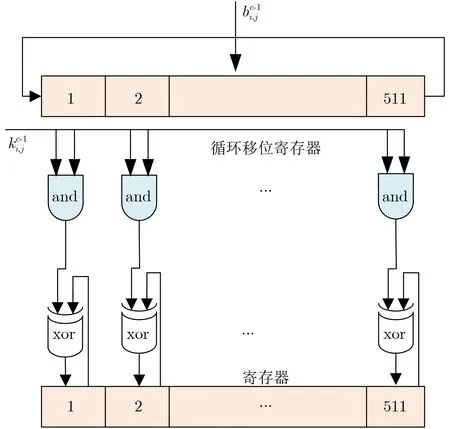

圖3 SRAA單元

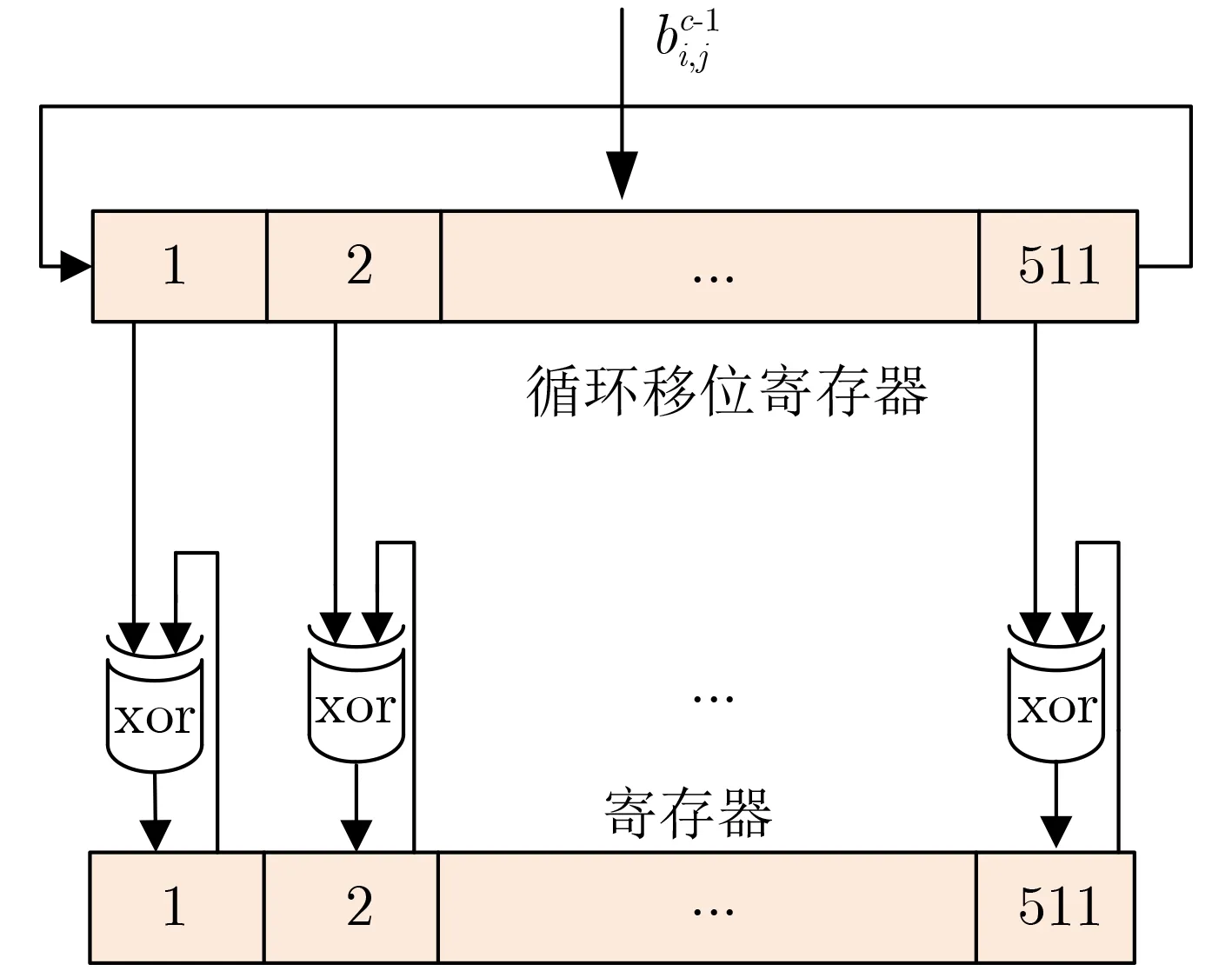

由于信息比特在二元域取值,當(dāng)輸入信息比特為0時(shí),經(jīng)過(guò)與門(mén)運(yùn)算的結(jié)果為0,與寄存器中的值進(jìn)行異或時(shí),不會(huì)改變寄存器中的值,因此可將SRAA進(jìn)行優(yōu)化,只在輸入信息比特為1時(shí),將循環(huán)移位寄存器中的值和寄存器中的值進(jìn)行異或并存儲(chǔ)于寄存器中。圖4為優(yōu)化的移位寄存器累加單元(Optimized Shift Register Adder Accumulator,OpSRAA),該單元包括:一個(gè)位寬511 bit用于存儲(chǔ)異或運(yùn)算結(jié)果的寄存器,一個(gè)位寬511 bit用于產(chǎn)生和存儲(chǔ)循環(huán)子矩陣行向量(d,:)的循環(huán)移位寄存器以及511個(gè)用于累加運(yùn)算的二輸入異或門(mén)。

圖4 OpSRAA單元

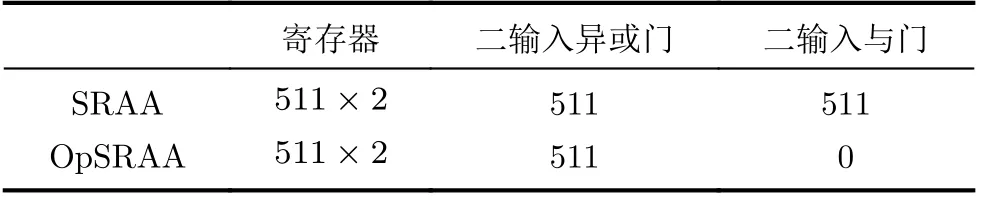

SRAA單元和OpSRAA單元所需硬件資源對(duì)比如表1所示。

表1 SRAA和OpSRAA資源對(duì)比

由以上分析知,利用2M個(gè)OpSRAA單元,經(jīng)過(guò)14×N個(gè)時(shí)鐘周期即可計(jì)算得到C,可節(jié)省2×511×M個(gè)二輸入與門(mén),降低了硬件實(shí)現(xiàn)復(fù)雜度。而且本文設(shè)計(jì)的OpSRAA對(duì)于具有準(zhǔn)循環(huán)結(jié)構(gòu)的編碼具有普適性,實(shí)際應(yīng)用時(shí),只需要根據(jù)生成矩陣循環(huán)矩陣階數(shù)改變寄存器的寬度和二輸入異或門(mén)的個(gè)數(shù)。

3.3 并行度可重構(gòu)設(shè)計(jì)

可重構(gòu)硬件設(shè)計(jì)思想是復(fù)用硬件電路中的主要資源,在增加少量控制硬件的情況下增加系統(tǒng)的功能或改善系統(tǒng)的性能[15]。本文將可重構(gòu)設(shè)計(jì)思想應(yīng)用于 LDPC 編碼器來(lái)改善系統(tǒng)性能。

綜上分析,在控制模塊的控制下,采用可重構(gòu)思想設(shè)計(jì)的編碼器可以有效保證編碼器動(dòng)態(tài)自適應(yīng)調(diào)整以適用于不同近地衛(wèi)星通信系統(tǒng)對(duì)編碼指標(biāo)、性能的不同要求,使得所設(shè)計(jì)的編碼器具有靈活性與通用性,而且可以取得編碼數(shù)據(jù)吞吐率和資源消耗之間的良好折中。

4 實(shí)現(xiàn)結(jié)果與分析

4.1 編碼器硬件實(shí)現(xiàn)分析

對(duì)本文提出的低復(fù)雜度可重構(gòu)LDPC編碼器,在Xilinx XC4VLX80-12ff1148型號(hào)FPGA上進(jìn)行了實(shí)現(xiàn),開(kāi)發(fā)環(huán)境為ISE14.7,與其它文獻(xiàn)編碼器對(duì)比結(jié)果如表2所示。

文獻(xiàn)[8]通過(guò)插0處理和改變矩陣結(jié)構(gòu)實(shí)現(xiàn)了2路并行編碼。文獻(xiàn)[11]利用矩陣轉(zhuǎn)換的概念,即只要循環(huán)矩陣的階數(shù)可以分解為兩個(gè)互質(zhì)的數(shù),那么可按照一定規(guī)則將其轉(zhuǎn)換為維度更小的塊循環(huán)矩陣,由于511=7×73,因此文獻(xiàn)[11]將511×511的循環(huán)矩陣轉(zhuǎn)換為73×73的塊循環(huán)矩陣實(shí)現(xiàn)了7路并行編碼。文獻(xiàn)[12]中800 Mbps數(shù)傳吞吐率需求以及Spacewire接口和組幀模塊的設(shè)計(jì)要求編碼在886個(gè)時(shí)鐘周期完成,因此設(shè)計(jì)了98路高并行度編碼。上述文獻(xiàn)只支持單一編碼并行度,而本文提出的編碼器通過(guò)插0處理和拆分循環(huán)矩陣支持2, 4和8 共3種編碼并行度,具有可重構(gòu)性,其中控制模塊有效保證了編碼器的動(dòng)態(tài)自適應(yīng)調(diào)整,提高了編碼器的靈活性與通用性。

從表2可以看出,由于采用OpSRAA單元完成基本編碼運(yùn)算,本文提出的編碼器寄存器資源、查找表資源與文獻(xiàn)[8]采用SRAA單元的編碼器相比分別節(jié)約了13.7%和14.8%,具有低實(shí)現(xiàn)復(fù)雜度。文獻(xiàn)[11]根據(jù)轉(zhuǎn)換的塊循環(huán)矩陣結(jié)構(gòu)和向量乘法運(yùn)算規(guī)則,利用2個(gè)并行移位寄存器累加單元(Parallel Shift Register Adder Accumulator, PSRAA)實(shí)現(xiàn)編碼,且由于編碼并行度7是CCSDS標(biāo)準(zhǔn)循環(huán)矩陣階數(shù)511的約數(shù),可以將信息比特序列直接分割,節(jié)省了插0處理需要的硬件邏輯,而本文為兼容多種編碼并行度,采用了最大化備份編碼策略,因此總體寄存器資源和查找表資源消耗比文獻(xiàn)[11]多。但文獻(xiàn)[11]設(shè)計(jì)的PSRAA需消耗2×73個(gè)7比特寄存器、7×511個(gè) 2 輸入與門(mén)、7×511個(gè)2輸入異或門(mén)和146個(gè)矩陣向量乘法運(yùn)算單元,具有針對(duì)性,而本文設(shè)計(jì)的OpSRAA單元只需要2個(gè)511 bit寄存器和511個(gè)二輸入異或門(mén),相較于PSRAA具有低復(fù)雜度,且對(duì)于具有準(zhǔn)循環(huán)結(jié)構(gòu)的編碼具有普適性,實(shí)際應(yīng)用時(shí),只需要根據(jù)循環(huán)矩陣階數(shù)改變寄存器的寬度和異或門(mén)的個(gè)數(shù)。文獻(xiàn)[12]的編碼器是針對(duì)OFDM鏈路而設(shè)計(jì),除包括核心編碼模塊還包括輸入輸出組幀模塊、數(shù)據(jù)緩存等模塊,因此硬件資源占用較多。

表2 不同文獻(xiàn)編碼器對(duì)比

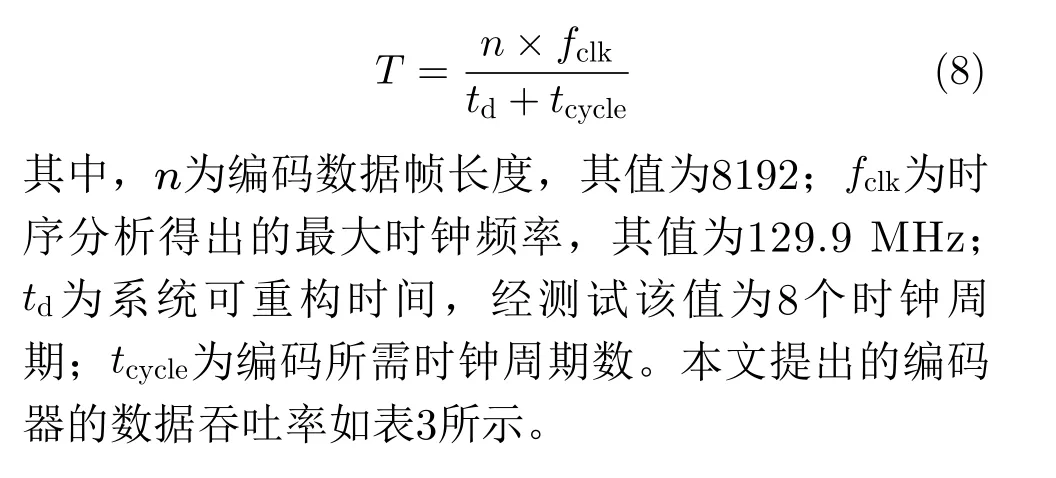

4.2 編碼器性能分析

編碼數(shù)據(jù)吞吐率是衡量編碼器性能的一個(gè)重要指標(biāo)。對(duì)于航天應(yīng)用編碼器,考慮其可靠性和功耗約束,將系統(tǒng)時(shí)鐘約束為125 MHz,借助Timing Analyzer工具,對(duì)本文編碼器進(jìn)行時(shí)序分析,并按式(8)計(jì)算編碼數(shù)據(jù)吞吐率

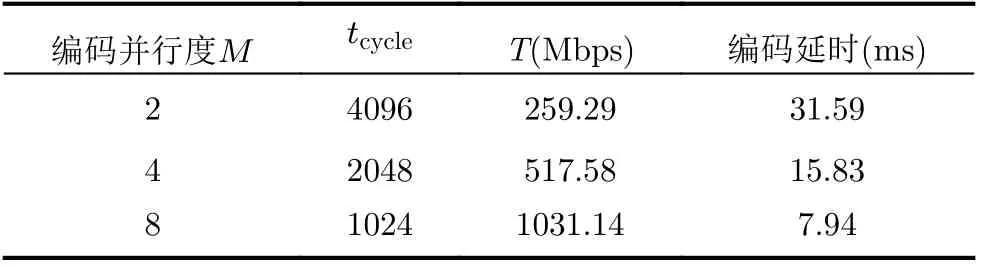

表3 本文編碼器吞吐率

為進(jìn)一步驗(yàn)證本文編碼器的可行性及有效性,搭建如圖5(a)所示硬件平臺(tái)對(duì)該編碼器進(jìn)行實(shí)際測(cè)試并利用高速數(shù)據(jù)接收終端對(duì)其進(jìn)行狀態(tài)參數(shù)監(jiān)控。測(cè)試時(shí),設(shè)置編碼調(diào)制FPGA系統(tǒng)時(shí)鐘為125 MHz,LDPC編碼器并行度為8,數(shù)字調(diào)制方式為QPSK,測(cè)試結(jié)果如圖5(b)所示。

圖5(b)中“①”指示硬件健康狀態(tài),顯示當(dāng)前編碼調(diào)制通道的網(wǎng)絡(luò)連接、外設(shè)驅(qū)動(dòng)、FPGA溫度、硬件電壓等狀態(tài),綠色表示正常的硬件狀態(tài),藍(lán)色表示正常的網(wǎng)絡(luò)連接。“②”指示編碼調(diào)制通道固件及基本性能,包括編碼調(diào)制通道、FPGA固件版本以及支持的中頻和調(diào)制符號(hào)速率范圍。“③”指示編碼調(diào)制流程圖,綠色表示該模塊正常工作,灰色表示該模塊被旁路,從圖中可看到數(shù)據(jù)源經(jīng)LDPC編碼和QPSK調(diào)制后輸出。“④”顯示I, Q調(diào)制基帶波形的時(shí)域圖,便于用戶(hù)觀察調(diào)制數(shù)據(jù)。“⑤”為編碼調(diào)制狀態(tài)參數(shù)顯示,包括編碼開(kāi)關(guān)、卷積開(kāi)關(guān)、調(diào)制開(kāi)關(guān)、中頻、噪聲、碼率、功率等信息,從圖中可看到實(shí)測(cè)編碼數(shù)據(jù)吞吐率為1 Gbps。

圖5 測(cè)試場(chǎng)景與測(cè)試結(jié)果

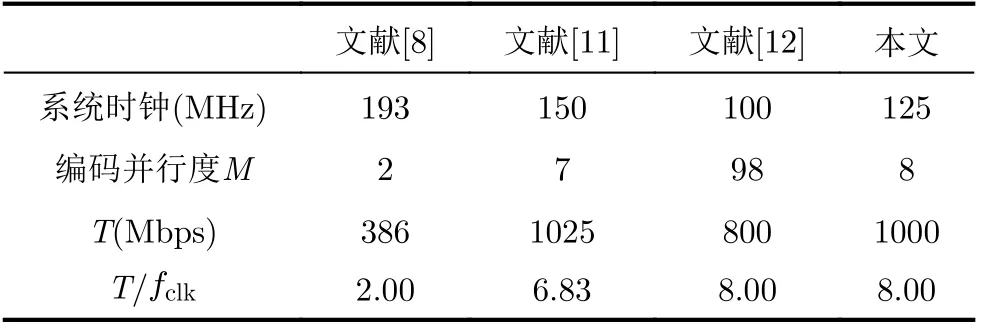

系統(tǒng)時(shí)鐘直接影響編碼數(shù)據(jù)吞吐率的大小,而系統(tǒng)時(shí)鐘會(huì)受硬件平臺(tái)影響,因此本文對(duì)系統(tǒng)時(shí)鐘進(jìn)行歸一化處理,比較歸一化編碼數(shù)據(jù)吞吐率。本文與其它編碼器歸一化編碼數(shù)據(jù)吞吐率比較如表4所示。

由表4可以看出,與文獻(xiàn)[11]設(shè)計(jì)的7路并行編碼器相比,本文歸一化編碼數(shù)據(jù)吞吐率提高了17.1%,文獻(xiàn)[12]采用98路并行編碼達(dá)到了和本文相同的歸一化編碼數(shù)據(jù)吞吐率。由此可見(jiàn),本文設(shè)計(jì)的編碼器更高效。

表4 不同文獻(xiàn)歸一化編碼器吞吐率對(duì)比

綜上分析,本文提出的低復(fù)雜度可重構(gòu)LDPC編碼器,降低了硬件資源規(guī)模,提高了編碼數(shù)據(jù)吞吐率,實(shí)現(xiàn)了硬件資源和編碼數(shù)據(jù)吞吐率之間的動(dòng)態(tài)平衡,而且能夠兼容3種編碼并行度,提高了編碼器的靈活性,可以滿足不同衛(wèi)星通信系統(tǒng)的要求。

5 結(jié)束語(yǔ)

本文面向LEO衛(wèi)星星地高速數(shù)傳系統(tǒng)對(duì)高通量、低復(fù)雜度、高可靠性信道編碼的應(yīng)用需求,提出了一種低復(fù)雜度可重構(gòu)LDPC編碼器。通過(guò)對(duì)輸入信息比特插0處理、拆分循環(huán)矩陣并動(dòng)態(tài)重構(gòu)編碼電路,實(shí)現(xiàn)了并行度可重構(gòu)編碼,提高了編碼器的靈活性與編碼數(shù)據(jù)吞吐率;采用OpSRAA 結(jié)構(gòu)顯著降低了編碼器硬件資源。FPGA實(shí)現(xiàn)結(jié)果表明,本文設(shè)計(jì)的編碼器,在系統(tǒng)時(shí)鐘為125 MHz時(shí),采用8路并行編碼最高編碼數(shù)據(jù)吞吐率可達(dá)1 Gbps,歸一化編碼數(shù)據(jù)吞吐率與并行度相近的編碼器相比提高了17.1%,且寄存器資源和查找表資源與相同平臺(tái)已有方案相比分別降低了13.7%和14.8%。綜上,本文設(shè)計(jì)的編碼器在對(duì)資源、功耗、編碼數(shù)據(jù)吞吐率要求苛刻的LEO衛(wèi)星星地高速數(shù)傳系統(tǒng)中具有較高應(yīng)用價(jià)值。