開關變換器傳導干擾抑制策略綜述

何 杰 劉鈺山 畢大強 李 曉

開關變換器傳導干擾抑制策略綜述

何 杰1劉鈺山1畢大強2李 曉1

(1. 北京航空航天大學自動化科學與電氣工程學院 北京 100083 2. 電力系統國家重點實驗室(清華大學電機系) 北京 100084)

開關變換器廣泛應用于可再生能源并網、電機驅動系統、消費電子供電等領域,其電磁干擾問題日益突出,因此該問題的解決非常重要。該文總結開關變換器傳導干擾抑制策略及其最新進展,重點說明這些策略的基本原理、研究現狀和作用特點。總結的策略主要包括濾波、電橋平衡、反相補償、改進脈寬調制、改進功率器件/模塊封裝、優化電路板設計、改善開關過程等,這些策略可分為阻斷傳導干擾的耦合路徑和削減干擾源的傳導發射兩大類。最后對開關變換器傳導干擾抑制技術的關鍵問題和發展前景進行了討論和總結。

開關變換器 傳導電磁干擾 電磁干擾抑制 電磁兼容

0 引言

與傳統的電能轉換設備相比,開關變換器在體積、質量、效率等方面明顯占優,因而被廣泛應用于各種領域,如可再生能源并網、電機驅動系統、消費電子供電等[1-2]。隨著電力電子技術的發展,開關變換器的功率密度、開關頻率、開關速度等逐漸提高、電路結構逐漸復雜、應用領域逐漸拓展,這導致其電磁干擾(Electromagnetic Interference, EMI)問題日益增多且日趨嚴重[3-6]。

電磁干擾是指電磁能量以輻射或傳導的方式對器件、設備、系統或生命組織造成的意外不利影響。電磁干擾可分為輻射干擾和傳導干擾,前者通過空間傳播,后者通過電路傳播。傳導干擾又可分為共模干擾和差模干擾。共模干擾流通回路由相線/中線和地線構成,不同相線/中線的共模電流大小相等、相位相同;差模干擾流通回路由不同相線/中線構成,不同相線/中線的差模電流大小相等、相位相反。

為避免電磁干擾,有關國際組織和大多數國家紛紛制定電磁兼容標準,規定了包括電磁發射限值和測量在內的諸多規范。輻射發射通常規定在30MHz以上的頻段內,它可以在半電波暗室或開闊場中進行測量,半電波暗室用以模擬開闊場,其主要作用是屏蔽室外電磁發射和防止墻面反射室內輻射發射;傳導發射通常規定在150kHz~30MHz的頻段內,它必須采用線路阻抗穩定網絡進行測量,線路阻抗穩定網絡的主要作用是為受試設備電源線與參考地之間提供穩定阻抗,使受試設備隔離電源端的干擾信號,為測量儀器提供測量端口等[7-8]。

電磁干擾的三要素是干擾源、耦合路徑和受擾體,因此抑制電磁干擾的基本思路是削減干擾源的電磁發射、阻斷電磁干擾的耦合路徑和增強受擾體的抗擾度。文獻[8-9]給出了一些通用性較強或針對特定電子系統的電磁干擾抑制方法,涉及屏蔽、濾波、接地、布線、頻譜管理、時間分離、空間分離和電氣隔離等。

對開關變換器而言,傳導干擾比輻射干擾更易產生且危害更大。開關變換器傳導干擾的噪聲來源按頻率成分從低到高可大致分為電網頻率諧波、開關頻率諧波和開關暫態噪聲,電網頻率諧波是功率二極管或晶閘管整流器對工頻交流電整流的產物,后兩者是功率開關器件進行開關工作和功率二極管電流進行反向恢復的產物[6, 10-11]。

電網頻率諧波主要集中在幾十Hz到幾百kHz之間,其在規定的傳導發射測量頻段內已經大幅衰減,因此其引起的傳導干擾較小。由于功率二極管不可控、晶閘管只能控制導通而不能控制關斷,因此不能通過改變控制策略來主動減小電網頻率諧波,一般只能通過濾波來抑制電網頻率諧波引起的傳導干擾。

開關變換器傳導干擾的主要噪聲來源是開關頻率諧波和開關暫態噪聲,這兩者都可由開關波形表征。前者是開關波形的諧波分量,集中在幾kHz到幾十MHz之間,主要由調制策略決定;后者是開關波形的暫態分量,具有很寬的頻譜,主要受功率開關器件及其門極驅動的特性、功率二極管特性、功率器件/模塊封裝、電路板設計等影響。

基于開關頻率諧波和開關暫態噪聲的這些特點,除通用性較強的濾波外,開關變換器傳導干擾抑制策略還呈現出較高的獨特性。針對開關頻率諧波引起的傳導干擾,一般可以通過改進脈寬調制策略來抑制。針對開關暫態噪聲引起的傳導干擾,除選擇合適型號的功率器件/模塊外,還可以通過改進功率器件/模塊封裝、優化電路板設計、改善開關過程等來抑制。此外,特殊的電橋平衡與反相補償策略也能抑制部分傳導干擾。開關變換器傳導干擾抑制策略分類如圖1所示。圖1對這些策略進行了概括,值得注意的是,改進功率器件/模塊封裝、優化電路板設計、改善開關過程對開關變換器輻射干擾也有抑制作用。

圖1 開關變換器傳導干擾抑制策略分類

文獻[12-19]對開關變換器傳導干擾抑制策略進行了總結,但不夠全面和深入。例如,文獻[12-16]限定開關變換器為開關電源;文獻[17]限定抑制策略為擴頻脈寬調制;文獻[18-19]對抑制策略的總結不夠充實。基于此,本文從阻斷傳導干擾的耦合路徑和消減干擾源的傳導發射兩大方面,全面深入地梳理了圖1所列的各類開關變換器傳導干擾抑制策略,并介紹了最新研究進展,致力于闡述相關策略的基本原理、研究現狀和作用特點等,最后還對相關技術的關鍵問題和發展前景進行了簡要探討。

1 濾波

開關變換器傳導干擾通過電源線和地線耦合到設備或電網中,這可能影響自身用電設備和連接到同一電網的其他設備的正常工作,通常采用電磁干擾濾波器來阻斷這種傳導耦合。電磁干擾濾波器可分為無源電磁干擾濾波器(Passive Electromagnetic interference Filter, PEF)和有源電磁干擾濾波器(Active Electromagnetic interference Filter, AEF)。PEF主要由電感和電容構成,它根據“最大失配阻抗”原則,即對干擾源阻抗和受擾體阻抗分別提供最大失配的輸入阻抗,從而對給定頻段的傳導干擾產生充分大的插入損耗。AEF為包含半導體器件或運放的電子電路,它利用有源消除(Active Can- cellation, AC)技術,能夠有效抑制共模或差模干擾。PEF的設計相對簡單,應用范圍更為廣泛,而AEF的體積和成本更小,且其性能受干擾源阻抗的影響更小。文獻[12, 20]對PEF或AEF做了較好的總結,下面重點從PEF的基本結構、設計及其優化和AEF的分類、功能結構和優化設計等幾個關鍵方面進行梳理。

1.1 無源濾波

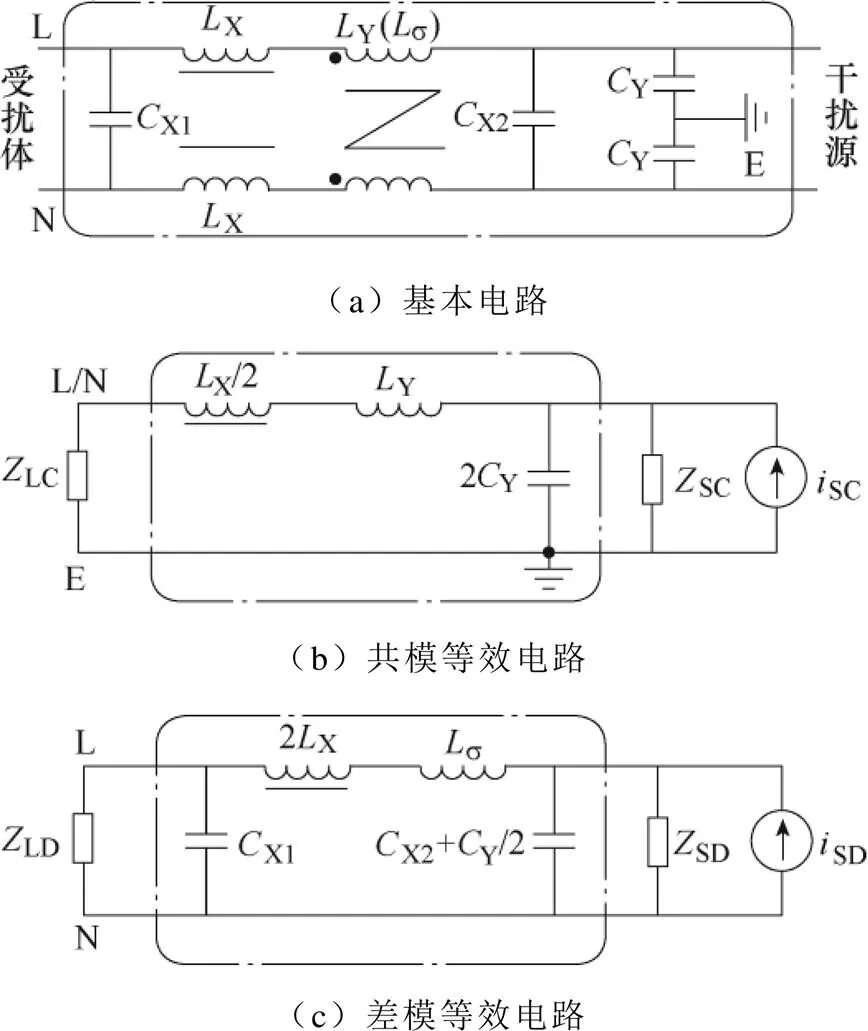

直流/單相交流電路的典型PEF如圖2所示,圖中,SC(SD)為共模(差模)干擾的理想電流源,SC(SD)和LC(LD)分別為共模(差模)干擾的源阻抗和受擾體阻抗,X和X1、X2分別為差模扼流圈和差模電容,Y和Y分別為共模扼流圈和共模電容,σ為Y的漏感且起差模濾波作用。

PEF設計的關鍵流程為:①確定干擾源阻抗;②確定共模和差模干擾幅值譜;③確定PEF的拓撲結構、極點數、元件參數和優化方案。其中①和②既可通過實際電路的測量得到,也可通過建立和分析功率變換系統的電磁干擾模型進行預測。

圖2 直流/單相交流電路的典型PEF

PEF濾波效果與干擾源阻抗和受擾體阻抗密切相關,但在標準的傳導干擾測量環境中,受擾體阻抗可由線路阻抗穩定網絡代替,因此多數研究僅考慮干擾源阻抗變化對PEF濾波效果的影響。干擾源阻抗的提取方法有很多,如插入損耗法[21]、電流探頭法[22]、散射參數法[23]、阻抗擾動法[24]等,這些提取方法的精度和復雜度不同。文獻[21, 25]給出了考慮干擾源阻抗時的PEF設計方案。

共模和差模干擾產生機理不同,因此需要運用噪聲分離技術分別得到共模和差模干擾的幅值譜,來分別設計共模和差模PEF。噪聲分離技術分為基于射頻電流探頭測試、基于軟件實現和基于硬件實現三類。文獻[26]對噪聲分離技術及其特點做了簡要總結。

建立功率變換系統電磁干擾模型是分析和預測電磁干擾的基礎,將此模型用于PEF設計就能避免對實際電路進行干擾源阻抗提取和噪聲分離,從而縮短整體設計周期。系統級電磁干擾建模方法可分為頻域法和時域法[27],前者仿真的速度更快、收斂性更好,但精度有所欠缺;后者與前者相反,文獻[28]對兩者做了簡要總結。目前,系統級電磁干擾的建模對象幾乎涵蓋了所有開關變換器類型及應用領域,如不間斷電源[29]、光伏逆變器[30]、變速電機驅動器[31]、模塊化多電平變換器[32]等。系統級電磁干擾模型的精度由主要的子模塊或元器件高頻模型和電路板雜散參數模型的精度決定,其中重點進行建模研究的子模塊或元器件主要有高頻變壓器[33]、功率器件或模塊[34-36]、PEF[37-38]等。文獻[37]給出了基于功率變換系統電磁干擾模型的PEF設計方案。

通過變更PEF基本電路的濾波元件,很容易得到其他拓撲結構,以滿足不同的濾波需求。共模或差模PEF的基本拓撲結構有LC型、CL型、T(LCL)型和p(CLC)型,它們可以通過級聯以提高插入損耗[39],文獻[6, 40]指出四種拓撲結構依次適用于低S高L、高S低L、低S低L、高S高L的情形,S和L分別為共模或差模干擾的源阻抗和受擾體阻抗。

PEF極點數和元件參數不僅取決于插入損耗,還受接地漏電流限值、PEF體積或質量等影響。文獻[41]給出一種基于粒子群優化的PEF自動設計方案,綜合考慮了各種影響因素,如插入損耗、接地漏電流限值、差分損耗電流限值、開關變換器的額定電壓和額定電流、PEF尺寸等因素。

在滿足濾波需求后,通過對PEF進行優化設計,能夠進一步提升其性能。PEF的優化設計目標主要有減小體積或質量[42]、消除雜散參數[43]、抑制諧振或增強穩定性[44]、提高效率[45]、降低諧波失真 率[46]等。

目前,針對PEF的研究主要集中在電磁干擾建模及其仿真分析和PEF優化設計上。研究的主要內容包括:對大功率、復雜結構或基于寬禁帶半導體器件的功率變換系統進行電磁干擾建模;解決電磁干擾模型仿真分析的精度、收斂性和速度之間的矛盾;減小PEF體積或質量等。

1.2 有源濾波

AEF有多種分類方式,按照采樣和補償方式可分為電壓采樣電壓補償型、電壓采樣電流補償型、電流采樣電壓補償型、電流采樣電流補償型;按照采樣和補償位置可分為前饋型和反饋型;按照控制方式可分為模擬控制型和數字控制型;按照所抑制的傳導干擾類型可分為共模型和差模型等。文獻[47]對各類AEF的優缺點和應用條件做了較好總結。

AEF主要由采樣電路、處理電路和補償電路構成。采樣電路為電流互感器或基于RC的高通濾波器及相應的噪聲分離電路,前者用以感測共模或差模電流噪聲,后者用以感測共模或差模電壓噪聲;模擬控制型處理電路通常為運放或推挽式放大器,而數字控制型處理電路由高速模數轉換器、基于DSP或FPGA的控制單元和高速數模轉換器構成,都用以提供增益;補償電路為變壓器或RC電路,分別用于注入補償電壓和補償電流。文獻[20]對AEF的電路結構做了較好總結。

AEF的低頻性能較好,而PEF的高頻性能較好,因此將兩者級聯形成混合電磁干擾濾波器(Hybrid Electromagnetic interference Filter, HEF),則能綜合二者的優點,從而提高濾波器的整體性能,而且還能通過提高PEF的截止頻率來減小PEF的體積或質量[48]。

文獻[49-50]給出了AEF/HEF的設計流程,其實驗結果明確了AEF/HEF抑制傳導干擾的作用。與PEF設計相比,AEF/HEF設計要重點考慮系統的穩定性。AEF/HEF的低頻(小于150kHz)不穩定性源于采樣電路引入的相移,而高頻(大于30MHz)不穩定性源于運放大的增益衰減以及電路的雜散效應,不穩定會顯著增加電路的噪聲。AEF/HEF建模的準確性對穩定性分析及設計至關重要,AEF/HEF建模的難點在于提取電路高頻雜散參數和確定干擾源阻抗,文獻[51]討論了共模AEF、差模AEF和HEF的建模過程,并給出了穩定性設計方案。

目前,AEF/HEF的設計還存在增益帶寬矛盾、提高響應速度、抑制浪涌電壓、降低功率損耗等問題或難點。另外,文獻[52-53]討論了數字控制型AEF的分析和設計,但相關技術仍有待進一步發展。

2 電橋平衡與反相補償

直接阻斷傳導干擾路徑能夠有效抑制電磁干擾,除此之外,還可以采用基于電橋平衡與反相補償原理的策略,它們通過改變開關變換器內部電路結構或元器件分布將傳導噪聲束縛在內部電路,使之不對外部電路造成干擾。

文獻[54-55]提出一種基于惠斯通電橋平衡原理的共模干擾抑制策略,其通過增添元器件或改進電路設計使4個橋臂的阻抗對稱,同時使干擾源和受擾體分別處于電橋的兩個對角線上,從而抑制共模干擾。由于該策略的共模干擾抑制效果與阻抗對稱程度密切相關,其對傳導干擾模型的阻抗精度要求很高。

文獻[56]提出一種基于電流補償的共模干擾抑制策略,其通過反相變壓器獲得一個與對地共模電壓相位相反的補償電壓,同時在補償端增加電容器以接收全部的接地漏電流,從而抑制共模干擾。該策略本質上是一種通過引入其他元件來消除功率器件對地雜散電容的方法,文獻[57]分析了其等效電路原理,并給出了其在幾種常見DC-DC變換器上的應用實例。文獻[58]提出了基于電壓補償的共模干擾抑制策略,同時通過反相變壓器獲得與共模電壓相位相反的補償電壓,但是補償電壓和共模電壓直接串聯相消。與AEF的有源補償策略相比,上述補償策略由無源器件實現,且作用于開關變換器內部電路,用以直接消除功率器件對地雜散電容的影響。上述補償策略主要抑制中低頻段的共模干擾,且其抑制效果受補償元件的雜散參數和功率器件對地雜散電容的估算精度影響。

相比于濾波策略,電橋平衡與反相補償策略的設計和實現更為簡單,所增加元件的體積或質量較小,但其只能用來抑制共模干擾,且實際抑制效果難以準確預測。此外,電橋平衡與反相補償策略對開關變換器其他工作性能的影響仍有待研究。

3 脈寬調制

脈寬信號的主要參數如圖3所示,脈寬信號()主要由周期(或頻率f)、脈寬、位置(延遲時間)等參數確定,這些參數隨時間的變化特性很大程度上決定了開關波形的特性。常規脈寬調制主要有載波脈寬調制(Carrier-Based PWM, CBPWM)和空間矢量脈寬調制(Space Vector PWM, SVPWM),脈寬信號的頻率和位置在工作過程中通常固定不變,而脈寬按照周期性規律變化,因此常規脈寬信號為周期函數,這導致開關波形的噪聲能量主要集中在離散的諧波頻率附近[59]。該問題的一種有效解決方案是降低開關頻率,但這與電力電子技術的發展趨勢相違背,因此工程應用價值不高。另一種解決方案是采用擴頻脈寬調制(Spread Spectrum PWM, SSPWM),即通過動態調整脈寬信號的部分或全部參數,將集中的開關頻率諧波噪聲能量分布在更寬的頻段內,從而有效降低這些噪聲能量的幅值以滿足電磁兼容標準。此外,一些基于特定優化目標的脈寬調制策略也能抑制部分開關波形噪聲,如旨在消除或降低開關變換器輸出波形指定部分諧波噪聲的特定消諧脈寬調制(Selective Harmonic Elimination PWM, SHEPWM)和用于降低變速電機驅動系統共模電壓的脈寬調制等。

圖3 脈寬信號的主要參數

3.1 擴頻脈寬調制

按照脈寬信號參數動態調整方式的不同,擴頻脈寬調制主要分為隨機脈寬調制(Random PWM, RPWM)、混沌脈寬調制(Chaotic PWM, CPWM)和周期脈寬調制(Periodic PWM, PPWM)。設擴頻脈寬調制的動態調整參數為載波頻率C(即開關頻率),則次開關頻率諧波分量經調制后可表示為

式中,An為hn(t)的幅值;DfC為載波頻率的偏移幅值;x(t)用以表征載波頻率的動態調整方式,其值域為[-1, 1]。根據卡森(Carson)法則[60],hn(t)在功率譜上展開的帶寬約為2nDfC,圖4比較了常規和周期脈寬調制的開關頻率諧波功率譜。

文獻[17, 61-62]對擴頻脈寬調制做了較好的闡述和總結,其局限性主要有:①擴頻脈寬調制不能降低開關波形的總噪聲能量;②由于開關變換器的元器件參數與開關頻率密切相關,開關頻率動態變化使相關參數的設計或選取變得困難;③實際應用中難以生成真正的隨機數,隨機脈寬調制抑制開關頻率諧波的效果依賴于偽隨機數的統計結果;④不能有效地控制輸出電流紋波和開關損耗等問題。

3.2 特定消諧脈寬調制

文獻[63-64]對特定消諧脈寬調制做了較好闡述和總結,這里簡述其基本原理和作用特點并補充最新相關文獻。特定消諧脈寬調制的基本原理:首先,基于開關變換器輸出波形的特性,如相數、極性、對稱性、電平數及幅值等,對輸出波形進行傅里葉級數分解;其次,選擇一組擬處理諧波并確定處理目標,如諧波消除[65]、諧波最小化[66]、總諧波畸變率最小化[67]、諧波抑制[68]等,由此得到表征基波與擬處理諧波的幅值和開關角關系的超越方程組;最后,求解目標開關角,當超越方程組較為簡單時,可采用牛頓迭代法進行求解,當超越方程組較為復雜時,可采用一些先進算法進行求解,如差分和聲搜索[65]、帝國競爭算法[66]、粒子群優化[69]、人工神經網絡[68]等,更多算法可參考文獻[64]。

由于每個開關角都對應一次開關動作,因此開關變換器輸出波形的基波角頻率不能過高,否則會出現相鄰開關動作時間間隔過短的情況,使功率開關器件不能安全工作。此外,當擬處理諧波數目較大時,開關角數目必須相應增加,這導致超越方程組的求解難度劇增,需要先進的求解算法和硬件設備,因此也限制了特定消諧脈寬調制的應用。

3.3 用于降低共模電壓的脈寬調制

電壓源逆變器(Voltage Source Inverter, VSI)具有較高的控制質量和能效,因此廣泛應用于變速電機驅動系統。對于常規VSI(兩電平三橋臂三相VSI),當其采用常規脈寬調制時,中性點會產生對地共模電壓,常規變速電機驅動系統如圖5所示,此共模電壓可近似表示為

常規VSI的開關組合共有八種,其中零電壓矢量對應的共模電壓為±DC/2,非零電壓矢量對應的共模電壓為±DC/6,因此采用常規脈寬調制的共模電壓為幅值DC/2的交流電壓。此共模電壓通過電機對地雜散電容產生共模電流和共模干擾,或通過電機內部雜散電容產生軸承電流,最終危害電機的正常工作。為減輕或消除這些危害,除特定消諧脈寬調制外,學者們還提出了諸多用于降低共模電壓的脈寬調制(Reduced Common-Mode Voltage PWM, RCMV-PWM)策略。

一類RCMV-PWM針對常規VSI而提出,其由常規脈寬調制直接改進而來。基于常規空間矢量脈寬調制的改進策略主要有有效零模態脈寬調制(Active Zero State PWM, AZPWM)、鄰近模態脈寬調制(Near State PWM, NSPWM)、疏遠模態脈寬調制(Remote State PWM, RSPWM)等,它們的核心思想在于避免直接使用產生高共模電壓的零電壓矢量,而使用非零電壓矢量合成并替代零電壓矢量,從而降低共模電壓幅值。基于常規正弦脈寬調制的改進策略主要有載波移相脈寬調制(Carrier Phase Shift PWM, CPSPWM)及載波峰值位置調制(Carrier Peak Position Modulation, CPPM)等,前者采用三個相位相差120°的正弦波與三個峰值錯開的三角載波進行比較,減小了零電壓矢量出現的概率,后者在前者的基礎上徹底消除了零電壓矢量。文獻[70-72]對這些RCMV-PWM做了較好的分析和比較。

另一類RCMV-PWM針對其他拓撲結構的VSI而提出,其通過中點鉗位、級聯、并聯、增加半橋支路等方法來增加常規VSI的電平數、橋臂數和相數等參數,進而增加開關組合并提高脈寬調制的自由度,最終也能降低甚至消除共模電壓。按照增加參數的類型,這類RCMV-PWM的作用對象主要可分為多電平VSI[73]、多橋臂VSI[74]、多相VSI[75-76]和多電平多橋臂VSI[77]等。這類RCMV-PWM可分為兩個子類:①類似于常規VSI,上述VSI可以使用產生低共模電壓的電壓矢量合成并替代產生高共模電壓的電壓矢量,或改進載波移相脈寬調制,從而降低共模電壓幅值;②當電平數為偶數和相數/橋臂數為奇數不同時成立,上述VSI總存在使共模電壓為0的電壓矢量[78],如果僅使用這些電壓矢量進行脈寬調制,就能徹底消除共模電壓。文獻[73-74, 76]的實驗結果明確了上述部分RCMV- PWM策略抑制共模干擾的作用。

RCMV-PWM有可能使VSI的輸出電流質量惡化、開關損耗增加以及調制比降低,一些RCMV- PWM結合了最優化控制[79]、模型預測控制[80]等,在改善這類問題和降低共模電壓中進行折中考慮。

總之,RCMV-PWM能夠有效降低VSI的共模電壓,而且部分RCMV-PWM能夠有效抑制共模干擾。然而,RCMV-PWM對差模干擾的影響目前尚缺乏分析,并且除共模電壓外,每個橋臂的開關電壓和開關電流也是重要干擾源,特別是當VSI拓撲結構復雜化后,開關器件明顯增多,由此產生的電磁干擾可能更加嚴重,這些問題都需要進一步研究。

3.4 基于其他優化目標的調制策略

單純以降低電磁干擾為目的的調制策略可能損害開關變換器的其他性能,一些基于其他優化目標的調制策略能夠兼顧電磁干擾抑制功能。

文獻[81]提出模型預測脈寬調制,即通過建立電流紋波或電機轉矩脈動的預測模型,來調整開關頻率或脈沖分布,以實現對上述預測模型參數的控制,仿真和實驗結果顯示,中低頻傳導干擾得到一定程度的抑制。文獻[82]提出改進的積分-微分(S-D)調制,其基于過采樣和噪聲整形技術來產生可變的開關頻率和占空比,同時實現對負載改變的快速瞬態響應,具有降低傳導干擾的作用。文獻[83]提出改進的脈沖序列調制,其通過輸出電壓與參考電壓的比較結果來調整高、低頻率或占空比控制脈沖的組合方式,用以減小輸出電壓波動和提高DC-DC變換器的輕載效率與瞬態響應速度,具有降低傳導干擾的作用。

上述調制策略能夠抑制傳導干擾的根本原因在于脈寬信號參數不再固定或周期性變化,而是呈現出部分分布的特性。

4 功率器件/模塊封裝和電路板設計

開關變換器的雜散阻抗由功率器件/模塊及其封裝和電路板設計決定,主要包括驅動回路與功率回路的雜散電感、功率器件的極間電容和功率模塊對地的雜散電容,這些雜散阻抗影響開關速度并產生過沖、高頻振蕩和位移電流等現象,進而影響電磁干擾特性。

文獻[84-87]研究了驅動回路或功率回路雜散電感對開關特性的影響。文獻[84]指出由于驅動電阻的過阻尼作用,驅動回路雜散電感對開關特性的影響較小,但驅動回路和功率回路耦合的共源極電感對開關特性影響較大,它對驅動電壓起負反饋作用,進而能降低開關電流變化速度,對差模干擾噪聲有一定程度的抑制。一些功率開關器件通過增加開爾文源極引腳使驅動回路和功率回路解耦,雖然略微提高了開關速度,但總體上改善了開關電壓的過沖和高頻振蕩[85]。文獻[86]表明通過降低開關波形的過沖幅值,可減小高頻振蕩的能量,并降低相應振蕩頻率附近的幅值譜。文獻[87]表明減小功率回路的雜散電感雖然能夠降低過沖幅值,但也略微提高了開關速度,于是開關波形幅值譜在振蕩頻率附近下降,但在更高的頻段內略有上升。

文獻[88-89]研究了雜散電容對開關特性的影響:文獻[88]分析了功率器件的各個極間電容對開關特性的影響,為功率器件選擇提供了參考;文獻[89]表明變化的開關電壓在功率模塊對地的雜散電容上產生位移電流,進而產生傳導干擾。

總之,開關變換器的雜散阻抗參數眾多且部分參數對開關波形幅頻特性的影響是復雜的,但減小雜散阻抗在總體上能夠有效抑制高頻電磁干擾,此外還可以減小電壓/電流應力、開關損耗等。特別是隨著寬禁帶半導體器件的發展,開關速度不斷提高,過沖和高頻振蕩、位移電流等現象愈發嚴重,減小雜散阻抗成為解決該問題并抑制部分高頻電磁干擾的可行和必要策略,而這個目標無疑需要通過改進功率器件/模塊封裝和電路板設計來實現。

4.1 功率器件/模塊封裝

常規的功率器件/模塊封裝結構示意圖如圖6所示,其構成要素主要包括功率器件芯片、基板、襯板、焊層、鍵合線、端子、密封劑和塑料外殼等。功率器件/模塊封裝的雜散電感主要產生于襯板走線、鍵合線和端子等,表1列出了減小這些雜散電感的通用方法[90]。功率器件/模塊封裝的雜散電容主要產生于絕緣襯板,絕緣襯板通過散熱器和地線相接[91]。相比于分立的功率器件封裝,多芯片整合的功率模塊封裝能夠減少互連和端子、提高功率密度、增加設計自由度,因此能夠更加有效地減小雜散 電感。

圖6 常規功率模塊封裝結構示意圖

表1 減小功率器件/模塊封裝雜散電感的通用方法

Tab.1 General methods to reduce stray inductance in power device/module package

功率模塊封裝主要通過改進芯片、襯板走線的布局和互連方式來減小雜散電感。部分文獻基于引線鍵合的互連方式,設計一些新的封裝電路布局,如P-cell和N-cell[90],雙端電源[92]等,其本質是通過減小電流環路的長度或面積來減小雜散電感。另外一些文獻采用新的互連方式,如在芯片焊盤上使用直接沉積銅的平面互連封裝[93]和通過襯板通孔進行芯片互連的3D互連封裝[94]。前者通過縮短和加寬電流路徑減小雜散電感,后者通過減小電流環路的長度和面積減小雜散電感。文獻[90, 92, 94]的實驗結果表明,降低功率器件/模塊封裝的雜散電感能夠有效降低部分傳導或輻射干擾。

部分功率模塊芯片直接安裝在電路板上,并通過改進功率回路布局來減小雜散電感。如文獻[95]提出多回路的概念,將常規的功率回路拆分成多個電流流向交錯的回路,極大地減小了各回路間的互感,從而減小雜散電感。文獻[96]提出一種垂直于電路板平面的功率回路,有效減小回路面積,從而減小雜散電感。文獻[97]提出平行于電路板平面的功率回路,它能夠在襯板的接地平面層感應出渦流,從而利用渦流效應減小回路的雜散電感。

通過改進功率模塊封裝也能減小雜散電容并抑制相關的電磁干擾。文獻[87]研究表明,半橋電路輸出節點對地雜散電容是影響共模干擾的主要參數,相比于分立功率器件封裝,所設計半橋功率模塊封裝的輸出節點對地雜散電容得到有效減小,對應的共模干擾整體上下降了約10dB。文獻[94]提出一種雙邊冷卻的功率模塊封裝,該封裝具有3層銅質基板,半橋電路輸出節點與中間層基板相連,有效地減小了對地雜散電容。文獻[98]提出一種平面互連和3D互連混合的半橋模塊封裝,使共模電流在10MHz以上的頻段內至少降低了15dB。

文獻[99-101]對上述部分封裝策略做了總結,并指出隨著寬禁帶半導體功率器件的應用,高速開關、熱管理、高溫工作、高壓隔離等問題對功率器件/模塊封裝提出了更高的要求。當前,多芯片整合的寬禁帶半導體功率模塊封裝逐漸成為研究主流,如何在滿足其他功能要求的基礎上有效減小封裝電路的雜散阻抗和抑制與之相關的傳導或輻射干擾成為研究熱點。

4.2 電路板設計

功率器件/模塊封裝外部的主要雜散阻抗為母線電感、電路走線對地的雜散電容和其他元件的高頻雜散阻抗,其中前兩者的大小和分布主要由電路板設計決定。文獻[102-103]給出了降低電磁干擾的電路板通用設計方法,下面主要討論減小母線電感和電路走線對地的雜散電容的設計方法。

母線電感是構成功率回路雜散電感的重要部分,采用疊層母排是一種有效減小母線電感的方法。文獻[104]討論了趨膚效應、互感效應、功率回路長度、疊層母排間距等對疊層母線雜散電感的影響。文獻[105]給出了雙層母排的電路模型和雜散電感計算方法,且實驗結果表明,相比于常規的母線設計,采用雙層母排設計使得逆變器的共模電流明顯減小。文獻[106-107]提出一些疊層母排的設計方案以減小母線電感,改善了開關波形的振蕩現象。

電路走線對地的雜散電容很大程度上決定于散熱器及其接地方式。文獻[108]比較了鋁質散熱器和有機聚合物質散熱器,實驗結果表明,后者導致直流變換器共模干擾強度明顯小于前者。文獻[109]提出采用絕緣金屬襯板來直接散熱,雖然提高了功率密度,但導致傳導干擾比常規散熱器更嚴重。文獻[110]比較了單散熱器接地和分散式散熱器接地,實驗結果表明,后者導致的共模和差模干擾略小于前者。

5 開關過程控制

在理論分析時,常將開關波形簡化為梯形波。開關速度對梯形波幅值譜及其包絡的影響如圖7所示(開關頻率為10kHz,占空比為0.5,值域為[0, 1],r和f分別指波形從10%上升到90%和從90%下降到10%的時間)。開關速度是影響開關波形高頻幅值譜的關鍵因素之一,降低開關速度能夠降低開關波形的高頻幅值譜,進而從源頭上抑制開關變換器的高頻傳導干擾。降低開關速度的常規策略為增大驅動電阻或在開關器件輸入/輸出側增加電容,這些策略易于實現且效果良好,但在抑制電磁干擾和降低開關損耗之間存在嚴重的制約關系[111],為避免或改善這種問題,一些新的策略如增設緩沖電路、軟開關和有源門極驅動控制等受到廣泛關注。

圖7 開關速度對梯形波幅值譜及其包絡的影響

5.1 緩沖電路和軟開關

緩沖電路能夠用來降低開關損耗、開關速度、過沖幅值和電磁干擾強度等,它主要由電阻、電容、電感、二極管VD和輔助開關器件等構成,按照有無電阻和輔助開關器件可分為有損無源型、無損無源型和有源型三類。通常軟開關電路指無損無源型和有源型緩沖電路,借助于特殊控制策略,其能夠有效避免暫態開關電壓、電流的交疊。按照發展歷程,軟開關電路還可以分為準諧振電路、零開關脈寬調制電路、零轉換脈寬調制電路。此外,按照暫態開關電壓、電流的變化時序,軟開關又分為零電壓軟開關和零電流軟開關。文獻[112]對各類緩沖電路的拓撲結構做了簡要總結。文獻[113-114]對軟開關電路及相應控制技術做了較好總結,這里簡述各緩沖電路的作用特點并補充相關最新文獻。

有損無源緩沖電路主要指RC或RCD電壓緩沖電路和RL或RLD電流緩沖電路,其中鐵氧體磁珠可以等效成一種特殊的RL電流緩沖電路。該類電路的特點是能夠有效衰減開關波形的高頻振蕩。文獻[115]的實驗結果明確了有損無源緩沖電路抑制高頻電磁干擾的作用。

無損無源緩沖電路為由LCD元器件組成的諧振電路,其能夠將吸收的能量反饋到功率回路,從而有效減小功率損耗。該類電路的諧振周期隨輸入電壓或負載變化而改變,因此只能采用脈沖頻率調制。有源緩沖電路除LCD元器件外還有輔助開關器件,其能夠使諧振現象僅發生在開關暫態。該類電路能夠提高開關變換器的開關頻率和功率密度,但其拓撲結構、參數設計和驅動控制較為復雜,且為進一步降低開關損耗和抑制電磁干擾,還應使輔助開關器件實現軟開關,這些問題限制了其工程應用。

文獻[116-117]的實驗結果明確了軟開關技術抑制高頻電磁干擾的作用,但它們都將研究重點放在了軟開關電路的拓撲結構、工作原理和硬件設計上,高頻電磁干擾抑制作用僅作為仿真和實驗結果顯示,對諧振過程缺乏控制,沒能揭示諧振過程和高頻電磁干擾特性之間的深層關聯。文獻[118]提出一種軟開關輔助換向極逆變器,采用可變定時控制使輸出電壓的暫態時間不隨相電流變化,于是輸出電壓的轉折頻率可通過暫態時間進行初步預測,實驗結果驗證了這種預測的可行性,同時表明輸出電壓幅值譜在0.6~10MHz范圍有明顯下降。

5.2 有源門極驅動控制

有源門極驅動通過對開關波形的精細控制實現多樣的應用目的,如減少開關延時、管理死區時間、降低開關損耗、解決電流/電壓均衡、抑制橋臂串擾、降低開關波形過沖幅值、抑制高頻電磁干擾等,這使得有源門極驅動控制技術受到廣泛關注。

有源門極驅動控制有開環和閉環之分。有源門極驅動開環控制即在開關器件暫態過程的不同階段,針對性地調節驅動電壓[119]、驅動電流[120]或驅動電阻[121],使之與參考波一致,以控制輸入電容的充放電速度,最終改善暫態特性。通常使輸入電容的充放電速度在開關電壓/電流快速變化階段放緩,而在其他階段加速。在一些有源門極驅動器中,驅動參數只能在有限的幾個值之間切換[119]。隨著數字驅動器的提出,驅動參數得到量化,微調開關波形的目標得以實現[120]。

由于開關器件暫態時間較短,為使動態響應足夠快,有源門極驅動閉環控制多由模擬反饋電路實現。有源門極驅動閉環控制主要分為基于d/d或d/d反饋的閉環控制和開關電壓/電流軌跡控制,后者將在下一節中闡述,前者即通過有源電路將采集到的d/d或d/d信號轉換成驅動電壓[122]或驅動電流[123],然后將此驅動電壓或驅動電流加到開關器件門極形成閉環反饋,以實現多樣的控制目的。由于驅動電流可以直接對輸入電容充放電,因此將d/d或d/d反饋信號轉換成驅動電流可使系統的動態響應更加迅速。

文獻[124]對IGBT的有源門極驅動控制技術做了較好總結。隨著寬禁帶半導體器件的應用,開關速度明顯提高,橋臂串擾、開關波形的過沖和振蕩、高頻電磁干擾等問題愈加凸顯,這使精細控制d/d或d/d顯得更加重要,但同時對有源門極驅動控制技術提出了更高的要求。文獻[119]提出一種基于智能模型的軌跡優化有源門極驅動器,對碳化硅器件帶來的電磁干擾和開關損耗進行優化權衡。文獻[125]提出的碳化硅有源門極驅動器降低了開關電壓過沖幅值,并將振蕩頻率附近的噪聲幅值降低約15dB。文獻[126]提出一種開環控制的氮化鎵數字驅動器,其時間分辨率可達150ps,實驗結果表明,所控器件的開關電壓幅值譜在高頻范圍明顯下降,但所控器件的驅動電壓和同一橋臂另一器件的開關電壓的幅值譜有所上升。文獻[127]對現階段針對碳化硅器件開關速度控制的有源門極驅動技術做了總結,并對碳化硅器件引起的高頻電磁干擾問題做了簡要分析。

當前,有源門極驅動控制技術的發展仍面臨諸多挑戰,包括可靠性和穩定性分析、動態響應速度提升、多控制功能集成、控制參數自適應調整、新型控制策略設計以及寬禁帶半導體器件控制等。

5.3 暫態軌跡控制

實際上開關波形并非理想的梯形波,其暫態軌跡是非規則上升或下降的,在暫態時間相同的情況下,開關波形以不同的軌跡上升或下降,也將引起不同的高頻電磁干擾。基于此,學者們開始研究暫態軌跡對電磁干擾特性的影響,從而設計出一些特殊的暫態軌跡,并分析具有這些暫態軌跡的開關波形在時域和頻域的對應關系,此外還通過改進驅動器設計直接控制和生成這些暫態軌跡[128]。

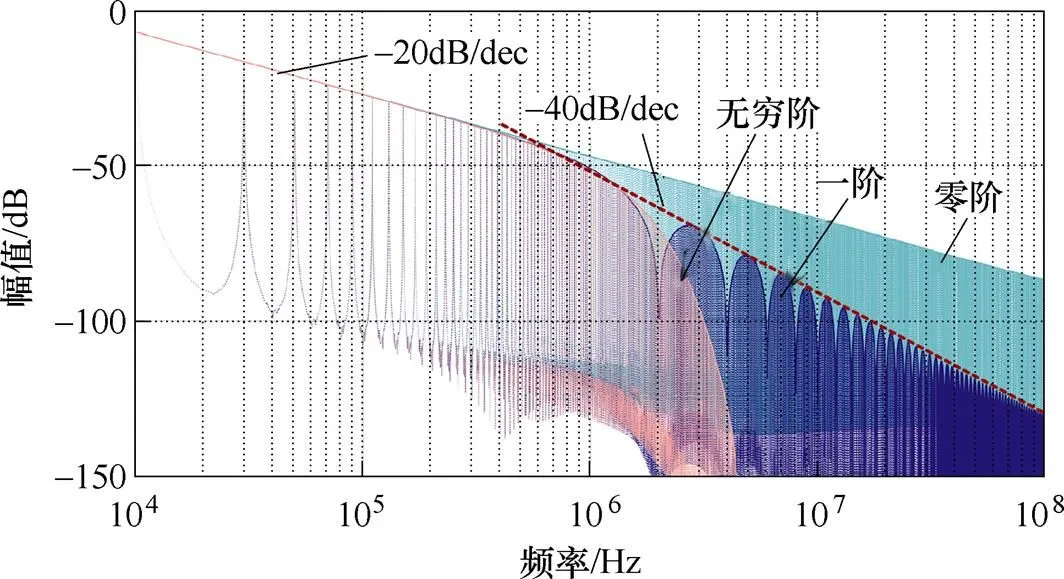

如圖7所示,梯形波的幅值譜在高頻范圍的下降速度為-40dB/dec。文獻[129]提出了二階可導的“S”形暫態軌跡開關波形,其幅值譜在高頻范圍也能實現-60dB/dec的下降速度。文獻[130]將開關波形表示為脈寬調制函數和門函數卷積的形式,其中脈寬調制函數決定開關波形的周期、脈寬和脈沖位置;門函數決定所提開關波形的暫態時間和可導階數,其目的是通過提高暫態軌跡的可導階數來提升開關波形的圓滑程度,進而降低開關波形幅值譜。文獻[130]利用不確定性原理證明,當且僅當門函數為高斯函數時,暫態軌跡無窮階可導且開關波形幅值譜實現最大程度降低。圖8所示為理想脈寬調制波形(零階)、梯形波(一階)和高斯“S”形開關波形(無窮階)的幅值譜(開關頻率為10kHz,占空比為0.5,值域為[0, 1],一階和無窮階開關波形的r和f皆為400ns,高斯窗的標準差為窗口長度的1/8)。實際工程應用中,經常只有部分頻段的信號不滿足電磁兼容標準,文獻[131]提出一種通過修改局部暫態軌跡斜率來抑制特定頻段傳導干擾的 方法。

圖8 零階、一階和無窮階開關波形的幅值譜及其包絡

為實現特定暫態軌跡,需要設計有源門極驅動控制策略。文獻[132]提出一種閉環控制策略,使實際開關電壓跟隨參考開關電壓,參考開關電壓中增加了通態電阻補償項,于是功率開關器件可以工作在不同的負載電流條件下。文獻[133]設計一種特殊的參考波形,通過比較實際開關電壓和該參考波形來輸出控制信號,該控制策略具有抑制電壓過沖和減小開關延遲的作用,同時實驗結果說明它能夠有效抑制高頻電磁干擾。文獻[134]提出基于迭代學習算法的數字閉環控制,用檢測的開關電壓生成驅動電流,有效抑制了電磁干擾噪聲,但也增加了控制復雜性和實現難度,且無法應對突發電路故障。

暫態軌跡控制為實現對高頻電磁干擾特性的精細化控制提供了額外選擇。當前,暫態軌跡控制技術仍有較大的發展空間,暫態軌跡和門極驅動器的設計仍是其研究重點。

6 問題探討和技術展望

電力電子技術仍在快速發展,開關變換器傳導干擾問題日趨復雜,其抑制技術在很多方面仍有待研究和發展。下面就主要問題進行探討并給出相關技術展望。

(1)綜合考慮開關變換器傳導干擾問題。開關變換器傳導干擾問題的解決是個系統性工程,即其抑制技術不是孤立的,測量、建模、仿真和分析方法都是深入理解、研究和應用其抑制技術的重要 基礎。

(2)自動化設計電磁干擾濾波器。開關變換器傳導干擾抑制策略眾多,但是目前濾波仍是最有效的工程解決方案,因此電磁干擾濾波器的設計和優化仍是研究重點。由于開關變換器的開關器件、電路拓撲、工作負載、電路板設計等存在差異,傳統電磁干擾濾波器設計的通用性較差,而借助計算機輔助技術及先進算法進行自動設計,則能夠簡化設計成本,因而應成為重要研究方向[41]。

(3)結合濾波和削減干擾源傳導發射的策略。在干擾源處抑制傳導干擾的策略更加靈活,能夠抑制給定頻率范圍的諧波或噪聲。將這類策略與濾波相結合,能減小電磁干擾濾波器的體積或質量,并提高開關變換器的功率密度[135-137]。

(4)開關變換器其他性能的評估。很多策略以降低開關變換器傳導干擾為唯一目的,這很可能會損害功率變換系統的其他性能,如功率密度、開關損耗、電流紋波、電機轉矩脈動等,包含電磁干擾抑制能力的特定目標優化控制策略應成為重要研究方向[79-81]。

(5)應用場景和工作條件的要求。開關變換器用途日益廣泛,如并網變換器、軌道交通牽引變流器、電動汽車牽引逆變器、航空航天開關電源等,由于它們所在電力電子系統的物理和電磁環境不同,除電磁兼容性外,其物理結構、可靠性、電壓/電流等級、電能質量等要求也往往不同,電磁干擾抑制策略必須充分考慮這些要求[3-5]。

(6)大功率、模塊化開關變換器的電磁干擾。隨著智能電網/電能路由器的發展,大功率、模塊化的并網變換器成為研究熱點,該類變換器開關器件眾多、拓撲結構復雜,電磁干擾問題也更加嚴重,當前針對該問題的研究尚處于初級階段[32]。

(7)寬禁帶基開關變換器的電磁干擾。隨著寬禁帶半導體的應用,開關變換器的開關頻率明顯提高、開關波形振蕩問題明顯加重,這導致開關變換器的傳導和輻射干擾問題更加嚴重,對寬禁帶半導體器件特性、封裝設計的研究應成為重 點[16, 31, 87, 99-101]。

(8)開關變換器內部弱電電路的電磁干擾。傳統的抑制策略主要作用于開關變換器對外部電路的傳導干擾,而非對內部控制、驅動、采樣電路的傳導干擾[138-139],后者應成為重要研究方向。

7 結論

開關變換器傳導干擾抑制策略主要包括濾波、電橋平衡、反相補償、改進脈寬調制、改進功率器件/模塊封裝、優化電路板設計、改善開關過程等。這些策略分為兩大類:一類用于傳導干擾耦合路徑;一類用于傳導干擾源。前者更加有效,但明顯增加了系統的體積或質量;后者更加靈活,但控制和設計更加復雜。隨著開關變換器的應用,其傳導干擾抑制技術在很多方面仍有待研究和發展。

[1] Trzynadlowski A M. Power electronic converters and systems: frontiers and applications[M]. London: The Institution of Engineering and Technology, 2016.

[2] Baliga B J. The IGBT device: physics, design and applications of the insulated gate bipolar transistor[M]. Oxford: William Andrew, 2015.

[3] Smolenski R. Conducted electromagnetic interference (EMI) in smart grids[M]. London: Springer, 2012.

[4] Luszcz J. High frequency conducted emission in AC motor drives fed by frequency converters: sources and propagation paths[M]. Hoboken, NJ: John Wiley & Sons, 2018.

[5] Ogunsola A, Mariscotti A. Electromagnetic com- patibility in railways: analysis and management[M]. Heidelberg: Springer, 2013.

[6] 馬偉明, 張磊, 孟進. 獨立電力系統及其電力電子裝置的電磁兼容[M]. 北京: 科學出版社, 2007.

[7] Paul C R. Introduction to electromagnetic com- patibility[M]. 2nd ed. Hoboken, NJ: John Wiley & Sons, 2006.

[8] Zheng Junqi. Electromagnetic compatibility (EMC) design and test case analysis[M]. Hoboken, NJ: John Wiley & Sons, 2019.

[9] Ott H W. Electromagnetic compatibility engineering[M]. Hoboken, NJ: John Wiley & Sons, 2009.

[10] Costa F, Gautier C, Labouré E, et al. Electromagnetic compatibility in power electronics[M]. Hoboken, NJ: John Wiley & Sons, 2014.

[11] Fang Zhihao, Jiang Dong, Zhang Yechi. Study of the characteristics and suppression of EMI of inverter with SiC and Si devices[J]. Chinese Journal of Electrical Engineering, 2018, 4(3): 37-46.

[12] Mainali K, Oruganti R. Conducted EMI mitigation techniques for switch-mode power converters: a survey[J]. IEEE Transactions on Power Electronics, 2010, 25(9): 2344-2356.

[13] Natarajan S, Babu T S, Balasubramanian K, et al. A state-of-the-art review on conducted electromagnetic interference in non-isolated DC to DC converters[J]. IEEE Access, 2020, 8: 2564-2577.

[14] Yazdani M R, Farzanehfard H, Faiz J. Classification and comparison of EMI mitigation techniques in switching power converters-a review[J]. Journal of Power Electronics, 2011, 11(5): 767-777.

[15] Li Hong, Li Zhong, Zhang Bo, et al. Suppressing electromagnetic interference in direct current con- verters[J]. IEEE Circuits and Systems Magazine, 2009, 9(4): 10-28.

[16] Zhang Boyi, Wang Shuo. A survey of EMI research in power electronics systems with wide bandgap semiconductor devices[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 626-643.

[17] Gamoudi R, Chariag D E, Sbita L. A review of spread-spectrum-based PWM techniques-a novel fast digital implementation[J]. IEEE Transactions on Power Electronics, 2018, 33(12): 10292-10307.

[18] 錢照明, 陳恒林. 電力電子裝置電磁兼容研究最新進展[J]. 電工技術學報, 2007, 22(7): 1-11.

Qian Zhaoming, Chen Henglin. State of art of electromagnetic compatibility research on power electronic equipment[J]. Transactions of China Elec- trotechnical Society, 2007, 22(7): 1-11.

[19] 張逸成, 葉尚斌, 張佳佳, 等. 電力電子設備傳導噪聲抑制措施研究綜述[J]. 電工技術學報, 2017, 32(14): 77-86.

Zhang Yicheng, Ye Shangbin, Zhang Jiajia, et al. Review of conducted noise suppression method for power electronic and electrical equipment[J]. Transa- ctions of China Electrotechnical Society, 2017, 32(14): 77-86.

[20] Narayanasamy B, Luo Fang. A survey of active EMI filters for conducted EMI noise reduction in power electronic converters[J]. IEEE Transactions on Elec- tromagnetic Compatibility, 2019, 61(6): 2040-2049.

[21] 江師齊, 劉藝濤, 銀杉, 等. 基于噪聲源阻抗提取的單相逆變器電磁干擾濾波器的設計[J]. 電工技術學報, 2019, 34(17): 3552-3562.

Jiang Shiqi, Liu Yitao, Yin Shan, et al. Electro- magnetic interference filter design of single-phase inverter based on the noise source impedance extraction[J]. Transactions of China Electrotechnical Society, 2019, 34(17): 3552-3562.

[22] Tarateeraseth V, Hu Bo, See K Y, et al. Accurate extraction of noise source impedance of an SMPS under operating conditions[J]. IEEE Transactions on Power Electronics, 2010, 25(1): 111-117.

[23] Zhou Mengxia, Zhao Yang, Yan Wei, et al. Investi- gation on conducted EMI noise source impedance extraction for electro magnetic compatibility based on SP-GA algorithm[J]. IET Power Electronics, 2019, 12(7): 1792-1799.

[24] Zheng Feng, Wang Wugang, Zhao Xiaofan, et al. Identifying electromagnetic noise-source impedance using hybrid of measurement and calculation method[J]. IEEE Transactions on Power Electronics, 2019, 34(10): 9609-9618.

[25] Tarateeraseth V, See K Y, Canavero F G, et al. Systematic electromagnetic interference filter design based on information from in-circuit impedance measurements[J]. IEEE Transactions on Electro- magnetic Compatibility, 2010, 52(3): 588-598.

[26] Ala G, Giaconia G C, Giglia G, et al. Design and performance evaluation of a high power-density EMI filter for PWM inverter-fed induction-motor drives[J]. IEEE Transactions on Industry Applications, 2016, 52(3): 2397-2404.

[27] 賈圣鈺, 趙爭鳴, 施博辰, 等. 電力電子系統電磁干擾數值建模分析[J]. 電工技術學報, 2021, 36(11): 2383-2393, 2423.

Jia Shengyu, Zhao Zhengming, Shi Bochen, et al. Numerical modeling and analysis of electromagnetic interference in power electronics systems[J]. Transa- ctions of China Electrotechnical Society, 2021, 36(11): 2383-2393, 2423.

[28] Xiang Yangxiao, Pei Xuejun, Zhou Wu, et al. A fast and precise method for modeling EMI source in two-level three-phase converter[J]. IEEE Transactions on Power Electronics, 2019, 34(11): 10650-10664.

[29] Ohn S, Yu Jianghui, Rankin P, et al. Three-terminal common-mode EMI model for EMI generation, propagation, and mitigation in a full-SiC three-phase UPS module[J]. IEEE Transactions on Power Elec- tronics, 2019, 34(9): 8599-8612.

[30] Wang Jianing, Liu Xiaohui, Xun Yuanwu, et al. Common mode noise reduction of three-level active neutral point clamped inverters with uncertain parasitic capacitance of photovoltaic panels[J]. IEEE Transactions on Power Electronics, 2020, 35(7): 6974-6988.

[31] 段卓琳, 張棟, 范濤. SiC電機驅動系統傳導電磁干擾建模及預測[J]. 電工技術學報, 2020, 35(22): 4726-4738.

Duan Zhuolin, Zhang Dong, Fan Tao. Modeling and prediction of electromagnetic interference in SiC motor drive systems[J]. Transactions of China Electrotechnical Society, 2020, 35(22): 4726-4738.

[32] Zhu Ruimin, Lin Ning, Dinavahi V, et al. An accurate and fast method for conducted EMI modeling and simulation of MMC-based HVDC converter station[J]. IEEE Transactions on Power Electronics, 2020, 35(5): 4689-4702.

[33] 高璐, 徐策, 董光, 等. 基于電磁仿真軟件的平面變壓器共模電磁干擾建模方法及其應用[J]. 電工技術學報, 2020, 35(24): 5057-5063.

Gao Lu, Xu Ce, Dong Guang, et al. Common mode electro-magnetic interference modeling method of planar transformers based on CST software and its application[J]. Transactions of China Electrotechnical Society, 2020, 35(24): 5057-5063.

[34] Mantooth H A, Peng Kang, Santi E, et al. Modeling of wide bandgap power semiconductor devices-part I[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 423-433.

[35] Santi E, Peng Kang, Mantooth H A, et al. Modeling of wide-bandgap power semiconductor devices-part II[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 434-442.

[36] 黃華震, 仝涵, 王寧燕, 等. 考慮寄生振蕩的IGBT分段暫態模型對電磁干擾預測的影響分析[J]. 電工技術學報, 2021, 36(12): 2434-2445.

Huang Huazhen, Tong Han, Wang Ningyan, et al. Analysis of the influence of IGBT segmented transient model with parasitic oscillation on electro- magnetic interference prediction[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2434- 2445.

[37] Jiang Shiqi, Liu Yitao, Mei Zhaozhao, et al. A magnetic integrated LCL-EMI filter for a single-phase SiC-MOSFET grid-connected inverter[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 601-617.

[38] Chen Henglin, Ye Shize. Modeling and optimization of EMI filter by using artificial neural network[J]. IEEE Transactions on Electromagnetic Compatibility, 2019, 61(6): 1979-1987.

[39] Ozenbaugh R L, Pullen T M. EMI filter design[M]. 3rd ed. Boca Raton, FL: CRC Press, 2017.

[40] Tarateeraseth V. EMI filter design: part III: selection of filter topology for optimal performance[J]. IEEE Electromagnetic Compatibility Magazine, 2012, 1(2): 60-73.

[41] Viani F, Robol F, Salucci M, et al. Automatic EMI filter design through particle swarm optimization[J]. IEEE Transactions on Electromagnetic Compatibility, 2017, 59(4): 1079-1094.

[42] Zhang Xinmin, Khodabandeh M, Amirabadi M, et al. A simulation-based multifunctional differential mode and common mode filter design method for universal converters[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 658-672.

[43] Wang Shuo, Lee F C, van Wyk J D. A study of integration of parasitic cancellation techniques for EMI filter design with discrete components[J]. IEEE transactions on Power Electronics, 2008, 23(6): 3094-3102.

[44] Yang Ming, Lyu Zekai, Xu Donglin, et al. Resonance suppression and EMI reduction of GaN-based motor drive with sine wave filter[J]. IEEE Transactions on Industry Applications, 2020, 56(3): 2741-2751.

[45] Xing Lei, Sun Jian. Optimal damping of multistage EMI filters[J]. IEEE Transactions on Power Electro- nics, 2012, 27(3): 1220-1227.

[46] Levron Y, Kim H, Erickson R W. Design of EMI filters having low harmonic distortion in high-power- factor converters[J]. IEEE Transactions on Power Electronics, 2014, 29(7): 3403-3413.

[47] Chen Wenjie, Zhang Weiping, Yang Xu, et al. An experimental study of common- and differential-mode active EMI filter compensation characteristics[J]. IEEE Transactions on Electromagnetic Compatibility, 2009, 51(3): 683-691.

[48] Wang Shuo, Maillet Y Y, Wang Fei, et al. Investi- gation of hybrid EMI filters for common-mode EMI suppression in a motor drive system[J]. IEEE Transactions on Power Electronics, 2010, 25(4): 1034-1045.

[49] Goswami R, Wang Shuo. Investigation and modeling of combined feedforward and feedback control schemes to improve the performance of differential mode active EMI filters in AC-DC power con- verters[J]. IEEE Transactions on Industrial Elec- tronics, 2019, 66(8): 6538-6548.

[50] Shin D, Jeong S, Baek Y, et al. A balanced feed- forward current-sense current-compensation active EMI filter for common-mode noise reduction[J]. IEEE Transactions on Electromagnetic Compatibility, 2020, 62(2): 386-397.

[51] Chu Yongbin, Wang Shuo, Wang Qinghai. Modeling and stability analysis of active/hybrid common-mode EMI filters for DC/DC power converters[J]. IEEE Transactions on Power Electronics, 2016, 31(9): 6254-6263.

[52] Ji Junping, Chen Wenjie, Yang Xu, et al. Delay and decoupling analysis of a digital active EMI filter used in arc welding inverter[J]. IEEE Transactions on Power Electronics, 2018, 33(8): 6710-6722.

[53] Hamza D, Qiu Mei. Digital active EMI control technique for switch mode power converters[J]. IEEE Transactions on Electromagnetic Compatibility, 2013, 55(1): 81-88.

[54] Shoyama M, Ohba M, Ninomiya T. Balanced Buck- Boost switching converter to reduce commom-mode conducted noise[J]. Journal of Power Electronics, 2002, 2(2): 139-145.

[55] Wang Shuo, Kong Pengju, Lee F C. Common mode noise reduction for Boost converters using general balance technique[J]. IEEE transactions on power electronics, 2007, 22(4): 1410-1416.

[56] Cochrane D, Chen D Y, Boroyevic D. Passive cancellation of common-mode noise in power electronic circuits[J]. IEEE Transactions on Power Electronics, 2003, 18(3): 756-763.

[57] Wang Shuo, Lee F C. Analysis and applications of parasitic capacitance cancellation techniques for EMI suppression[J]. IEEE Transactions on Industrial Electronics, 2010, 57(9): 3109-3117.

[58] Xie Lihong, Ruan Xinbo, Zhu Haonan, et al. Common-mode voltage cancellation for reducing the common-mode noise in DC-DC converters[J]. IEEE Transactions on Industrial Electronics, 2021, 68(5): 3887-3897.

[59] Monmasson Eric. Power electronic converters: PWM strategies and current control techniques[M]. Hoboken, NJ: John Wiley & Sons, 2011.

[60] Carson J R. Notes on the theory of modulation[J]. Proceedings of the Institute of Radio Engineers, 1922, 10(1): 57-64.

[61] Pareschi F, Rovatti R, Setti G. EMI reduction via spread spectrum in DC/DC converters: state of the art, optimization, and tradeoffs[J]. IEEE Access, 2015, 3: 2857-2874.

[62] Chen Jianan, Jiang Dong, Sun Wei, et al. A family of spread-spectrum modulation schemes based on distribution characteristics to reduce conducted EMI for power electronics converters[J]. IEEE Transa- ctions on Industry Applications, 2020, 56(5): 5142- 5157.

[63] Dahidah M S A, Konstantinou G, Agelidis V G. A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications[J]. IEEE Transactions on Power Electronics, 2015, 30(8): 4091-4106.

[64] Amjad A M, Salam Z. A review of soft computing methods for harmonics elimination PWM for inverters in renewable energy conversion systems[J]. Rene- wable and Sustainable Energy Reviews, 2014, 33: 141-153.

[65] Xin Yayun, Yi Jin, Zhang Kai, et al. Offline selective harmonic elimination with (2+1) output voltage levels in modular multilevel converter using a differential harmony search algorithm[J]. IEEE Access, 2020, 8: 121596-121610.

[66] Etesami M H, Farokhnia N, Fathi S H. Colonial competitive algorithm development toward harmonic minimization in multilevel inverters[J]. IEEE Transactions on Industrial Informatics, 2015, 11(2): 459-466.

[67] Srndovic M, Zhetessov A, Alizadeh T, et al. Simultaneous selective harmonic elimination and THD minimization for a single-phase multilevel inverter with staircase modulation[J]. IEEE Transa- ctions on Industry Applications, 2018, 54(2): 1532- 1541.

[68] Moeini A, Dabbaghjamanesh M, Kimball J W, et al. Artificial neural networks for asymmetric selective harmonic current mitigation-PWM in active power filters to meet power quality standards[J/OL]. IEEE Transactions on Industry Applications, 1: 9[2020-07-07]. https://doi.org/10.1109/TIA.2020.3007596.

[69] Etesami M H, Vilathgamuwa D M, Ghasemi N, et al. Enhanced metaheuristic methods for selective harmonic elimination technique[J]. IEEE Transactions on Industrial Informatics, 2018, 14(12): 5210-5220.

[70] Chen Henglin, Zhao Huan. Review on pulse-width modulation strategies for common-mode voltage reduction in three-phase voltage-source inverters[J]. IET Power Electronics, 2016, 9(14): 2611-2620.

[71] Hava A M, ün E. Performance analysis of reduced common-mode voltage PWM methods and com- parison with standard PWM methods for three-phase voltage-source inverters[J]. IEEE Transactions on Power Electronics, 2009, 24(1): 241-252.

[72] Xu Junzhong, Han Jingwen, Wang Yong, et al. High- frequency SiC three-phase VSIs with common-mode voltage reduction and improved performance using novel tri-state PWM method[J]. IEEE Transactions on Power Electronics, 2019, 34(2): 1809-1822.

[73] Peng Hongwu, Yuan Zhao, Zhao Xingchen, et al. Improved space vector modulation for neutral-point balancing control in hybrid-switch-based T-type neutral-point-clamped inverters with loss and common-mode voltage reduction[J]. CPSS Transa- ctions on Power Electronics and Applications, 2019, 4(4): 328-338.

[74] Jiang Dong, Shen Zewei, Wang Fei. Common-mode voltage reduction for paralleled inverters[J]. IEEE Transactions on Power Electronics, 2018, 33(5): 3961-3974.

[75] Xiong Wenjing, Sun Yao, Su Mei, et al. Carrier-based modulation strategies with reduced common-mode voltage for five-phase voltage source inverters[J]. IEEE Transactions on Power Electronics, 2018, 33(3): 2381-2394.

[76] Shen Zewei, Jiang Dong, Liu Zicheng, et al. Common-mode voltage elimination for dual two-level inverter-fed asymmetrical six-phase PMSM[J]. IEEE Transactions on Power Electronics, 2020, 35(4): 3828-3840.

[77] Chee S J, Ko S, Kim H S, et al. Common-mode voltage reduction of three-level four-leg PWM converter[J]. IEEE Transactions on Industry Applications, 2015, 51(5): 4006-4016.

[78] Karugaba S, Muetze A, Ojo O. On the common-mode voltage in multilevel multiphase single-and double- ended diode-clamped voltage-source inverter systems[J]. IEEE Transactions on Industry Applications, 2012, 48(6): 2079-2091.

[79] Wu Xiang, Tan Guojun, Ye Zongbin, et al. Optimized common-mode voltage reduction PWM for three- phase voltage-source inverters[J]. IEEE Transactions on Power Electronics, 2016, 31(4): 2959-2969.

[80] Xing Xiangyang, Chen Hua. A fast-processing predictive control strategy for common mode voltage reduction in parallel three-level inverters[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(1): 316-326.

[81] 蔣棟. 電力電子變換器的先進脈寬調制技術[M]. 北京: 機械工業出版社, 2018.

[82] Hwang Y S, Chen J J, Yang J, et al. A low-EMI continuous-time delta-sigma-modulator Buck converter with transient response eruption techniques[J]. IEEE Transactions on Industrial Electronics, 2020, 67(8): 6854-6863.

[83] Xu Jianping, Wang Jinping. Bifrequency pulse-train control technique for switching DC-DC converters operating in DCM[J]. IEEE Transactions on Industrial Electronics, 2011, 58(8): 3658-3667.

[84] Huang Huazhen, Wu Jialing, Xu Weihua, et al. The influence of driving parameters on conducted EMI for an IGBT module[J]. IEEE Transactions on Electro- magnetic Compatibility, 2020, 62(5): 2285-2293.

[85] B?deker C, Ayerbe E, Kaminski N. Impact of a Kelvin source connection on discrete high power SiC-MOSFETs[J]. Materials Science Forum, 2018, 924: 723-726.

[86] Kim J, Shin D, Sul S K. A damping scheme for switching ringing of full SiC MOSFET by air core PCB circuit[J]. IEEE Transactions on Power Electronics, 2018, 33(6): 4605-4615.

[87] Xie Yue, Chen Cai, Huang Zhizhao, et al. High frequency conducted EMI investigation on packaging and modulation for a SiC-based high frequency converter[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019, 7(3): 1789-1804.

[88] Wang Jianjing, Chung H S, Li R T. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching per- formance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[89] Dalal D N, Christensen N, Jrgensen A B, et al. Impact of power module parasitic capacitances on medium- voltage SiC MOSFETs switching transients[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 298-310.

[90] Li Shengnan, Tolbert L M, Wang Fei, et al. Stray inductance reduction of commutation loop in the P-cell and N-cell-based IGBT phase leg module[J]. IEEE Transactions on Power Electronics, 2014, 29(7): 3616-3624.

[91] Brovont A D, Lemmon A N, New C, et al. Analysis and cancellation of leakage current through power module baseplate capacitance[J]. IEEE Transactions on Power Electronics, 2020, 35(5): 4678-4688.

[92] Wang Miao, Luo Fang, Xu Longya. A double-end sourced wire-bonded multichip SiC MOSFET power module with improved dynamic current sharing[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2017, 5(4): 1828-1836.

[93] Liang Zhenxian, Ning Puqi, Wang Fred, et al. A phase-leg power module packaged with optimized planar interconnections and integrated double-sided cooling[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2014, 2(3): 443-450.

[94] Vagnon E, Jeannin P O, Crebier J C, et al. A bus- bar-like power module based on three-dimensional power-chip-on-chip hybrid integration[J]. IEEE Transactions on Industry Applications, 2010, 46(5): 2046-2055.

[95] Wang Kangping, Wang Laili, Yang Xu, et al. A multiloop method for minimization of parasitic inductance in GaN-based high-frequency DC-DC converter[J]. IEEE Transactions on Power Electronics, 2017, 32(6): 4728-4740.

[96] Reusch D, Strydom J. Understanding the effect of PCB layout on circuit performance in a high- frequency gallium-nitride-based point of load con- verter[J]. IEEE Transactions on Power Electronics, 2014, 29(4): 2008-2015.

[97] Bhargava A, Pommerenke D, Kam K W, et al. DC-DC Buck converter EMI reduction using PCB layout modification[J]. IEEE Transactions on Electro- magnetic Compatibility, 2011, 53(3): 806-813.

[98] DiMarino C M, Mouawad B, Johnson C M, et al. 10kV SiC MOSFET power module with reduced common-mode noise and electric field[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 6050-6060.

[99] Lee H, Smet V, Tummala R. A review of SiC power module packaging technologies: challenges, advances, and emerging issues[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 239-255.

[100] Hou Fengze, Wang Wenbo, Cao Liqiang, et al. Review of packaging schemes for power module[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 223-238.

[101] Chen Cai, Luo Fang, Kang Yong. A review of SiC power module packaging: layout, material system and integration[J]. CPSS Transactions on Power Electro- nics and Applications, 2017, 2(3): 170-186.

[102] Archambeault B R, Drewniak J. PCB design for real-world EMI control[M]. New York: Springer, 2013.

[103] Montrose M I. EMC and the printed circuit board: design, theory, and layout made simple[M]. New York: IEEE Press, 1999.

[104] Chen Cai, Pei Xuejun, Chen Yu, et al. Investigation, evaluation, and optimization of stray inductance in laminated busbar[J]. IEEE Transactions on power electronics, 2014, 29(7): 3679-3693.

[105] Caponet M C, Profumo F, De Doncker R W, et al. Low stray inductance bus bar design and construction for good EMC performance in power electronic circuits[J]. IEEE Transactions on Power Electronics, 2002, 17(2): 225-231.

[106] 朱俊杰, 原景鑫, 聶子玲, 等. 基于全碳化硅功率組件的疊層母排優化設計研究[J]. 中國電機工程學報, 2019, 39(21): 6383-6394.

Zhu Junjie, Yuan Jingxin, Nie Ziling, et al. Optimum design of planer busbar based on all-silicon carbide power module[J]. Proceedings of the CSEE, 2019, 39(21): 6383-6394.

[107] 阮杰, 劉暢, 李廣卓. 適用于器件并聯型ANPC拓撲的低感疊層母排設計方法[J]. 高電壓技術, 2019, 45(7): 2093-2100.

Ruan Jie, Liu Chang, Li Guangzhuo. Design method of low-inductance laminated busbar for device- parallel ANPC circuit[J]. High Voltage Engineering, 2019, 45(7): 2093-2100.

[108] Grobler I, Gitau M N. Analysis, modelling and measurement of the effects of aluminium and polymer heatsinks on conducted electromagnetic compatibility in DC-DC converters[J]. IET Science, Measurement & Technology, 2017, 11(4): 414-422.

[109] Gong Xun, Josifovi? I, Ferreira J A. Modeling and reduction of conducted EMI of inverters with SiC JFETs on insulated metal substrate[J]. IEEE Transa- ctions on Power Electronics, 2013, 28(7): 3138-3146.

[110] Gong Xun, Ferreira J A. Investigation of conducted EMI in SiC JFET inverters using separated heat sinks[J]. IEEE Transactions on Industrial Electronics, 2014, 61(1): 115-125.

[111] Oswald N, Anthony P, McNeill N, et al. An experimental investigation of the tradeoff between switching losses and EMI generation with hard- switched all-Si, Si-SiC, and all-SiC device com- binations[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2393-2407.

[112] García-Caraveo A, Soto á, González R, et al. Brief review on snubber circuits[C]//2010 20th Inter- national Conference on Electronics Communications and Computers (CONIELECOMP), Cholula, Puebla, Mexico, 2010: 271-275.

[113] Batarseh I, Harb A. Soft-switching DC-DC con- verters[M]//Cham: Springer, Power Electronics: Circuit Analysis and Design. 2nd ed. 2018: 347-460.

[114] Rashid M H, Hui S Y R, Chung H S H. Resonant and soft-switching converters[M]//Oxford: Butterworth- Heinemann, Rashid M H. Power Electronics Handbook. 4th ed. 2018: 339-383.

[115] Yano Y, Kawata N, Iokibe K, et al. A method for optimally designing snubber circuits for Buck converter circuits to damp LC resonance[J]. IEEE Transactions on Electromagnetic Compatibility, 2019, 61(4): 1217-1225.

[116] Mohammadi M, Adib E, Yazdani M R. Family of soft-switching single-switch PWM converters with lossless passive snubber[J]. IEEE Transactions on Industrial Electronics, 2015, 62(6): 3473-3481.

[117] Mohammadi M R, Peyman H, Yazdani M R, et al. A ZVT bidirectional converter with coupled-filter- inductor and elimination of input current notches[J]. IEEE Transactions on Industrial Electronics, 2020, 67(9): 7461-7469.

[118] Charalambous A, Yuan Xibo, McNeill N. High- frequency EMI attenuation at source with the auxiliary commutated pole inverter[J]. IEEE Transa- ctions on Power Electronics, 2018, 33(7): 5660- 5676.

[119] Zhao Shuang, Zhao Xingchen, Dearien A, et al. An intelligent versatile model-based trajectory-optimized active gate driver for silicon carbide devices[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 429-441.

[120] Obara H, Wada K, Miyazaki K, et al. Active gate control in half-bridge inverters using programmable gate driver ICs to improve both surge voltage and converter efficiency[J]. IEEE Transactions on Industry Applications, 2018, 54(5): 4603-4611.

[121] Wang Rui, Liang Lin, Chen Yu, et al. Self-adaptive active gate driver for IGBT switching performance optimization based on status monitoring[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 6362-6372.

[122] Jiang Yanfeng, Feng Chao, Yang Zhichang, et al. A new active gate driver for MOSFET to suppress turn- off spike and oscillation[J]. Chinese Journal of Electrical Engineering, 2018, 4(2): 43-49.

[123] Shu Lu, Zhang Junming, Peng Fangzheng, et al. Active current source IGBT gate drive with closed- loop d/dand d/dcontrol[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3787-3796.

[124] Lobsiger Y, Kolar J W. Closed-loop d/dand d/dIGBT gate driver[J]. IEEE Transactions on Power Electronics, 2015, 30(6): 3402-3417.

[125] Camacho A P, Sala V, Ghorbani H, et al. A novel active gate driver for improving SiC MOSFET switching trajectory[J]. IEEE Transactions on Indu- strial Electronics, 2017, 64(11): 9032-9042.

[126] Dymond H C P, Wang Jianjing, Liu Dawei, et al. A 6.7GHz active gate driver for GaN FETs to combat overshoot, ringing, and EMI[J]. IEEE Transactions on Power Electronics, 2018, 33(1): 581-594.

[127] Zhao Shuang, Zhao Xingchen, Wei Yuqi, et al. A review on switching slew rate control for silicon carbide devices using active gate drivers[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 4096-4114.

[128] 王寧, 張建忠. 基于開關軌跡優化的SiC MOSFET有源驅動電路研究綜述[J/OL]. 電工技術學報: 1-15[2022-01-26]. DOI: 10.19595/j.cnki.1000-6753.tces. 210560.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J/OL]. Transactions of China Electro- technical Society: 1-15[2022-01-26]. DOI: 10.19595/j. cnki.1000-6753.tces.210560.

[129] Oswald N, Stark B H, Holliday D, et al. Analysis of shaped pulse transitions in power electronic switching waveforms for reduced EMI generation[J]. IEEE Transactions on Industry Applications, 2011, 47(5): 2154-2165.

[130] Patin N, Vi?als M L. Toward an optimal Heisenberg's closed-loop gate drive for Power MOSFETs[C]// IECON 2012-38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 2012: 828-833.

[131] Mori T, Funato H, Ogasawara S, et al. H-bridge step- down converter applied proposed switching transient waveform modification to reduce specific harmo- nics[C]//2012 International Conference on Renewable Energy Research and Applications (ICRERA), Nagasaki, Japan, 2012: 1-6.

[132] Cui Tongkai, Ma Qishuang, Xu Ping, et al. Analysis and optimization of power MOSFETs shaped switching transients for reduced EMI generation[J]. IEEE Access, 2017, 5: 20440-20448.

[133] Yang Xin, Long Zhiqiang, Wen Yanhui, et al. Investigation of the trade-off between switching losses and EMI generation in Gaussian S-shaping for high-power IGBT switching transients by active voltage control[J]. IET Power Electronics, 2016, 9(9): 1979-1984.

[134] Blank M, Glück T, Kugi A, et al. Digital slew rate and S-shape control for smart power switches to reduce EMI generation[J]. IEEE Transactions on Power Electronics, 2015, 30(9): 5170-5180.

[135] Zhang Yechi, Shen Zewei, Jiang Dong. An integrated EMI filter scheme for paralleled inverter with zero- CM PWM algorithm[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(1): 716-726.

[136] Jayaraman K, Kumar M. Design of passive common- mode attenuation methods for inverter-fed induction motor drive with reduced common-mode voltage PWM technique[J]. IEEE Transactions on Power Electronics, 2020, 35(3): 2861-2870.

[137] Park H P, Jeong S, Kim M, et al. Spread spectrum technique for decreasing EM noise in high-frequency APWM HB resonant converter with reduced EMI filter size[J]. IEEE Transactions on Power Electronics, 2019, 34(11): 10845-10855.

[138] Tian Yidong, Yang Xu, Chen Wenjie. A novel copper layer based field-to-trace coupling model and EMS evaluation method for DSP-based control circuit in MMC-HVDC system[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019, 9(1): 1133-1146.

[139] Nguyen V S, Lefranc P, Crebier J C. Gate driver supply architectures for common mode conducted EMI reduction in series connection of multiple power devices[J]. IEEE Transactions on Power Electronics, 2018, 33(12): 10265-10276.

Review of Conducted Electromagnetic Interference Suppression Strategies for Switching Converters

1121

(1. School of Automation Science and Electrical Engineering Beihang University Beijing 100083 China 2. State Key Lab of Power Systems Department of Electrical Engineering Tsinghua University Beijing 100084 China)

Switching converters are widely applied in economy fields, where the electromagnetic interference (EMI) is becoming increasingly prominent, hence the suppression of EMI in switching converters becomes more essential. A state-of-the-art review of the conducted EMI suppression strategies for switching converters is presented, focusing on their basic principles, research statuses and effectiveness. The reviewed strategies include filtering, balance, compensation, improving pulse width modulation, power device/module packaging, printed circuit board design, improving switching process, etc. These strategies can be classified into two broad categories: blocking the coupling path and reducing the electromagnetic emission from the interference source. Finally, crucial questions and development prospects of conducted EMI suppression technologies for switching converters are discussed.

Switching converters, conducted electromagnetic interference (EMI), EMI suppression, electromagnetic compatibility

10.19595/j.cnki.1000-6753.tces.210094

TM46

何 杰 男,1995年生,碩士研究生,研究方向為SiC器件驅動設計和功率變換器控制。E-mail: hejie_love@buaa.edu.cn

李 曉 男,1990年生,博士,研究方向為模型預測控制、寬禁帶器件的應用、電力電子技術在電力系統中的應用。E-mail: li_xiao@buaa.edu.cn(通信作者)

2021-01-19

2021-09-25

國家自然科學基金(52107175)、北京市科技新星計劃(Z211100002121080)和清華大學電力系統及大型發電設備安全控制和仿真實驗室開放課題(SKLD20M05)資助項目。

(編輯 陳 誠)