基于薄膜IPD 工藝的N77 頻段多零點帶通濾波器設計

王浩威 ,郭 瑜 ,傅肅磊 ,王為標 ,吳浩東

(1.江南大學 物聯網工程學院,江蘇 無錫 214122;2.無錫市好達電子股份有限公司,江蘇 無錫 214124;3.南京大學 物理學院,江蘇 南京 210093)

無源微波器件是微波模塊的重要組成部分,而濾波器作為無源微波器件的關鍵部分,對整個微波收發系統的性能與體積有決定性影響。在3G/4G 時代,基于聲表面波和體聲波原理的聲學濾波器由于其高選擇性、價格低廉、尺寸小等優點在移動終端市場中占主導地位。隨著5G 通訊時代的到來,高頻寬帶濾波器的市場需求迅速上升,而傳統的聲學濾波器受器件壓電材料聲速小、機電耦合系數低的限制,難以滿足需求[1]。目前,基于薄膜IPD 工藝的濾波器因具有高頻、大帶寬、體積小、易于集成等特點[2-4],成為當前研究的熱門方向。

薄膜IPD 工藝具有加工精度高、均一性好等優點,使得濾波器能在滿足帶寬需求的同時極大地縮小尺寸。然而,IPD 器件的膜層通常很薄,并且受半導體襯底的導電性影響,濾波器電感Q值較低,整體損耗較大。因此,許多學者針對如何降低IPD 器件損耗在材料、工藝、電路結構等方面進行了探索。Zuo 等[5]提出將IPD 電路與聲學諧振器相結合,通過使用更少的LC 元件來增大帶寬、降低損耗,但實驗模型過于理想化,并且損耗性能改善不顯著。Wu 等[6]應用高Q值非對稱差分電感和空氣橋增強電容來提升電路性能,但器件制備流程復雜、加工難度大。Chen 等[7-8]采用GaAs 作為襯底材料,器件損耗有所改善,但GaAs IPD 工藝通常采用Au 或Au/Cu 作為金屬材料,工藝成本太高。因此,如何獲得低損耗、低成本的大帶寬薄膜IPD 濾波器,仍是一個亟待解決的問題。

針對上述問題,本文利用PCB 基板中金屬膜較厚、層數多、便于設計高Q值電感的優點,將以往IPD 濾波器的主諧振回路平面螺旋電感改為三維結構電感形式放置在PCB 基板內,大幅提高電感Q值,降低器件損耗。將薄膜IPD 技術與PCB 技術二者優勢相結合,還能減小電路面積,降低器件成本。此外,通過引入外部串聯電路和源負載耦合結構拓寬了通帶帶寬,并產生了三個帶外零點來提升帶外抑制。最終制備了一款工作在N77 頻段的大帶寬、多零點帶通濾波器,并進行了實際測試。

1 理論與設計

1.1 電路結構分析

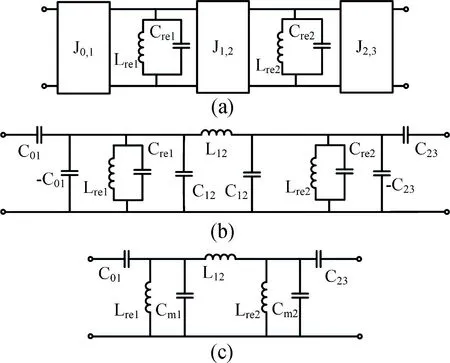

為得到高性能濾波器,本文在二階帶通濾波器電路基礎上進行結構變換,具體變換過程如圖1 所示。圖1(a)為由兩個諧振回路、三個導納逆變器組成的二階帶通濾波器等效電路。根據導納逆變器原理[9],在窄帶近似的情況下,使用電容電感網絡對逆變器進行等效變換,得到圖1(b)所示電路。針對此時出現理論負值電容的情況,可通過相鄰的正值電容并聯消除,得到圖1(c)所示電路。值得注意的是,在窄帶近似的情況下,圖1(a)~(c)電路結構是等效的,圖1(c)等效電路局限于窄帶濾波器。

圖1 帶通濾波器等效電路。(a)采用導納逆變器;(b)使用等效電路替換逆變器;(c)合并并聯電容Fig.1 Equivalent circuit of the bandpass filter.(a) A bandpass filter circuit with admittance inverters;(b) A bandpass filter circuit with admittance inverters replaced by equivalent circuit;(c) A bandpass filter circuit after combining shunt capacitors

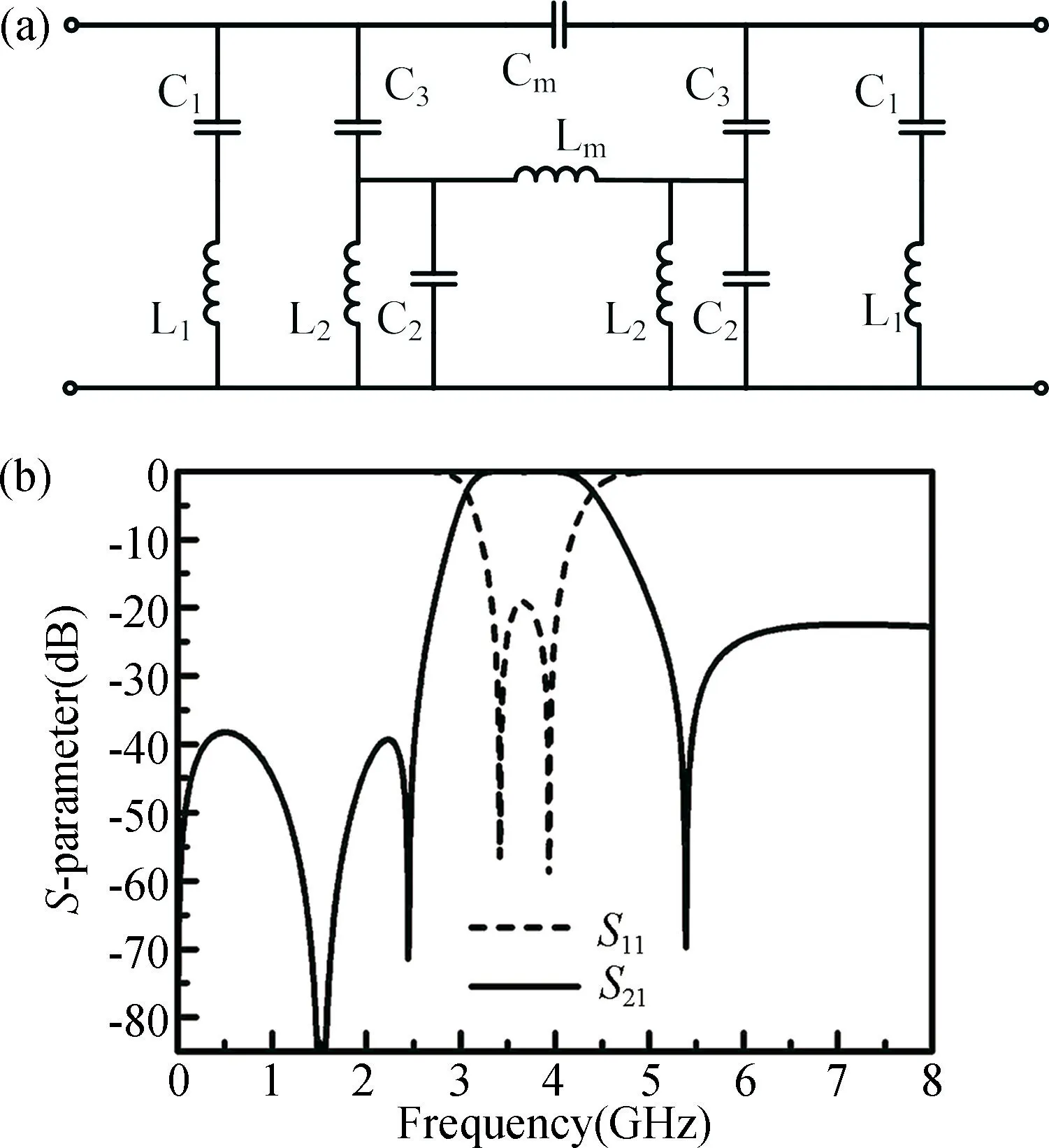

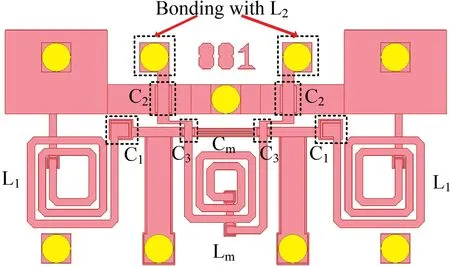

為了實現大帶寬濾波器,本文在電路兩側各級聯一個串聯電路L1和C1,起到拓寬通帶、調節帶內平坦度的作用。同時,級聯串聯電路在通帶左側位置形成了一個傳輸零點。此外,為提高濾波器選擇性,本設計通過引入源負載耦合電容Cm,在通帶兩側各增加了一個傳輸零點。最終帶通濾波器等效電路結構如圖2(a)所示,元件參數如下:L1=2.95 nH,L2=0.47 nH,Lm=1.6 nH,C1=3.7 pF,C2=4.22 pF,C3=0.93 pF,Cm=0.01 pF。計算的電路頻率響應如圖2(b)所示。

圖2 (a) 帶通濾波器原理圖;(b) 頻率響應Fig.2 (a) Schematic of the proposed bandpass filter;(b) Frequency response of the bandpass filter

1.2 高Q 值電感和電容設計

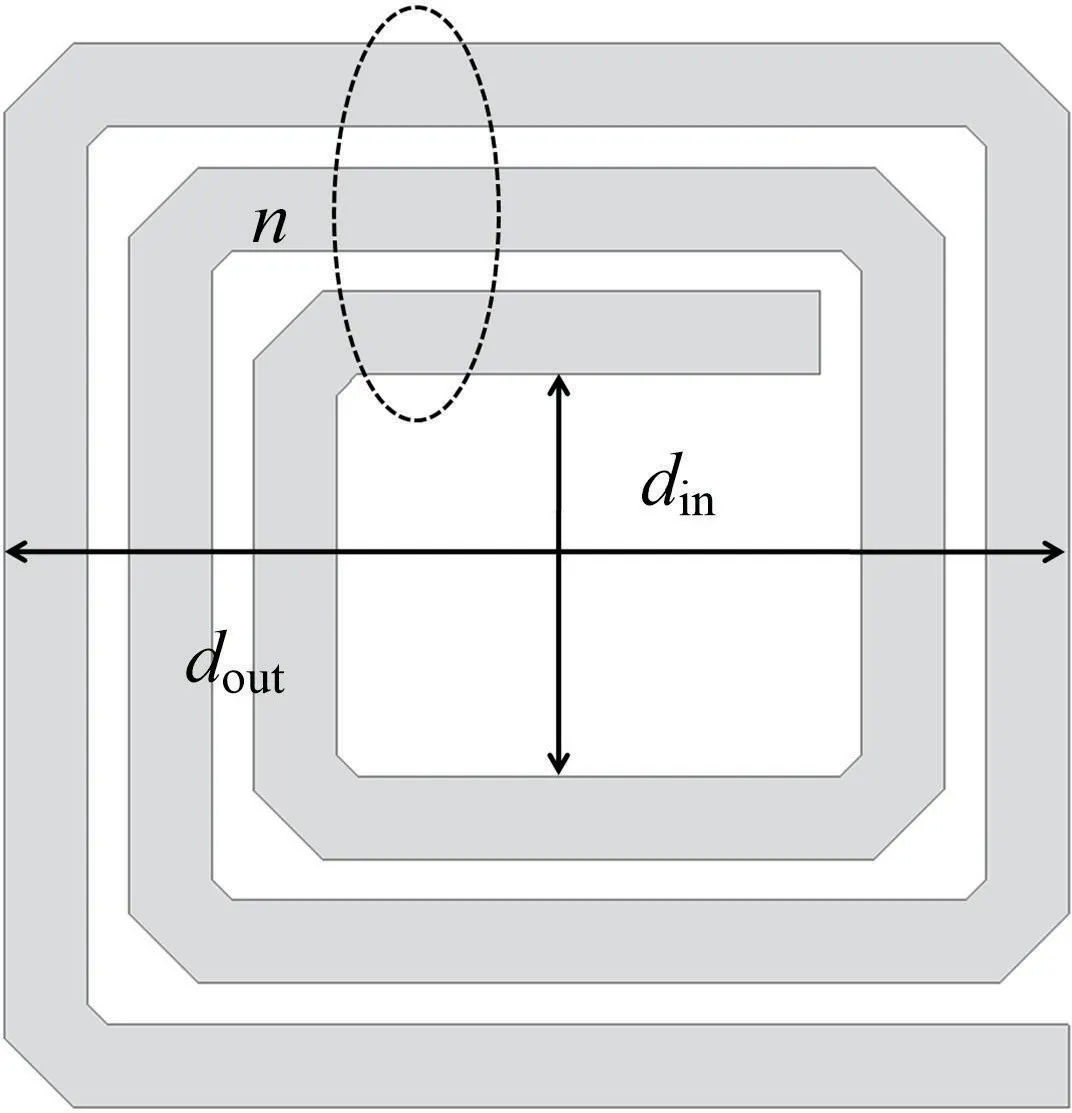

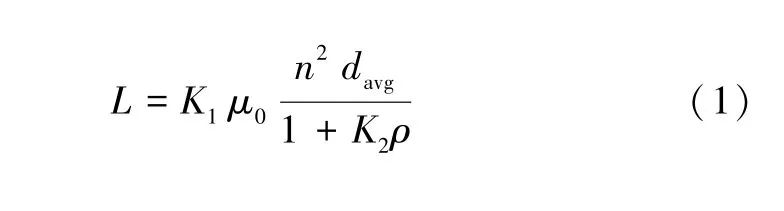

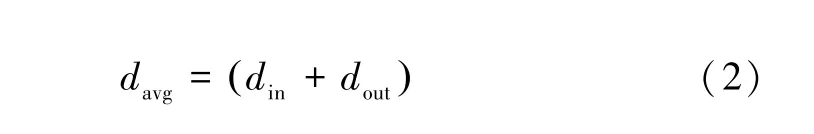

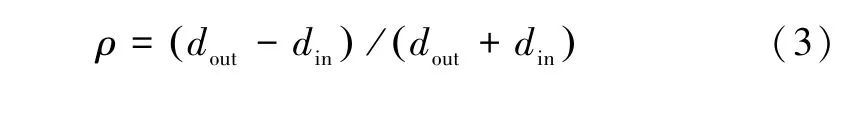

與傳統LC 濾波器不同,IPD 工藝集總濾波器的電感大多為平面螺旋電感,其電感值與其幾何形狀相關,如圖3 所示。對于四邊形平面螺旋電感,可運用下述公式大致計算[10]:

圖3 平面電感結構Fig.3 Structure of the planar inductor

式中:K1和K2為固定系數;n為匝數;ρ為填充率;davg代表的是內徑din和外徑dout的算術平均值。

其中,填充率ρ的計算公式為:

方形電感器的固定系數為K1=2.34 和K2=2.75。平面電感的品質因數一般只能達到30 左右,且自諧振頻率較低。當平面電感作為主諧振電感時,將嚴重影響高頻波段濾波器的帶內特性和帶外抑制。

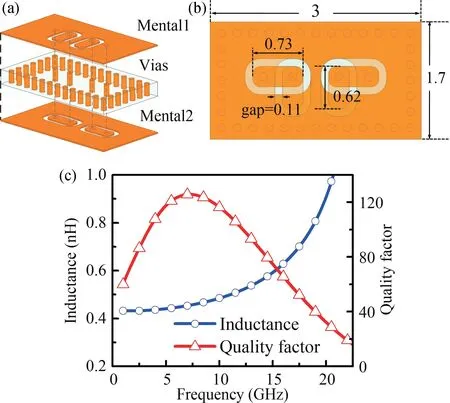

為提升電路損耗性能,本文將主諧振電路的電感與其余電感分開設計。鑒于PCB 基板金屬厚、層數多、成本低,提出將主諧振電感以三維電感的形式設計在基板內,以提高電感Q值。如圖4(a)和圖(b)所示,兩個三維電感同向放置,并在電感四周設置一圈金屬柱,以避免引入板間寄生電容影響濾波器的整體性能。進一步地,腔體式的結構設計能將磁場能量束縛在金屬柱范圍內,也起到屏蔽的作用,避免外部電路帶來不必要的耦合。其余旁路電感以平面電感形式集成在硅基芯片上,硅片阻值為5000 Ω·cm,金屬厚度為4.5 μm,具體電感尺寸可通過公式(1)~(3)進行計算。

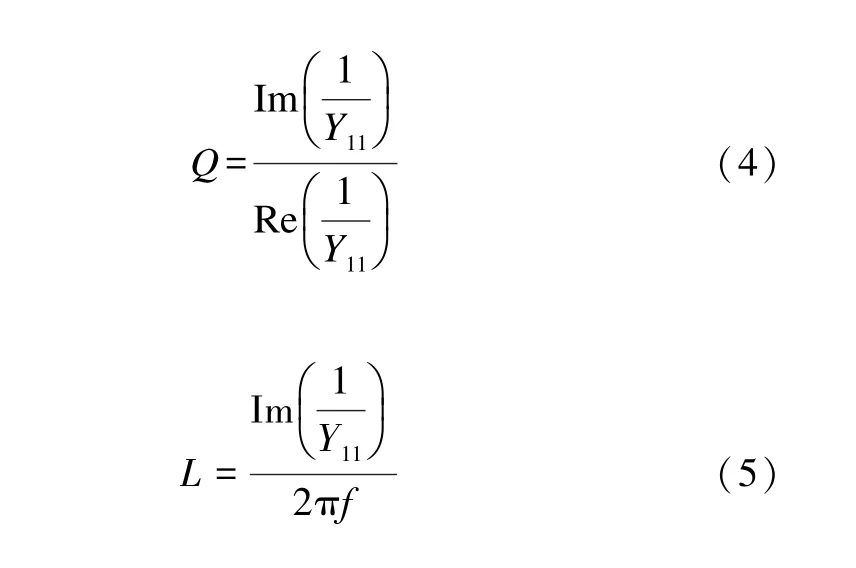

使用電磁仿真軟件進行建模仿真,可以得到準確電感值,電感特性可以通過Y參數計算獲得:

仿真得到的三維電感特性如圖4(c)所示,該電感在3.7 GHz 時Q值大于100,自諧振頻率大于20 GHz,比傳統的平面螺旋電感具有更高的Q值和更寬的頻率使用范圍。

圖4 (a) 電感三維圖;(b) 俯視圖,單位:mm;(c) 電感值與Q 值隨頻率變化曲線Fig.4 (a) 3-D view of inductor;(b) Top view of inductor;(c) Dependence of inductance and quality factor on frequency

使用薄膜IPD 工藝加工薄膜介質,能夠提高單位電容密度,在小區域內滿足電路需求。如使用SiNx作為MIM 電容的介質材料,當介質厚度為0.1 μm 時,單位電容密度可以達到600 pF/mm2,電容Q值高于500。然而,由于介質厚度過薄,MIM 結構難以滿足0.1 pF 量級電容的精度需求。故采用叉指電容的結構進行小電容設計。叉指電容的指條寬度為5 μm,指間間隙為5 μm,金屬厚度為2 μm,可以通過改變指條對數精準控制電容大小。如圖5 所示,電路結構與圖2(a)電路相對應,C1、C2、C01和C23采用MIM 電容結構,Cm采用叉指電容結構。

圖5 濾波器芯片結構Fig.5 Configuration of the proposed filter chip

1.3 基板與芯片的實現與結合

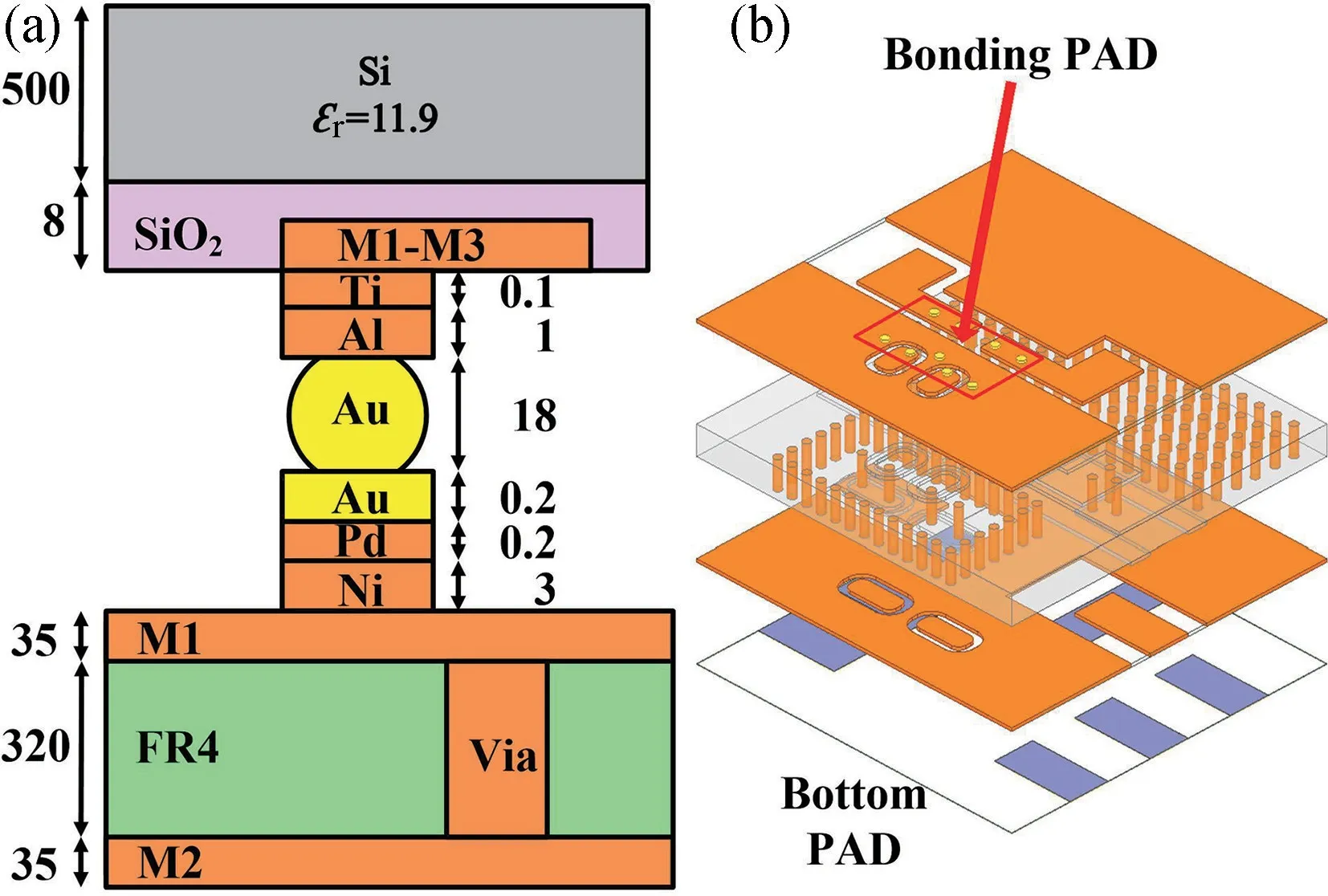

通過金球倒裝工藝將芯片鍵合到基板上。如圖6(a)所示,金球上方為倒置的IPD 芯片,下方為包含高Q值電感和輸入輸出端口的基板。金球上下層鍵合區域的材料為Al 或Au,以保證上下層有足夠的結合力。芯片表面使用Ti/Al 金屬材料,基板表面使用Ni、Pd 和Au 鍍層。

圖6 (a) 鍵合結構剖面圖,單位:μm;(b) 基板整體結構Fig.6 (a) Cross-sectional views of the bonding structure(Unit:μm);(b) Overall structure of the proposed PCB

采用金球倒裝鍵合工藝主要起到三個作用:(1)用于上下層的信號互聯;(2)用于上下兩層的共地;(3)為基板上層的濾波器提供電磁屏蔽,防止其干擾外界以及外界對其產生干擾。輸入輸出端口皆位于下層基板,因此下層基板尺寸大于上層芯片。為方便后續濾波器測試,將電感放置在5 mm×5 mm 的基板內,使用CPW 結構將輸入輸出端引到基板底層,如圖6(b)所示。

2 工藝實現步驟

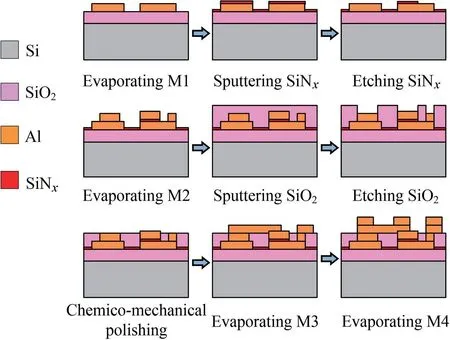

圖7 展示了本文濾波器硅基芯片的加工工藝。采用電阻率為5000 Ω·cm 的高阻硅片作為襯底,以提高平面電感的Q值。首先,在硅襯底上濺射3 μm 厚的SiO2,用于實現硅片與平面螺旋電感的隔離。在SiO2上通過剝離工藝得到厚度為2 μm 的鋁圖案(M1)作為MIM 電容器的下電極板。濺射0.1 μm 厚的SiNx作為電容器介質,并對非電容位置進行光刻開窗。蒸發1 μm 厚的金屬層(M2),部分作為MIM 電容的上極板,其余起到連接柱作用。進行SiO2的濺射,將金屬完全覆蓋在SiO2內,并使用CMP 與刻蝕工藝進行磨平開窗。

圖7 IPD 工藝流程步驟Fig.7 Process flow of IPD technology

通過反濺工藝對M2 開窗位置進行表面處理,去除殘留SiO2等氧化物后,再通過剝離工藝制作一層3 μm 厚的金屬鋁(M3)。最終在M3 層上制作一層1.1 μm 厚的Ti/Al 金屬PAD。后續將金球植在芯片表面,再將芯片倒裝在基板上,使用熱壓超聲的方式將二者鍵合。

3 實驗結果與測量

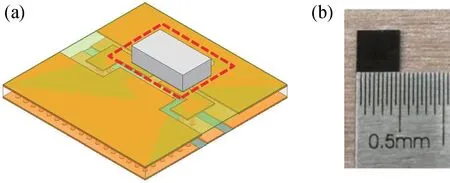

基于上述分析,本文設計了一款N77 頻段的帶通濾波器。為驗證設計方案的準確性,結合IPD 工藝和PCB 工藝加工得到了N77 頻段濾波器。所制作的濾波器整體結構如圖8(a)所示,倒裝完成后通過覆膜將濾波器完全密封,如圖8(b)所示。圖8(a)中紅框所示為該BPF 的實際大小(不包含額外引出的輸入輸出PAD),尺寸為2.2 mm × 3.0 mm,即0.027λ0×0.037λ0,其中λ0為3.7 GHz 的波長。

圖8 (a) 濾波器仿真結構;(b) 濾波器實物圖Fig.8 (a) 3-D view of the proposed filter;(b) Photograph of the fabricated filter

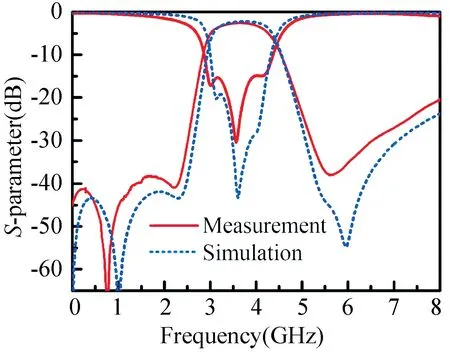

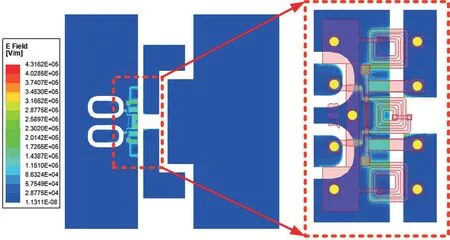

將濾波器元件焊接在評估板(EVB,Evaluation Board)上,使用矢量網絡分析儀(是德科技,E5071C)進行測試,測量結果與仿真結果對比如圖9 所示。實測損耗為-2.58 dB,上阻帶存在兩個零點,帶外抑制大于30 dB,下阻帶存在一個零點,帶外抑制大于20 dB。需要注意的是,測試結果比圖2(b)理想頻率響應多一個傳輸極點,這是由于測試結果中包含了基板和測試板的影響。經仿真探究發現,該額外極點是由基板和芯片間的寄生電容效應導致的。如圖10 所示,基板電場強度最大的區域與芯片輪廓基本吻合,二者間確實存在較強的電容效應。

圖9 濾波器仿真及測試結果Fig.9 Simulated and measured results of the proposed filter

圖10 基板電場分布圖Fig.10 Electric field distribution of PCB

此外,本文使用鋁作為主要金屬材料,后續可以使用導電性更好的金屬材料如銅、金等,以進一步降低歐姆損耗,提升帶內性能。測試結果與仿真結果整體吻合較好,帶外區域存在較小偏差,這是由于EVB板與器件之間存在耦合,并且EVB 板和測試接頭存在一定插損。

表1 展示了本研究濾波器與已有文獻中IPD 濾波器的性能對比。可以發現,本文所設計的濾波器擁有多個零點,且在使用低成本的鋁作為主金屬材料的情況下,器件損耗依然相對較好。

表1 與文獻中現有IPD 工藝濾波器對比Tab.1 Comparisons with some related IPD filters

4 結論

本文將IPD 工藝和PCB 工藝相結合,設計并制備出了一款小尺寸(2.2 mm×3.0 mm)的大帶寬、低損耗、低成本濾波器。基于PCB 基板的成本較低、內置電感Q值較高的特性,最終制備的濾波器最低損耗為-2.58 dB,1 dB 帶寬為918 MHz。相較于其他已有的IPD 電路器件,本文基于低成本的鋁材料器件仍在損耗性能方面占有優勢,證明了該工藝結合的優越性。基于上述優點,本濾波器有望應用于5G/6G 毫米波通信系統中。