一種可改善鍵合絲截止頻率的T形匹配電路

摘? 要:介紹了一種在微波多芯片模塊中,芯片微波端口鍵合絲較長的情況下,如何對其進行頻率拓寬的方法。針對芯片微波端口鍵合絲引入的失配情況進行了分析和準確的模型提取,并以此得出了一個有效的匹配電路結構(T形結)。在鍵合絲長度相同的情況下,此T形匹配方式將成倍提高其使用頻率,改善電路性能。同時,此T形匹配結構簡單,便于設計和應用。

關鍵詞:T形結;鍵合絲;芯片

中圖分類號:TN402? ? ? ? ?文獻標識碼:A文章編號:2096-4706(2022)02-0078-03

Abstract: This paper introduces a method of how to broaden the frequency of microwave multi chip module when the bonding wire of Chip microwave port is long. Aiming at the mismatch situation of introducing the chip microwave port bonding wire, it is analyzed and the accurate model is extracted. According to this, an effective matching circuit structure (T-junction) is obtained. When the length of bonding wire is the same, this T-shaped matching method will multiply its use frequency and improve the circuit performance. At the same time, the T-shaped matching structure is simple and convenient for design and application.

Keywords: T-junction; bonding wire; chip

0? 引? 言

近年來,微波和射頻通信技術、各種雷達等軍用電子系統的飛速發展。對整機系統的集成度提出了很高的要求。多芯片模塊在各種系統中的使用越來越多,這也是目前實現射頻和微波電路小型化的有效途徑。在微組裝工藝中,常常使用鍵合線對多個芯片、芯片與其他元器件之間進行互相連接。其是微組裝中的關鍵工藝技術。鍵合工藝作為多芯片模塊中必不可少的關鍵工藝,以其靈活高效的組裝方式被大量運用,但鍵合絲的缺點也越來越凸顯,尤其對于較高的頻率的系統而言,其電感量(鍵合絲越長電感量越大,反之越小)已不能忽略,這將嚴重影響芯片的應用;當微波頻率較高時,傳統做法常常是采用減小芯片與連接微帶線間的間隙(通常為0.075 mm~0.15 mm之間)來減小鍵合絲的長度,從而達到減小鍵合絲電感效應的目的[1,2]。但這無形中帶來了以下三方面的問題:(1)過小的間隙造成工藝組裝困難,嚴重影響裝配效率;(2)影響鍵合效率,芯片最易鍵合距離大于0.3 mm,過小的器件間隙將使得鍵合變得困難;(3)芯片和連接的微帶線間隙過小,容易造成短路,因而影響了電路可靠性。

為了在解決以上幾方面問題的同時又不影響電路性能,這里將介紹一種針對多芯片模塊中,芯片微波端口鍵合絲的匹配方法,在鍵合絲長度相同的情況下,此匹配方法將大大提高電路的截止頻率,并改善電路性能,同時在設計中可以在工藝容許的條件下,將鍵合絲的長度適當加長以達到工藝最優長度,這樣可以大大提高由多種芯片組成的組件產品的可生產性,提高生產效率。

1? 模型提取與原理分析

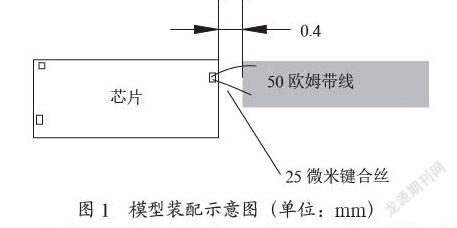

這里以芯片與50歐姆微帶線間的間隙為0.4 mm,鍵合直徑為25微米金絲為例,來進行分析,圖1為模型裝配示意圖。同時為了分析方便,這里假設芯片端口為50歐姆。

因鍵合絲具有電感效應,因此,圖1中芯片端口直徑25微米兩根金絲可等效為一個電感。由此,圖1可以等效為一個電感串聯在兩個50歐姆端口上(假設芯片端口為50歐姆)。

我們假設選取圓柱形鍵合線,其直徑為d、長度為L,根據經典理論,這段鍵合線的串聯電阻R與串聯電感L可分別通過下面的式(1)和式(2)表示:

式中各參數的代表意義如下:其中δ為損耗因數;μr為金絲材料鍵合線的相對磁導率,如果是金絲材料的鍵合線,此值應為1;μ0為空氣的磁導率;ds和ρ分別為金絲材料鍵合線的趨膚深度和電阻率。

為了得到鍵合金絲的長度,模擬實際的鍵合高度與芯片間距,制作了鍵合夾具,在同等工藝條件下鍵合多次后,取下鍵合金絲在帶有測距功能的高倍顯微鏡下進行長度測量。最終得到間隙為0.4 mm時,鍵合金絲的長度大約為0.75 mm,帶入相應的參數進行計算,可得出單根鍵合金絲的電感量約為0.76 nH,進而將此帶入到具有互感仿真功能的軟件進行仿真,最終得出圖1中兩根直徑25微米金絲其電感量大約為0.35 nH。圖2為對其等效模型進行理論仿真結果,由仿真結果可知,當頻率大于5 GHz時,S11與S22大于-20 dB;當頻率大于10 GHz時,S11與S22大于-10 dB,即當頻率越高駐波越差。此電感效應,在實際電路中將嚴重影響微波電路頻率高端的特性。因此,將頻率拓寬變得非常有必要。

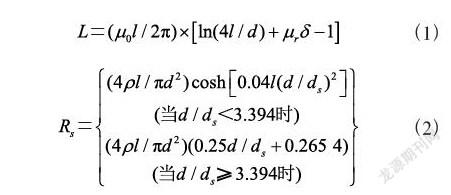

在不改變金絲長度的情況下,為了拓寬其使用頻率,必須對其進行阻抗匹配,匹配電路模型和仿真結果如圖3所示。不難看出在0~20 GHz的范圍內,S11與S22幾乎均小于-20 dB。同時,由圖2與圖3中的仿真結果對比可知,匹配后S11與S22小于-20 dB頻帶寬度是匹配前的4倍,同時S21也改善了許多。因此,此匹配方法從理論上是可拓寬鍵合絲截止頻率的。

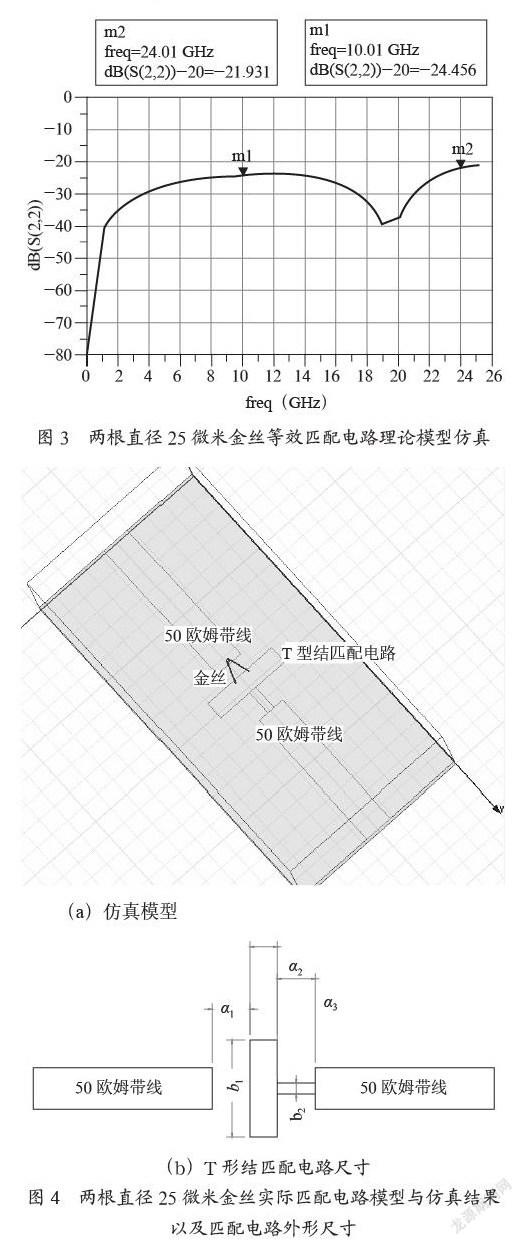

更進一步,為了更接近實際電路,將根據圖3的等效匹配原理圖,用微帶電路對鍵合絲進行匹配,將圖3中的等效電感替換為與實際對應的鍵合金絲,LC匹配電路用微帶匹配電路來實現,微帶匹配電路選用厚度為10 mil的電路板。然后將金絲與其微帶匹配電路的初始值代入軟件中仿真。圖4為實際匹配電路仿真模型與仿真結果(其中:a1=0.4,a2=0.5,a3=1.1,b1=2.1,b2=0.4,單位:mm),由仿真結果可知:在0~20 GHz的范圍內,S11與S22均小于-18 dB。同時,由仿真結果對比可知實際鍵合金絲匹配電路仿真結果與理論分析仿真結果基本保持一致。圖4(b)為匹配電路外形尺寸(由于金絲匹配電路的外形像字母“T”,故將其稱為T形結)

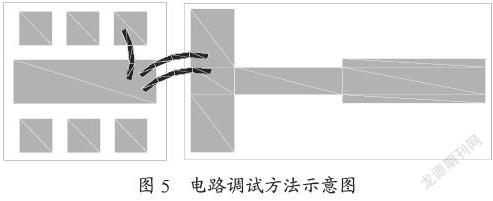

2? 微組裝工藝中電路調試方法的優化

由于材料與工藝參數的波動等原因,微波和射頻元器件都各種性能參數都有一定的波動范圍,如功率芯片,其不同只之間的增益會波動,輸出功率也會有一定范圍的上下浮動,不同批次間的變化可能會更大。但對最終的微波和射頻的組件或者電子系統,我們往往希望其性能基本保持穩定,不同批次間差異不能太大。另外,由于仿真精度及加工精度等影響,設計值與實際使用的各參數往往有一定的差異,為此,在產品裝配完成后,一般都需要進行調試工作。特別是首次生產的產品。

電路調試的基本思路是找到影響電路性能的敏感點,通過改變電路在某處敏感點的傳輸特性,進而改變電路的匹配特性。以前比較常用的方法是切割傳輸帶線或者在傳輸帶線旁邊粘接銅皮或者其他材料,這樣可以改變此處的傳輸特性。

但這種調試方法有很多弊端,如一次與一次的調試都有區別,無法達到每次調試都比較接近。另外,由于粘接金屬材料風險很高,很多場合為了保證較高的可靠性已禁止此種調試方法。

所以,在電路設計的初期,通過電路仿真及其他途徑確定電路的敏感點,然后在后期電路制作加工前,在敏感點附加增加一些合適的方形的獨立調試小塊。小塊大小需要考慮工作頻率及工藝對鍵合壓點的限制。在需要時,可以通過鍵合連接的方式連接這些調試的小塊,用于改變電路的傳輸特性,進而改善端口特性。此方法簡單、高效。可以降低電路設計的成本,提高產品的成品率。

3? 結? 論

本文介紹了一種可以改善鍵合絲截止頻率的電路結構,解決了由多芯片組成的射頻和微波電子系統與器件組件中,采用鍵合線互相連接電路常常要遇到的問題。這種電路設計方法可成倍改善微波芯片端口鍵合絲的截止頻率。另外,在工藝裝配過程中,由于工藝設備的要求以及工藝人員對可靠性等方面的追求,工藝要求中往往對鍵合線長度有嚴格的控制,采用文中的設計方法可以非常顯著的提高采用鍵合線互相連接電路的頻率響應特性,很好的改善端口性能。

同時提供了一種微波電路的調試方法,通過在鍵合絲互相連接芯片及其他電路的附近設計若干合適大小的方形的獨立帶線,需要時,在工藝上可采用鍵合的方法連接,此種調試的方法適合于采用微組裝工藝組裝的多種電路形式,工藝操作簡單,可靠性高。

由于此T形匹配結構簡單,便于設計和應用。所以,此T形結匹配方式可大量使用在微波多芯片模塊中,這將會極大的改善多芯片模塊電路性能,減小調試量;更重要的是,由于T形結的匹配方式在保證電性能的同時,可使管芯和帶線間的間隙盡可能的大。這將極大的降低裝配和鍵合難度,從而提高生產效率。因此,T形結匹配電路在微波多芯片模塊中具有很強的實用價值,值得廣泛推廣和應用。

參考文獻:

[1] HASSAINE N,CONCILIO F. Modeling and high frequency characterization of short links for high performance integrated circuits. Experimental validation and CAD formulas [C]//Proceedings of the 2003 SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference-IMOC 2003.(Cat.No.03TH8678).Foz do Iguacu:IEEE,2003:507-512.

[2] MEI S,ISMAIL Y I. Modeling skin and proximity effects with reduced realizable RL circuits [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2004,12(4):437-447.

[3] YANG S Y,XIANG D W,BRYANT A,et al. Condition Monitoring for Device Reliability in Power Electronic Converters:A Review [J].IEEE Transactions on Power Electronics,2010,25(11):2734-2752.

[4] ZHANG Z R,GAO J C,FLOWERS G T,et al. The Impact of Connection Failure of Bonding Wire on Signal Transmission in Radio Frequency Circuits [J].IEEE Transactions on Components,Packaging and Manufacturing Technology,2020,10(10):1729-1737.

[5] PEDERSEN K B,KRISTENSEN P K,POPOK V,et al.Degradation Assessment in IGBT Modules Using Four-Point Probing Approach [J].IEEE Transactions on Power Electronics,2015,30(5):2405-2412.

作者簡介:羅建(1981—),男,漢族,四川眉山人,工程師,碩士研究生,研究方向:3D-SIP及微系統。