基于FPGA的數字式鎖定放大器設計

楊晨曦

(電子科技大學 電子科學與工程學院,四川成都,611731)

0 引言

在實際工程中,常常需要進行微弱信號的檢測。而本數字式鎖定放大器采用相關檢測法實現了數字相敏的檢波,通過噪聲信號和確定性信號的相關特性實現有用信號的提取。一般情況下,有用信號在時域上不同時刻的取值具有相關性,而比如熱噪聲之類的干擾噪聲具有隨機性,因此,可以利用這一特性差異,區分出有用信號與干擾噪聲[1-2]。

1 數字相敏檢波

■1.1 數字相敏檢波特點

采用數字相敏檢波,可以方便進行低頻信號的檢測。在模擬式相敏檢測器中,當參考信號頻率很低時,相敏檢波器的Q值會嚴重下降,而數字相敏檢波不會,而且由于數字信號處理的特性,使得數字相敏檢波有很高的線性度。且由于FPGA代碼便于修改,可以對工作頻率、時間常數、靈敏度等參數進行靈活控制,使得數字相敏檢波有很好的靈活性[2]。

■1.2 數字相敏檢波原理

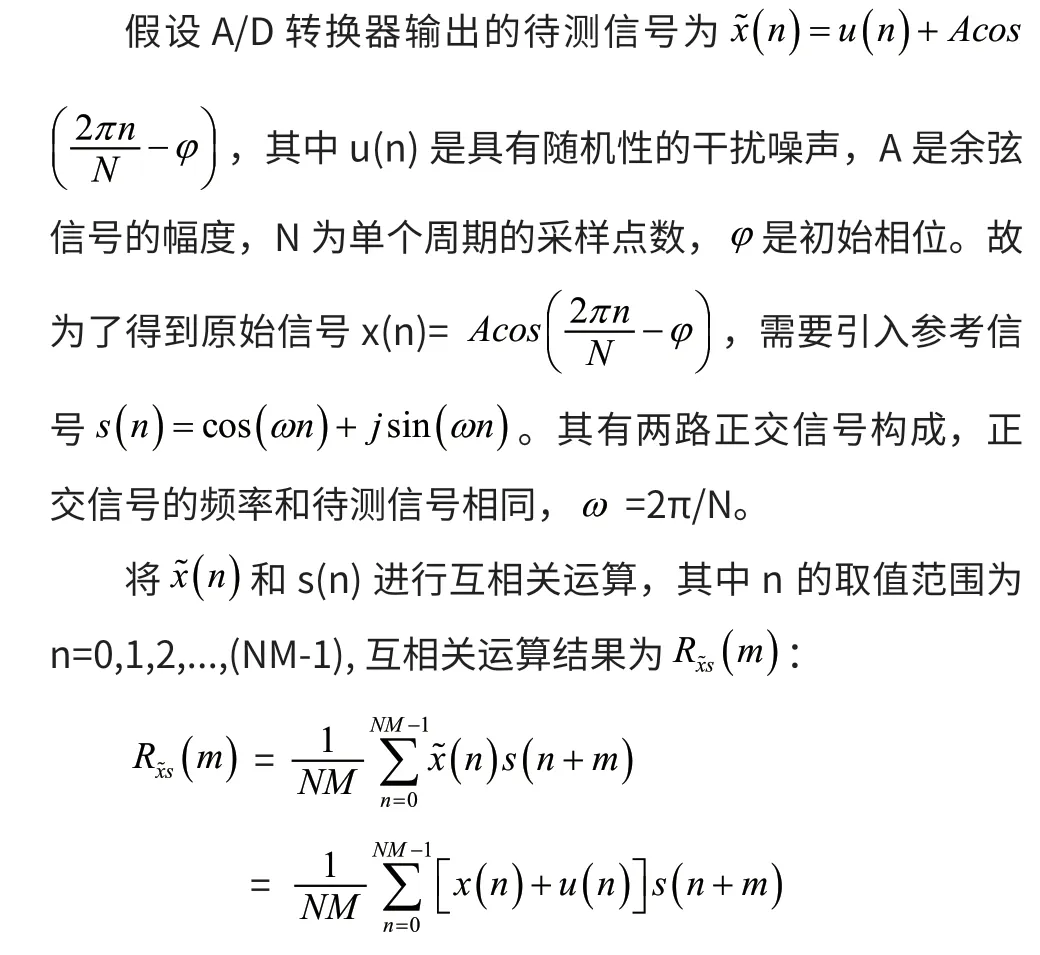

綜上,數字相敏檢波可以很好的抑制隨機噪聲的干擾,提取出微弱的有用信號,并且使用起來比模擬相敏檢波更加的靈活方便[3]。數字相敏檢波的原理如圖1所示。

圖1 數字相敏檢波原理圖

2 數字式鎖定放大器設計

■2.1 數字式鎖定放大器框架

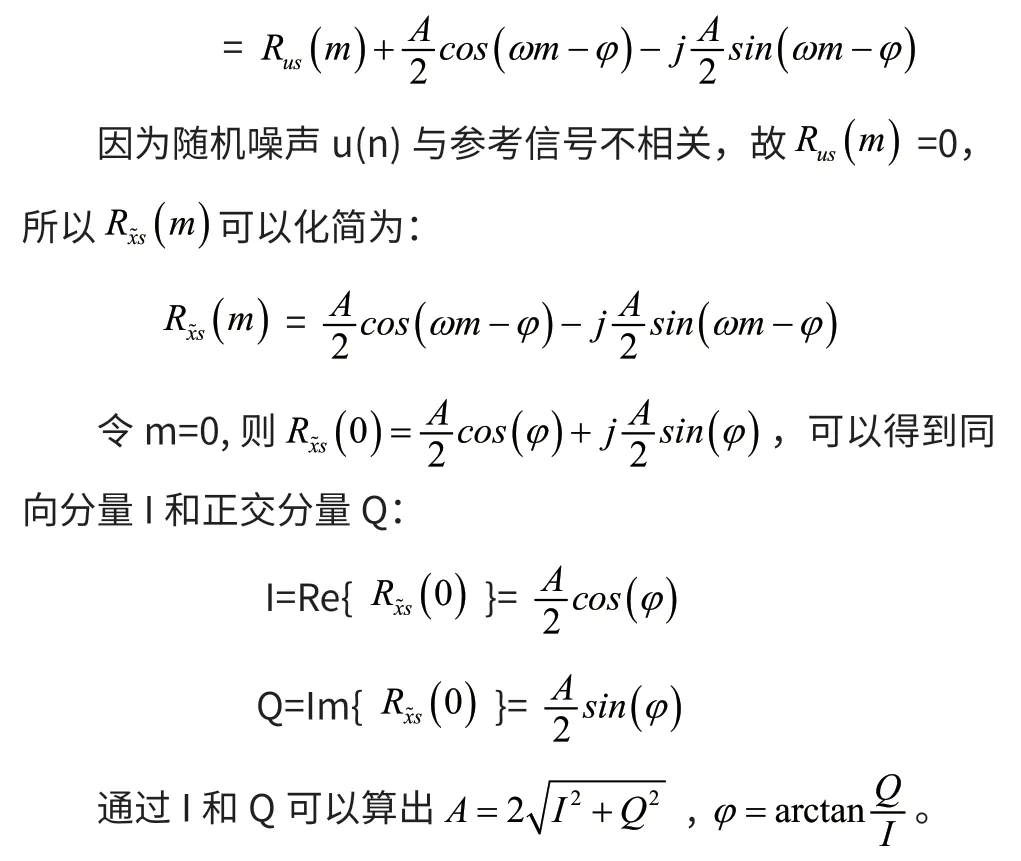

在設計中采用ADS8320作為A/D轉換器,50MHz外部晶振作為系統時鐘,以12.8kHz的采樣頻率對200Hz的正弦信號進行采樣,即每個正弦周期采樣64個點。正弦待測信號和參考信號通過直接數字頻率合成器(DDS)芯片AD9958生成。

數字式鎖定放大器的系統框圖如圖2所示。FPGA內部有分頻模塊、數據采集控制模塊、DDS控制模塊和數據處理模塊四個部分組成。系統工作流程為FPGA通過DDS控制模塊對AD9958進行控制,使其產生兩路正交的正弦信號,一路正弦信號經過會引入隨機噪聲的路徑后到達A/D轉換芯片,進行數字化處理,另外原始的兩路正交的正弦信號直接送入A/D芯片。隨后FPGA采集控制模塊控制A/D芯片進行數據的接收,并將接收到的數據送入數據處理模塊進行相乘、累加等數據運算,最終求出幅值和相位并進行輸出。

圖2 數字式鎖定放大器系統框圖

■ 2.2 分頻模塊設計

在FPGA開發中,時鐘設計是時序電路非常重要的一部分。在本設計中FPGA芯片所使用的時鐘是由外部晶振提供的50MHz的時鐘。分頻模塊先調用PLL的IP核分出一個32MHz的主時鐘,該時鐘主要是用于后續數據處理模塊的乘法、開方和反三角函數的計算。同時該時鐘還可以很方便的通過計數的方式進行分頻,產生用于控制DDS芯片的2MHz時鐘和用于A/D轉換芯片采樣的320kHz的時鐘。該設計共使用了4種頻率的同步時鐘,并不存在跨時鐘域數據傳輸,整體時鐘結構比較簡單。

■ 2.3 數據采集控制模塊設計

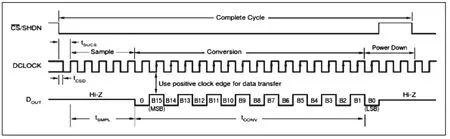

數據采集模塊的功能主要是通過SPI協議與ADS8320進行通信,由分頻模塊為ADS8320提供320kHz的采樣時鐘,每25個時鐘將CS管腳(片選)拉低21個時鐘。在CS剛被拉低的前5個時鐘,DOUT處于高阻態,隨后輸出一個時鐘周期的低電平信號作為輸出轉換結果開始的標志,接下來的16個時鐘由高到低的輸出16位的轉化結果。之后將CS端拉高,停止轉換。AD轉換器通過SPI協議輸出的數據由移位寄存器接收并進行串并轉換。控制時序如圖3所示。

圖3 ADS8320控制時序圖

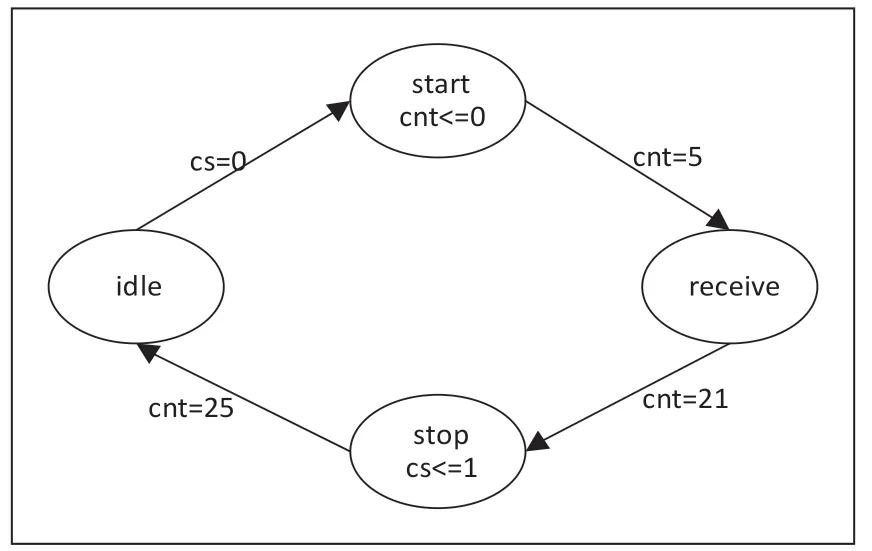

得到的數據送入數據處理模塊,實現幅值和相位的檢波運算。整體的數據采集控制模塊采用狀態機進行設計。狀態機有idle、start、receive、stop四個狀態,通過計數器控制狀態的轉移,在idle狀態發現片選信號有效時,進入start狀態,將計數器清零。計數器計數5個時鐘后進入receive狀態,開始接收數據。數據接收完成,計數器計數到21,進入stop狀態,停止采集數據,將片選信號撤銷。計數到25后重新開始一輪數據采集。狀態轉移圖如圖4所示。

圖4 數據采集模塊狀態轉移圖

■ 2.4 DDS控制模塊設計

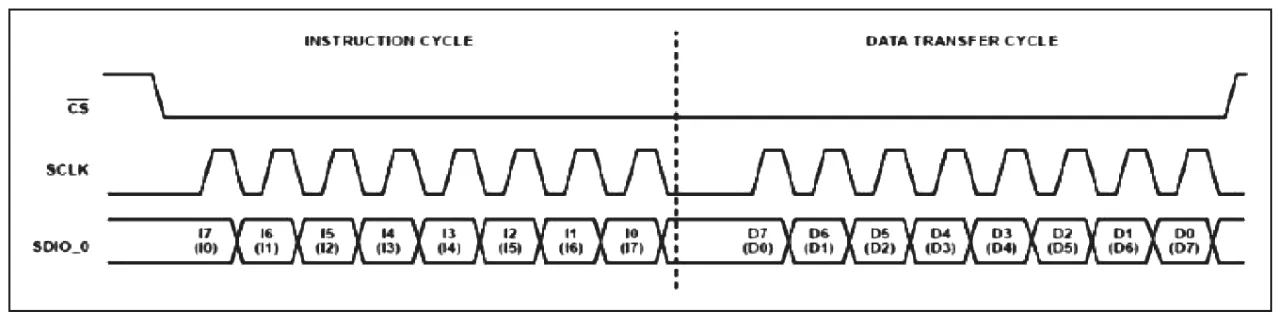

DDS控制模塊的功能是通過SPI協議對DDS芯片的片內寄存器進行配置,從而實現指定頻率正弦波的產生。AD9958內部擁有10個寄存器,分別對應著不同的地址,這些寄存器為:通道選擇寄存器CSR、線性掃描斜率LSRR、LSR上升增量RDW和LSR下降增量FDW、功能寄存器FR1和FR2、通道寄存器CFR、通道頻率調整字CFTW0、通道相位偏移字CPOW0、幅度控制字ACR[4]。本模塊采用單bit串行模式進行數據寫入,實現對AD9958片內寄存器的配置。控制時序圖如圖5所示。每次傳輸16bit的數據,其中前8bit是指令周期,其中I7決定數據的讀寫模式,I0-I4是寄存器的地址,后8bit是寄存器中的數據。

圖5 AD9958串行寫入時序圖

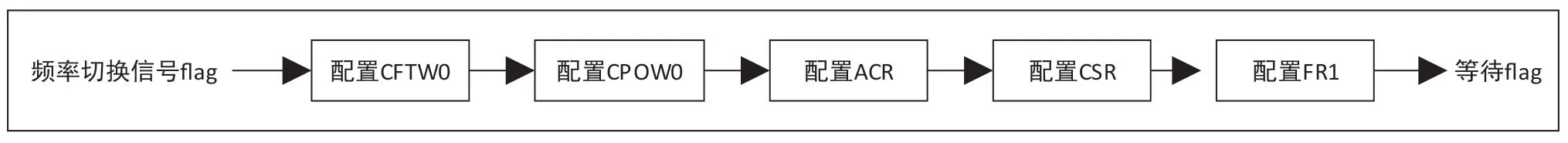

DDS控制模塊通過控制CFTW0可以設置通道的頻率參數,控制ACR可以對輸出信號的電壓幅度參數進行設置,控制CPOW0設置相位偏移參數,相位偏移字有14位精度可以調節,分辨率為控制CSR設置SPI的指令控制的具體通道是哪個,控制FR1設置PLL的分頻系數和VCO增益等等。每次進行頻率的切換都需要對這些寄存器重新進行配置。DDS控制模塊流程如圖6所示。

圖6 DDS控制模塊工作流程

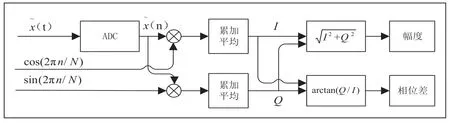

■ 2.5 數據處理模塊設計

數據處理模塊主要是對采集到的數字信號進行計算,首先從數據采集模塊的移位寄存器中將同步采集到的兩組數據讀到乘法器的輸入寄存器中,對其進行相乘后送入累加寄存器進行累加。當每個正弦信號的64個采樣點的數據相乘累加結束后,通過截位進行平均操作,將低6位的數據直接舍棄,這樣做雖然會喪失一點精度,但是避免了使用除法器,節省了運算時間和邏輯資源。截位得到的數據就是數字相敏檢波算法中的同向分量I和正交分量Q。然后計算對應的就得到了待測信號的幅值和相位。數據處理流程圖如圖7所示。

圖7 數據處理流程圖

數據處理模塊所涉及到的乘法器、開平方根和反三角函數登運算,都是通過調用ise工具提供的IP核實現的,在進行FPGA開發的時候,調用成熟的IP核可以大大縮短程序開發的時間,同時還可以獲得更好的性能。

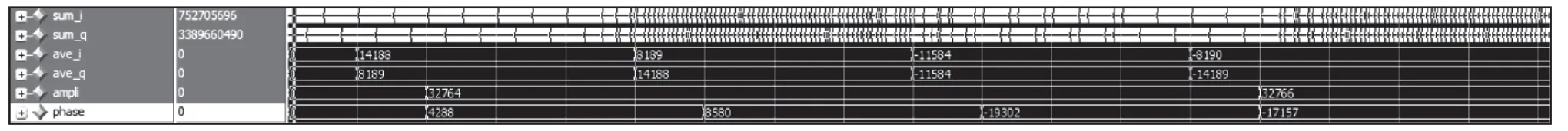

為了對基于FPGA實現的數字相敏檢波模塊進行仿真分析,我編寫一個DDS模塊,用來生成頻率為200Hz的正弦信號,輸出的結果加上隨機噪聲來模擬待測信號,同時生成兩路正交的余弦信號作為參考信號,送入數據處理模塊,改變待測信號的幅值和相位參數,觀察輸出的結果與設置參數的區別,仿真的截圖如圖8所示,最終仿真數據如表1所示。

圖8 數字相敏檢波時序仿真圖

表1 仿真數據

3 結語

本文設計了一款基于FPGA的數字式鎖定放大器,該系統能夠實現對200Hz的低頻信號進行檢波,由于A/D轉換芯片采樣率的限制,可以通過改變DDS控制模塊的程序參數實現最高約100kHz的信號幅相檢測。通過對FPGA程序進行仿真發現數字相敏檢波算法可以達到預期目標,相信FPGA在微弱信號檢測領域會發揮越來越大的作用。